Изобретение относится к радиотехнике и может быть использовано в системах фазовой автоподстройки частоты.

Цель изобретения - сокращение времени перехода в режим сравнения фаз из режима сравнения частот.

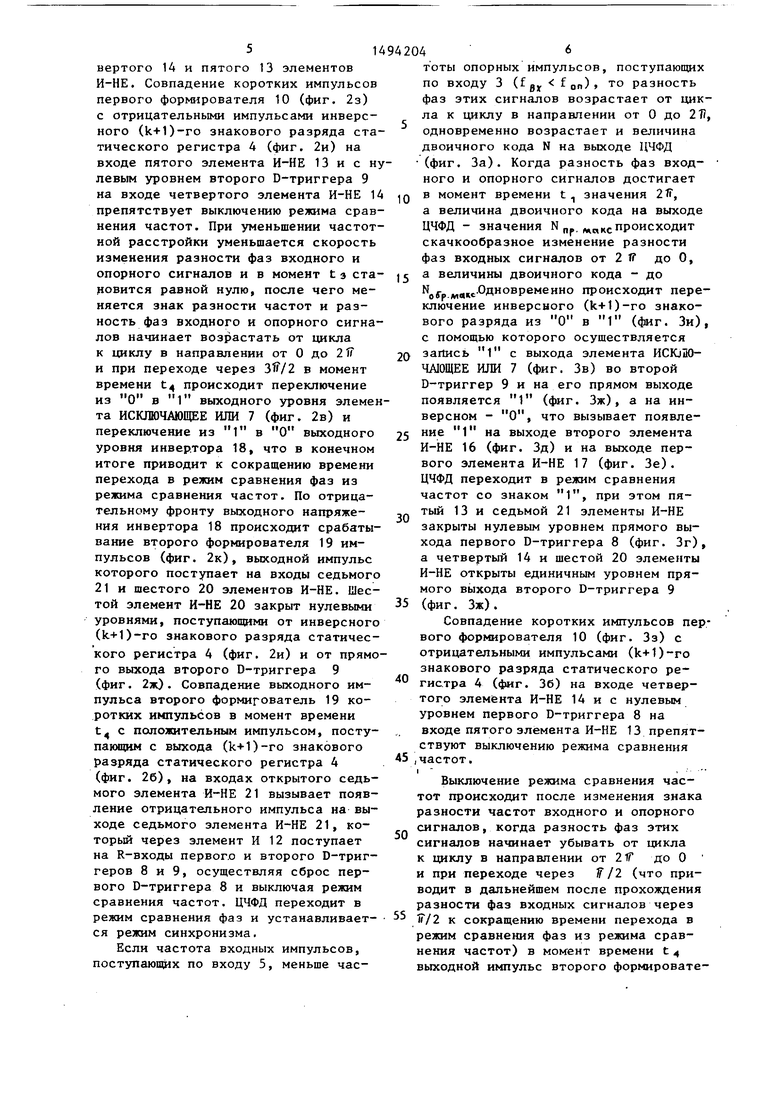

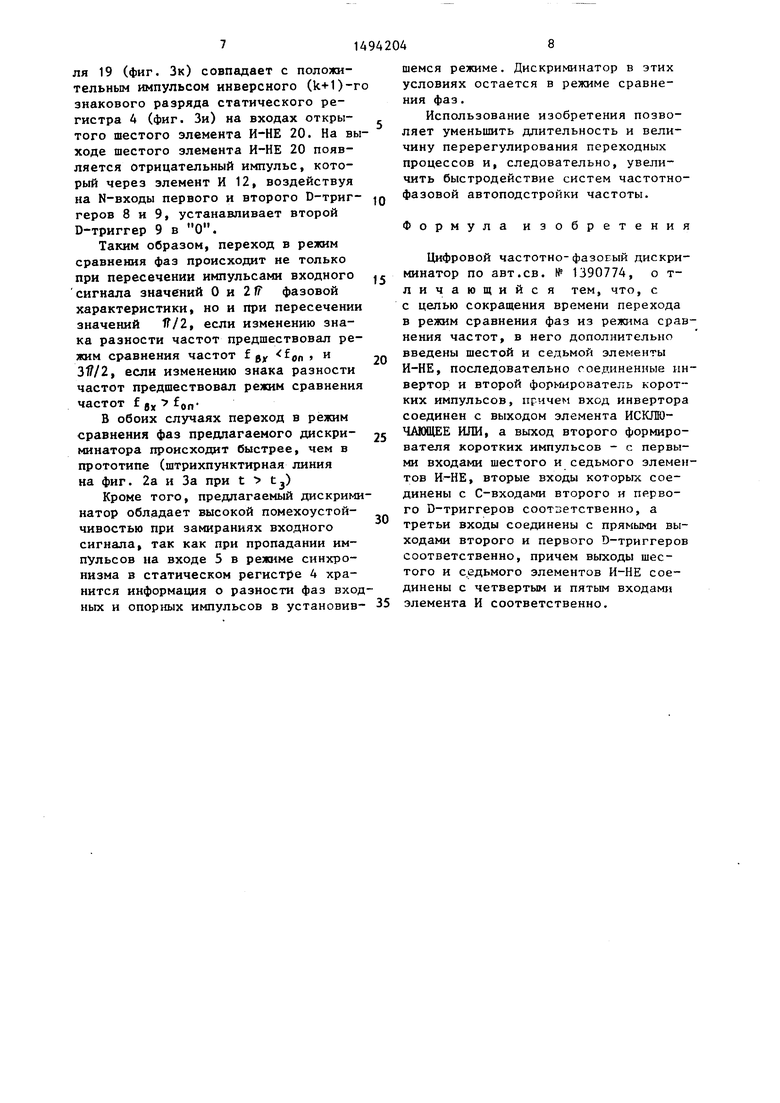

На фиг. 1 представлена структурная электрическая схема цифрового частотно-фазового дискриминатора; на фиг. 2 и 3 - временные диаграммы поясняющие его работу.

Цифровой частотно-фазовый дискриминатор (ЦИФД) содержит счетчик 1, вход 2 счетных импульсов, вход 3 опорных импульсов, статический регистр 4, сигнальный вход 5, блок 6 запрета, элемент ИСЮБОЧАЮЩЕЕ ИЛИ 7, первый 8 и второй 9 D-триггеры, первый формирователь 10 коротких импульсов, элемент ИЛИ 11, элемент И 1 пятый 13, четвертый 14, третий 15, второй 16 и первый 17 элементы И-НЕ инвертор 18, второй формирователь 19 коротких импульсов и шестой 20 и седьмой 21 элемент И-НЕ 20, 21.

Цифровой частотно-фазовый дискри- шнaтop работает следующим образом.

Опорными импульсами, поступающими от входа 3 на установки О счетчика 1, на выходах последнего устанавливаются О. На счетный вход Т счетчика 1 по входу 2 поступают счетные импульсы. При этом частота счетных импульсов определяется выражением:

сч

N

где 2

-1 - емкость счетчика 1, Т - период опорных импульсов .

В MOM.JHT прихода по входу 5 входного импульса на вход статического регистра 4 информация из счетчика 1 записывается в статический регистр 4, таким образом на выходе этого регист}1а формируепся двоичный код, величина N которого пропорциональна разности фаз входного и опорного импульсов.

Если частота входных импульсов, поступающих по входу 5 больше частоты опорных импульсов, поступающих по входу 3 (f J, 7 f of,) , то разность фаз этих сигналов убывает от цикла к циклу в направлении от 2 ff -до О, одновременно убывает и величина дво

0

5

0

5

0

5

0

5

ичного кода N на выходе гшфрового частотно-фазового дискриминатора (фиг. 2а) .

Когда разность фаз входного и опорного сигналов достигает в момент времени t значения О, а величина двоичного кода на выходе цифрового частотно-фазового дискриминатора - значения акспроисходит скачкообразное изменение разности фаз входных сигналов от О до 2, а величины двоичного кода - до N pp. „пкс Одновременно происходит переключение (k+1)-ro знакового разряда статического регистра 4 из О в 1 (фиг. 2б), с помощью которого осуществляется запись 1 с выхода элемента ИСКЛЮЧ ШЦЕЕ ИЛИ 7 (фиг. 2в) в первый D-триггер 8. На прямом выходе этого D-триггера появляется 1 (фиг. 2г), а на инверсном - О, что вызывает появление 1 на выходе второго элемента И-НЕ 16 (фиг. 2д) , т.е. в старшем значащем разряде выходного кода цифрового частотно- фазового дискриминатора. Эта 1 отключая младщие значащие разряды выходного кода ЦЧФД, поступающие через блок 6 запрета, а также вызывает появление 1 на выходе элемента ИЛИ 11. На выходе первого элемента

И-НЕ 17, т.е. в знаковом разряде выходного кода ЦЧФД, установится О (фиг. 2е). ЦЧФД переходит в режим сравнения частот со знаком О, при этом четвертый 14 и шестой 20 элементы И-НЕ закрыты нулевым уровнем прямого выхода второго U-триггера 9 (фиг. 2ж), а пятый 13 и седьмой 21 элементы И-НЕ открыты единичным уровнем прямого выхода первого D-триггера 8 (фиг. 2г).

В режиме сравнении частот t , ; t t 3 уменьшается скорость изменения двоичного кода на выходе статического регистра 4 (пунктирная линия на фиг. 2а), а следовательно, уменьшается скорость изменения разности фаз входного и опорного сигналов. При переходе разности фаз входного и опорного сигналов значения в момент ti происходит переключение из 1 в О выходного уровня элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 (фиг. 2в) и импульс с выхода первого формирователя 10 коротких импульсов (фиг. 2з), работающего по отрицательному фронту, поступает на входы четвертого 14 и пятого 13 элементов И-НЕ. Совпадение коротких импульсов первого форкирователя 10 (фиг. 2з) с отрицательными импульсами инверсного (k+1)-ro знакового разряда статического регистра 4 (фиг. 2и) на входе пятого элемента И-НЕ 13 и с нулевым уровнем второго D-триггера 9 на входе четвертого элемента И-НЕ 14 препятствует выключению режима сравнения частот. При уменьшении частотной расстройки уменьшается скорость изменения разности фаз входного и опорного сигналов и в момент t 3 становится равной нулю, после чего меняется знак разности частот и разность фаз входного и опорного сигналов начинает возрастать от цикла к циклу в направлении от О до 2 ff и при переходе через 3lf/2 в момент времени t4 происходит переключение из О в 1 выходного уровня элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 (фиг. 2в) и переключение из 1 в О выходного уровня инвертора 18, что в конечном итоге приводит к сокрашению времени перехода в режим сравнения фаз из режима сравнения частот. По отрицательному фронту выходного напряжения инвертора 18 происходит срабатывание второго формирователя 19 импульсов (фиг. 2к), выходной импульс которого поступает на входы седьмого 21 и шестого 20 элементов И-НЕ. Шестой элемент И-НЕ 20 закрыт нулевыми уровнями, поступающими от инверсного (k+1)-ro знакового разряда статического регистра 4 (фиг. 2и) и от прямого выхода второго D-триггера 9 (фиг. 2ж). Совпадение выходного импульса второго формирователь 19 коротких импульсов в момент времени t с положительным импульсом, поступающим с выхода (k+1)-ro знакового разряда статического регистра 4 (фиг. 2б), на входах открытого седьмого элемента И-НЕ 21 вызывает появление отрицательного импульса на выходе седьмого элемента И-НЕ 21, ко- торьй через элемент И 12 поступает на R-входы первого и второго D-триг- геров 8 и 9, осуществляя сброс первого D-триггера 8 и выключая режим сравнения частот. ЦЧФД переходит в режим сравнения фаз и устанавливается режим синхронизма.

Если частота входных импульсов, поступающих по входу 5, меньше час0

5

0

5

0

тоты опорных импульсов, поступающих по входу 3 () то разность фаз этих сигналов возрастает от цикла к циклу в направлении от О до 21, одновременно возрастает и величина двоичного кода N на выходе ЦЧФД (фиг. За). Когда разность фаз входного и опорного сигналов достигает в момент времени t значения 21f, а величина двоичного кода на выходе ЦЧФД - значения N „р, „ксПР° сходит скачкообразное изменение разности фаз входных сигналов от 2 ff до О,

5 а величины двоичного кода - до

. .Одновременно происходит переключение инверсного (k+1)-ro знакового разряда из О в 1 (фиг. Зи), с помощью которого осуществляется

Q запись 1 с выхода элемента ИСЮЗО- ЧАЮЩЕЕ ИЛИ 7 (фиг. Зв) во второй D-триггер 9 и на его прямом выходе появляется 1 (фиг. Зж), а на инверсном - О, что вызывает появление 1 на выходе второго элемента И-НЕ 16 (фиг. Зд) и на выходе первого элемента И-НЕ 17 (фиг. Зе). ЦЧФД переходит в режим сравнения частот со знаком 1, при этом пятый 13 и седьмой 21 элементы И-НЕ закрыты нулевым уровнем прямого выхода первого D-триггера 8 (фиг. Зг), а четвертый 14 и шестой 20 элементы И-НЕ открыты единичным уровнем прямого выхода второго D-триггера 9 (фиг. Зж).

Совпадение коротких импульсов первого формирователя 10 (фиг. Зз) с отрицательными импульсами ()-ro знакового разряда статического регистра 4 (фиг. 36) на входе четвертого элемента И-НЕ 14 и с нулевым уровнем первого D-триггера 8 на входе пятого элемента И-НЕ 13 препятствуют выключению режима сравнения , частот. I .

Выключение режима сравнения частот происходит после изменения знака разности частот входного и опорного сигналов, когда разность фаз этих сигналов начинает убывать от цикла к циклу в направлении от 21Г до О и при переходе через /2 (что приводит в дальнейшем после прохождения разности фаз входных сигналов через и/2 к сокращению времени перехода в режим сравнения фаз из режима сравнения частот) в момент времени 14 выходной импульс второго формировате5

0

5

ля 19 (фиг. Зк) совпадает с положительным импульсом инверсного (k+1)-r знакового разряда статического регистра 4 (фиг. Зи) на входах откры- того шестого элемента И-НЕ 20. На выходе шестого элемента И-НЕ 20 появляется отрицательный импульс, который через элемент И 12, воздействуя на N-входы первого и второго D-триг- геров 8 и 9, устанавливает второй D-триггер 9 в О.

Таким образом, переход в режим сравнения фаз происходит не только при пересечении импульсами входного сигнала значений О и 2 f фазовой характеристики, но и при пересечении значений , если изменению знака разности частот предшествовал режим сравнения частот f оп 311/2, если изменению знака разности частот предшествовал режим сравнения частот f вх опВ обоих случаях переход в режим сравнения фаз предлагаемого дискри- минатора происходит быстрее, чем в прототипе (штрихпунктирная линия на фиг. 2а и За при t t)

Кроме того, предлагаемый дискриминатор обладает высокой помехоустойчивостью при замираниях входного сигнала, так как при пропадании импульсов на входе 5 в режиме синхронизма в статическом регистре 4 хранится информация о разности фаз входных и опорных импульсов в установив-

шемся режиме. Дискриминатор в этих условиях остается в режиме сравнения фаз.

Использование изобретения позволяет уменьшить длительность и величину перерегулирования переходных процессов и, следовательно, увеличить быстродействие систем частотно- фазовой автоподстройки частоты.

Формула изобретения

Цифровой частотно-фазовый дискриминатор по авт.св. № 1390774, о т- личающийся тем, что, с с целью сокращения времени перехода в режим сравнения фаз из режима сравнения частот, в него дополнительно введены шестой и седьмой элементы И-НЕ, последовательно соединенные инвертор и второй формирователь коротких импульсов, причем вход инвертора соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход второго формирователя коротких импульсов - с первыми входами шестого и седьмого элементов И-НЕ, вторые входы которых соединены с С-входами второго и первого D-триггеров соответственно, а третьи входы соединены с прямыми выходами второго и первого D-триггеров соответственно, причем выходы шестого и с.едьмого элементов И-НЕ соединены с четвертым и пятым входами элемента И соответственно.

Affffy. твж

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотно-фазовый дискриминатор | 1986 |

|

SU1390774A2 |

| Цифровой частотно-фазовый дискриминатор | 1991 |

|

SU1826122A1 |

| Цифровой частотно-фазовый дискриминатор | 1985 |

|

SU1251289A1 |

| Цифровой частотно-фазовый дискриминатор | 1984 |

|

SU1256139A1 |

| Цифровой частотно-фазовый дискриминатор | 1982 |

|

SU1027798A1 |

| Цифровой частотно-фазовый дискриминатор | 1985 |

|

SU1363431A2 |

| Цифровой частотно-фазовый дискриминатор | 1983 |

|

SU1117824A1 |

| Способ фазовой автоподстройки частоты управляемого генератора и устройство для его осуществления | 1989 |

|

SU1788576A1 |

| Цифровой фазовый дискриминатор | 1989 |

|

SU1693713A1 |

| Способ определения знака разности частот и устройство для его реализации | 2016 |

|

RU2625054C1 |

Изобретение относится к радиотехнике. Цель изобретения - сокращение времени перехода в режим сравнения фаз из режима сравнения частот. Дискриминатор содержит счетчик 1, статический регистр 4, блок запрета 6, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, D - триггеры 8 и 9, формирователи 10 и 19 коротких импульсов, элементы ИЛИ 11, И 12, И-НЕ 13-70, 20 и 21 и инвертор 18. Из режима сравнения частот дискриминатор переходит в режим сравнения фаз и устанавливается режим синхронизма. Выключение режима сравнения частот происходит после изменения знака разности частот входного и опорного сигналов, когда разность фаз этих сигналов начинает убывать от цикла к циклу в направлении от 2φ до 0. Прохождение разности фаз входных сигналов через φ/2 приводит к сокращению времени перехода в режим сравнения фаз из режима сравнения частот. 3 ил.

/V

.

fna.

| Цифровой частотно-фазовый дискриминатор | 1986 |

|

SU1390774A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-15—Публикация

1987-07-30—Подача