(54) СПОСОБ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования дискретных сигналов | 1983 |

|

SU1136199A2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| Цифровой следящий электропривод | 1985 |

|

SU1308982A1 |

| Синтезатор частот | 1985 |

|

SU1262685A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 1995 |

|

RU2138910C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТРЕХФАЗНЫМ АСИНХРОННЫМ ДВИГАТЕЛЕМ | 2014 |

|

RU2566740C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки /ЭЛТ/ | 1989 |

|

SU1633387A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОДНОФАЗНЫМ АСИНХРОННЫМ ЭЛЕКТРОДВИГАТЕЛЕМ | 2013 |

|

RU2542717C2 |

1

Изобретение относится к технике цифровых систем передачи и может использоваться при передаче цифровых сигналов в линейных трактах, оборудованных регенераторами многоуровневых сигналов.

Известен способ преобразования двоичного сигнала в квазитроичный балансный сигнал и устройство для его реализации, в котором баланс-,Q ный многоуровневый сигнал получается путем преобразования исходного дв 1чного сигнала в балансный трехуровневый сигнал

Недостатком данного способа и 15 реализующего его устройства является ограниченная область применения, поскольку они предназначены только на формирование квазитройчных балансных сигналов.20

Наиболее близким по технической сущности к предлагаемому является способ преобразования дискретных сигналов, заключающийся в том, что

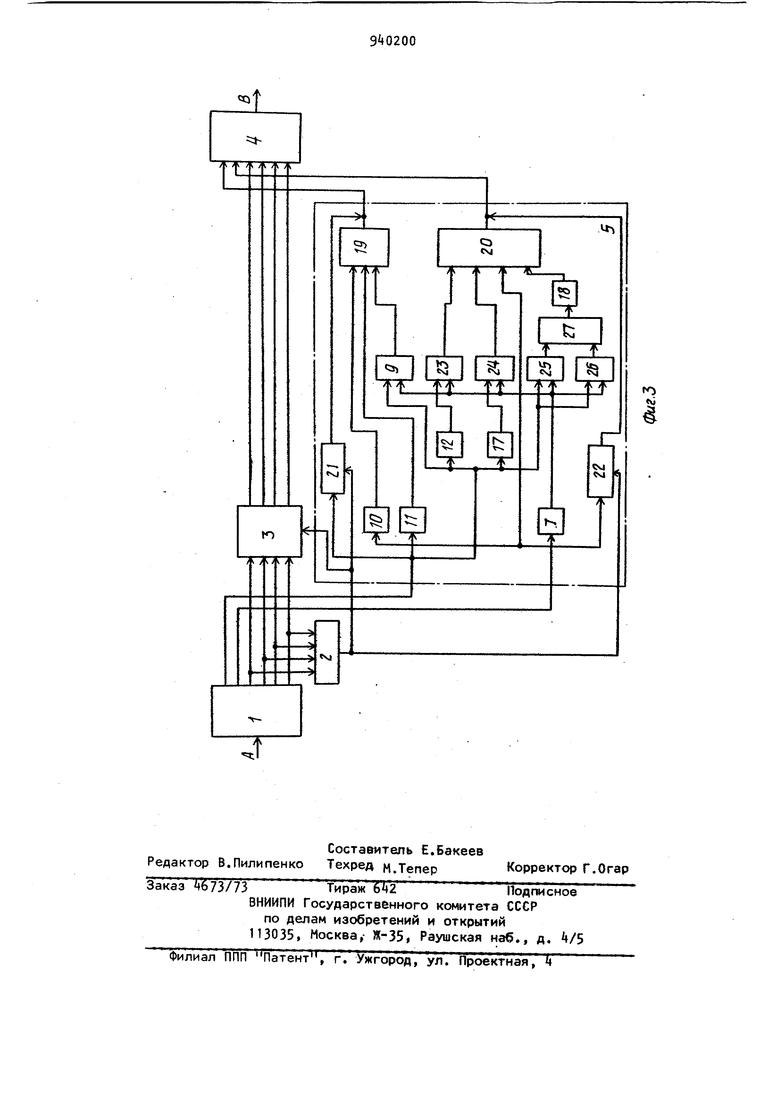

из последовательности дискретных од сполярных сигналов формируют последовательности многоуровневых биполярных импульсов и устройство для преобразования дискретных сигналов, содержащее преобразователь двоичного сигнала в биполярный сигнал, старшие выходы которого подключены к соответствующим входам анализатора веса и к первым входам конвертора полярности импульсов, выходы которого соединены с соответствующими первыми входами мультиплексора, выход последнего подключен к выходу устройства, младшие разряды преобразователя дискретного сигнала в биполярный сигнал подключены к соответствующим информационным входам логического переключателя, выход анализатора веса соединен с управляющими входами логического переключателя, первый выход которого подключен к управляющему входу конвертора полярности импульсов, второй и третий выходы 39 логического переключателя создинены с вторыми входами мультиплексора 2 Недостатком известного способа и реализующего его устройства является низкая помехоустойчивость и низкая информативность. Цель изобретения - повышение помехоуст 1чивости и информативности. Поставленная цель достигается тем, что в способе преобразования ди кретных сигналов,заключающемся в том, что из последовательности дискретных однополярных сигналов формируют последовательности многоуровневых биполярных сигналов, в которых сравнивают каждый импульс каждой кодовой последовательности, кроме первого и втopoгo с заданным значением, при превышении которого изменяют на противоположную полярность четные импульсы каждой кодовой последовательности, кроме второго импульса, в противном случае заменяют первый и второй импульсы каждой последовательности на соответствующие комбинации многоуровневых импульсов. В устройство для преобразования дискретных сигналов, содержащее преобразователь двоичного сигнала в биполярный сигнал, старшие выхо- ды которого подключены к соответству ющим входам анализатора веса и к первым входам конвертора полярности импульсов, выходы которого соединены с соответствующими первыми входами мультиплексора, выход последнего под ключен к выходу .устройства, младшие разряды преобразователя двоичного сигнала в биполярный сигнал подключены к соответствующим информационным входам логического переключателя 1 выход анализатора веса соединен с управляющими входами логического пер ключателя , первый выход которого под ключен к управляющему входу конвертора полярности импульсов, второй и третий выходы логического переключателя соединены с вторыми входами мультиплексора, введены сумматоры, логический переключатель выполнен на выпрямителе, ограничителе, ключах, элементах И, ИЛИ, инверторах, генераторе, первый информационный вход логического переключателя соединен с входом первого ключа, с первым вхо дом первого элемента ИЛИ, с первым входом четвертого элемента И и через второй инвертор - с первым входом третьего элемента И, первый выход пе вого ключа соединен с первым управляющим входом и с первым выходом логического переключателя, второй выход первого ключа подключен к второму выходу логического переключателя, второй информационный вход логического переключателя соединен через ограничитель с вторым входом первого элемента ИЛИ и через выпрямитель - с первым входом третьего инвертора, выход которого подключен к второму входу третьего элемента И, выход генератора соединен с вторым входом третьего инвертора и с первыми входами первого и второго элементов И, выход первого элемента И подключен к первому информационному выходу логического переключателя, выход второго элемента И через четвертый инвертор соединен с вторым информационным выходом логического переключателя, выход первого элемента ИЛИ подключен к второму входу первого элемента И и через первый инвертор - к второму входу второго элемента И, выход третьего инвертора соединен с вторыми входами третьего и четвертого элементов И, выход третьего элемента И - непосредственно, а выход четвертого элемента И через пятый инвертор соединен с третьими информационными выходами логического переключателя, выходы первого и второго ключей подключены соответственно к первому и второму управлякщим выходам логического пepeFcлючaтeля, первый и второй информационные выходы которого соединены соответственно с входами первого и второго сумматоров, первый и второй управляющие выходы логического переключателя соединены соответственно с выходами первого и второго сумматоров, которые подключены к соответствующим вторым входам мультиплексора. Яогический перекл очатель выполнен на ключах, инверторах, выпрямителе, элементах ИЛИ и на третьем сумматоре, первый информационный вход логического переключателя соединен через второй инвертор с первым информационным выходом логического переключателя, с первым входом первого ключа, с первыми входами первого, четвертого и пятого элементов ИЛИ и через третий и четвертый инверторы подключены соответственно к первым входам второго и третьего элемен- i тов ИЛИ, второй информационный вход логического переключателя соединен с первым входом второго ключа, с третьим информационным выходом логического, переключателя и через выпрямитель - с вторыми входами пер вого, второго, третьего, четвертого и пятого элементов ИЛИ и через первый инвертор - с первым информационным выходом логического переключателя, выход первого элемента ИЛИ подключен к третьему выходу логического переключателя, первый управляющий вход логического переключателя подключен к второму входу пе вого ключа и к первому управляющему выходу логического переключателя выходы второго и третьего элементо ИЛИ соединены с первым и вторым информационными выходами логического переключателя, выходы четвертого и пятого элементов ИЛИ подключены к входам третьего сумматора, выход которого через пятый инвертор соеди нен с третьим информационным выходом логического переключателя. На фиг. I представлена обобщенная схема устройства для осуществления спо соба; на фиг.2 и 3 - варианты устройства с различным преобразованием. Устройство содержит (фиг. 1) преобразователь 1 последовательного двоичного сигнала в биполярный сигнал, анализатор 2 веса, инвертор 3 полярности импульсов, мультиплексор Ц и логический переключатель 5. Для пояснения последовательности способа рассмотрим работу обс щенной схемы устройства (фиг. 1). На вход преобразователя t подается исходный дискретный сигнал с тактовой частотой FA . Преобразователь работает по правилу перевода числа из двоичной системы счисления в систему счисления с основанием М 2 при этом И двоичных импульсов заменяются на К М-уровневых (), а об щая тактовая частота сигнала снижается в п/К раз. На выходах преобразователя 1 формируется К-разрядное М-уровневое параллельное кодово слово из множества разрешенных кодо вых слов. В анализаторе 2 веса вычи ляется алгебраическая сумма значений импульсов всех разрядов, кроме первого и второго. Если вычисленное значение превышает по абсолютной величине порог } const, то анализатор 2 веса вырабатывает управляющий сигнал, который btRJiJOMaeT 0 логический переключатель 5 и включает конвертор 3 полярности импульсов. В конверторе 3 полярности импульсов, принцип работы которого такой же, как и в прототипе, осуществляется изменение полярности импульсов в четных разрядах, кроме второго, что уменьшает небаланс в кодовом слове. Логическийпереключатель 5 при этом отключен и импульсы первого и второго разряда подаются на мультиплексор Ц без изменения, последний осуществляет перевод параллельного многоуровневого балансного сигнала в последовательный линейный сигнал с тактовой частотой Рд . Если же алгебраическая сумма Wj,| const, то на выходе анализатора 2 веса управляющий сигнал отсутствует, конвертор 3 полярности импульсов отключается и импульсы всех разрядов, кроме первого и рторого подаются на мультиплексор k без изменения. В логическом переключателе 5 осуществляется замена импульсов первого и второго разрядов новыми комбинациями импульсов, которыми начинаются избыточные кодовые Слова, Сформированное таким образом параллельное многоуровневое балансное кодовое слово преобразуется в мультиплексоре в последовательный линейный сигнал с тактовой частотой % К/п-Гд (). Для сохранения однозначности декодирования на приеме в схему декодера также вводится логический переключатель, который оценивают импульсы первого и второго разрядов Если принятое кодовое слово принадлежит к числу избыточных, то в лot гическом переключателе осуществляется амена импульсов первого и второго разрядов,обратная замене, осущественной на передаче. В противном лучае импульсы первого и второго азрядов не изменяются, а изменяютя полярности импульсов в четных азрядах кодового слова. Таким образом, в результате пребразования в сформированном многоровневом сигнале отсутствуют кодовые лова с большим весом,,устраняется одовое слово, состоящее из одних улей, существует возможность конроля достоверности передачи на приме, повышается плотность импульсов кодовом слове. Поскольку баланс кодовом слове достигается без введения дополнительных балансных импульсов, то повышается эффективност преобразования, снижается тактовая частота линейного сигнала, .что приводит к повышению помехоустойчивост и скорости передачи информации. Предлагаемый способ можно исполь зовать при формировании балансного линейного сигнала с любым числом уро ней (), при наличии избыточности преобразования. На фиг. 2 приведена схема устройства, реализующего предлагаемый способ при преобразовании восьми двоичных символов () в шесть троичных (, ). Выбор преобразования вида 8В-6Т осуществлен по следующим соображениям. Преобразование обладает достаточной избыточностью ,85. Тактовая частота линейного сигнала снижается в 1,33 раза, что позволяет повысить эффективность цифровых систем передачи на 33%. Устройство (фиг. 2 и 3) содержит преобразователь 1 двоичных сигналов в биполярные сигналы, анализатор 2 веса, конвертор 3 полярности импульсов, мультиплексор , логический переключатель 5, ограничитель 6, выпрямитель 7 генератор 8, элемент ИЛИ 9, первый, второй и третий инверторы 10-12, первый, второй, третий и четвертьЛ элементы И 13-16, четвертый и пятый инверторы 17 и 18, первый и второй сумматоры 19 и 20, первый и второй ключи 21 и 22, элементы ИЛИ 23-26 и третий сумматор 27. Устройство работает следующим образом. Преобразователь 1 преобразует восьмиразрядный двоичный сигнал А с тактовой частотой Рд в параллельный шестиразрядный небалаИсный трехуровневый сигнал с общей тактовой частотой Fg Преобразование осуществляется по правилу перевода числа из двоичной системы счисления в троичную. Анализатор 2 веса определяет алгебраическую сумму импульсов 3, , 5 и6, разрядов, а мультиплексор 4 осуществляет перевод параллельного балансного сигнала в последовательный. Принцип работы пре образователя 1, анализатора 2 веса, мультиплексора такой же, как и в , устройстве-прототипе. 008 Пусть вес 3, , 5, 6 разрядов I w,| 3. В этом случае управляющий сигнал на выходе анализатора 2 веса отсутствует, ключи 21 и 22 закрыты, а конвертор 3 отключен. С выходов 3, , 5, 6 разрядов преобразователя 1 сигналы поступают на соответствующие входы мультиплексора k без изменения, а с выходов первого и второго разрядов преобразователя 1 на входы логического переключателя 5, который осуществляет замену в соответствии с табл. 1. Таблица 1 Комбинации импульсов 1-го и 2-го разрядов до замены после замены Примечание:1импульсположительной полярности; 2 - импульс отрицательной полярности; О импульс нулевого уровня. С выхода первого разряда преобразователя 1 импульсы поступают на первый вход элемента ИЛИ 9 и одновременно на первые входы элементов И 15 и 16, причем перед поступлением на вход элементов И 15 импульсы изменяют свое значение в инверторе 12 о На второй вход элемента ИЛИ 9, через ограничитель 6 импульсов, поступают сигналы с выхода 2-го разряда преобразователя 1. Ограничитель не пропускает импульсы отрицательной полярности и на его выходе возможно появление только положительных и нулевых импульсов. С выхода элемента ИЛИ 9 сигнал nocTytiaeT на второй вход элемента И 13, а через инвертор 11 - на второй вход элемента И И. В сумматоре 19 осуществляется сложение выходных сигналов элементов И 13 и Н, причем выходной сигнал элемента И И изменяет свою поярность на противоположную в инверторе 17 полярности импульсов. С выхода сумматора 19 импульсы поступают на вход первого разряда мультиплексора k. Импульсы с выхода второго разряда преобразователя 1 через двухполупериодный выпрямитель 7 и инвертор 10 поступают на вторые входы элементов И 15 и 16„ На первый вход инвертора 10 поступают импульсы с выхода генератора 8, частота следования импульсов равна Fg, с выходов элементов И 15 и 16 импульсы поступают на входы сумматора 20, причем с выхода элемента И 16 через инвертор 18 полярности импульсов, изменяющий полярность импульсов на противоположную. С выхода сумматора 20 сигнал поступает на вход второго разряда мультиплексора . Таким образом, на выходах логического переключателя 5 формируются комбинации импульсов в соответствии с табл. 1, которые и поступают на входы первого и второго раз рядов мультиплексора Пусть вес 3, , 5, 6 разрядов )wj-|7/3. В этом случае управляющий сигнал с выхода анализатора 2 веса открывает ключи 21 и 22 и подключает управляемый конвертор 3. Сигналы с выхода первого и второго разрядов преобразователя 1 поступают на соответствующие входы мультиплексора 4 без изменения, а конвертор 3 изменяет полярность импульсов в и 6 разрядах на противоположную, тем самым уменьшая небаланс в кодовом слове. Таким образом, в сформированном трехуровневом сигнале тактовая частота снижена в 1,33 раза, отсутству ют кодовые слова с BecoMlw -f 3, устранено кодовое слово, состоящее из одних нулей, повышена плотность импульсов в кодовом слосе. На приеме существует возможность контроля достоверности передачи, так как при ем кодового слова с весом) будет свидетельствовать об ошибке. Так как баланс в кодовом слове достигается без введения дополнительных балансных импульсов, то повышается эффективность преобразования и, как следствие, помехоустойчивость и скорость передачи информации. Устройство(фиг. З) осуществляет преобразование 12 двоичных символов в 6 пятиуровневых по предлагаемому способу и содержит преобразователь 1 дискретного сигнала в биполярный сигнал, анализатор 2 веса, конверто 3 полярности импульсов, мультиплексор k, логический переключатель 5, 9 выпрямитель 7, первый элемент ИЛИ 9 первый 10, второй 11, третий 12 инверторы, четвертый инвертор 17, пятый инвертор 18, первый 19 и второй 20 сумматоры, первый ключ 21, второй ключ 22, второй, третий, четвертый и пятый элементы ИЛИ 23-26 и третий сумматор 27. Устройство работает следующим образом. Преобразователь 1 преобразует двенадцатиразрядный двоичный сигнал с тактовой частотой Рд в параллельный шестиразрядный небалансный пятиуровневый сигнал с тактовой частотой Fa 0,5 FA. Преобразование осуществляется по правилу переврда числа из двоичной системы счисления в пятиричную. Анализ 2 веса определяет вес импульсов 3, , 5, 6 разрядов, а мультиплексор 4 осуществляет перевод параллельного балансного пятиуровневого сигнала в после довательный. Пусть вес 3, 5, 6 разрядов |wf-/ 4. В этом случае управляющий сигнал на выходе анализатора 2 веса отсутствует, ключи 21 и 22 закрыты, а управляемый конвертор 3 полярности импульсов отключен. С выходов 3, , 5, 6 разрядов преобразователя 1 сигналы поступают на соответствующие входы мультиплексора k без изменения, а с выходов первого и второго разрядов преобразователя 1 на входы логического переключателя 5, который осуществляет замену в соответствии с табл. 2. С выхода первого разряда преобразователя 1 импульсы поступают на первые входы элементов ИЛИ 9, 23, 2, 25 и 26, причем перед поступлением на вход элементов ИШ 23 и 2+ импульсы изменяют свое значение в инверторах 2 и 17, которые импульсы положительной полярности преобразуют в нулевые, а нулевой импульс - в импульс положительной полярности единичной амплитуды. Одновременно импульсы с выхода 1-го разряда преобразователя 1 поступают на вход сумматора 19, предварительно изменив свою полярность на противопложную в инверторе 11. С выхода второго разряда преобразователя 1 импульсы также поступают на вход сумматора 19, предварительно изменив свою полярность на противоположную в инверторе 10. Одновременно импульсы с выхода вто рого разряда преобразователя 1 поступают на вторые входы элементов ИЛИ 9| 23-26, предварительно пройдя через выпрямитель 7, который положительные импульсы пропускает без изменения, а отрицательные импульсы преобразовывает в положител ные без изменения амплитуды импуль сов С выхода элемента ИЛИ 9 импульсы поступают на третий вход су матора 19 с выхода которого резул тирующий импульс поступает на вход первого разряда мультиплексора . Т а б л и ц а 2 Комбинации импульсов 1-го и 2-го разрядов Примечание: 1- импульс единичного уровня положительной полярности, 2 - импульс двойного уровня положительной полярности, 3 импульс единичного уровня отрица1тельной полярности, ч - импульс дво ного уровня отрицательной полярност О - импульс нулевого уровня. В сумматоре 20 осуществляется сложение импульсов с выхода второго разряда преобразователя 1, с выходов элементов ИЛИ с инверсией 23 и 2k, а также импульсов с выходов элементо ИЛИ 25 и 2б, просуммированных в сумматоре 27 и изменивших свою полярность на противоположную в инверторе 18. С выхода сумматора 20 результирующие импулчзсы поступают на вход второго разряда мультиплексора о Таким образом, на выходах логического переключателя 5 формируются комбинации импульсов в соответствии с данными табл. 2, которые и посту 12 пают на входы первого и второго разрядов мультиплексора 4. Пусть вес 3, , 5, 6 разрядов . В этом случае управляющий сигнал с выхода анализатора веса 2 открывает ключи 21 и 22 и подключает конвертор 3 полярности импульсов Сигналы с выхода первого и второго разрядов преобразователя 1 поступают на соответствующие входы мультиплексора k без изменения, а конвертор 3 изменяет полярность импульсов в четвертом и шестом разрядах на противоположную, тем самым уменьшая небаланс в кодовом слове. Таким образом, в сформированном пятиуровневом сигнале тактовая частота снижена в 2 раза, отсутствует кодовое слово, состоящее из нулей, повышена плотность импульсов в кодовом слове, отсутствуют кодовые слова с весом / Wf/ 75. Формула изобретения 1.Способ преобразования дискретных сигналов, заключающийся в том, что последовательность дискретных сигналов (эднополярных сигналов преобразуют в последовательность многоуровневых биполярных импульсов, отличающийся тем, что, с целью повышения помехоустойчивости и информативности, сравнивают каждый импульс каждой кодовой последовательности, кроме первого и второго, с заданным значением, при превышении которого изменяют на противоположную полярность четные импульсы каждой кодовой последовательности, кроме второго импульса, в противном случае заменяют первый и второй импульсы каждой последовательности на соответствующие комбинации многоуровневых импульсов. 2,Устройство для преобразования дискретных сигналов, содержащее преобразователь двоичного сигнала в биполярный сигнал, старшие выходы которого подключены к соответствующим входам анализатора веса и к первым входам конвертора полярности импульсов, выходы которого соединены с соответствующими первыми входами мультиплексора, выход мультиплексора подключен к выходу устройства, младшие разряды преобразователя двоичного сигнала в биполярный сигнал подключены к соответствующим информ ционным входам логического hepeключателя, выход анализатора веса соединен с управляющими входами логического переключателя, о т л и чающееся тем, что, с целью повышения помехоустойчивости и скорости передачи информации, в устройство введены сумматоры, логический переключатель выполнен на выпря мителе, ограничителе, ключах, элементах И, ИЛИ,инверторах, генераторе, первый информационный вход логического переключателя соединен с входом первого ключа, с первым входом первого элемента ИЛИ, с первым входом четвертого элемента И и чере второй инвертор - с первым входом третьего элемента И, первый выход п вого ключа соединен с первым управляющим входом и с первым выходом ло гического переключателя, второй вых первого ключа подключен к второму выходу логического переключателя, в рой информационный вход логического переключателя соединен через ограничитель с вторым входом первого эл мента ИЛИ и через выпрямитель - с п вым входомтретьего инвертора, выход которого подключен к второму вх ду третьего элемента И, выход генератора соединен с вторым входом тре тьего инвертора и с первыми входами первого и второго элементов И, вых первого элемента И подключен к первому информационному выходу логического переключателя, выход второг элемента И через четвертый инвертор соединен с вторым информационным выходом логического переключателя, выход первого элемента ИЛИ подключе к второму входу первого элемента И и через первый инвертор - к второму входу второго элемента И, выход третьего инвертора соединен с вторыми входами третьего и четвертого элементов И, выход третьего элемента И - непосредственно, а вых четвертого элемента И через пятый инвертор соединены с третьими инфор мационными выходами логического переключателя, выходы первого и второго ключей подключены соответственно к первому и второму управляющим выходам логического переключателя, первый и второй информационные выходы которого соединены соответственно с входами первого и вт рого сумматоров, первый и второй управляющие выходы логического переключателя соединены соответственно с выходами первого и второго сумматоров, которые подключены к соответствующим: вторым входам мультиплексора. 3. Устройство для преобразования дискретных сигналов по п. 2, о т личающееся тем, что, логический переключатель выполнен на ключах, инверторах, выпрямителе, элементах ИЛИ и третьем сумматоре, первый информационный вход логического переключателя соединен через второй инвертор с первым информационным выходом логического переключателя, с первым входом первого ключа, с первыми входами первого, четвертого и пятого элементов ИЛИ и через третий и четвертый инверторы подключены соответственно к первым входам второго и третьего элементов ИЛИ, второй информационный вход логического переключателя соединен с первым входом второго ключа, с третьим информационным выходом логического переключателя и через выпрямитель - с вторыми входами первого, второго, третьего, четвертого и пятого элементов ИЛИ и через первый инвертор - с первым информационным выходом логического переключателя, выход первого элемента ИЛИ подключен к третьему выходу логического переключателя, первый управляющий вход логического переключателя подключен к второму входу первого ключа и к первому управляющему выходу логического переключателя, выходы второго и третьего элементов ИЛИ соединены с первым и ВТОРЫМ информационными выходами логического переключателя, выходы четвертого и пятого элементов ИЛИ подключены к входам третьего сумматора, выход которого через пятый инвертор соединен с третьим информационным выходом логического переключателя. Источники информации, принятые во внимание при экспертизе 1,Технические средства телеобработки информации в АСУ в реальном масштабе времени. М., изд-во МДНТП, 1976, с. 176-177. 2. Transactions on Communication, , № 8, p. 1136-1139, fig. 3 (прототип).

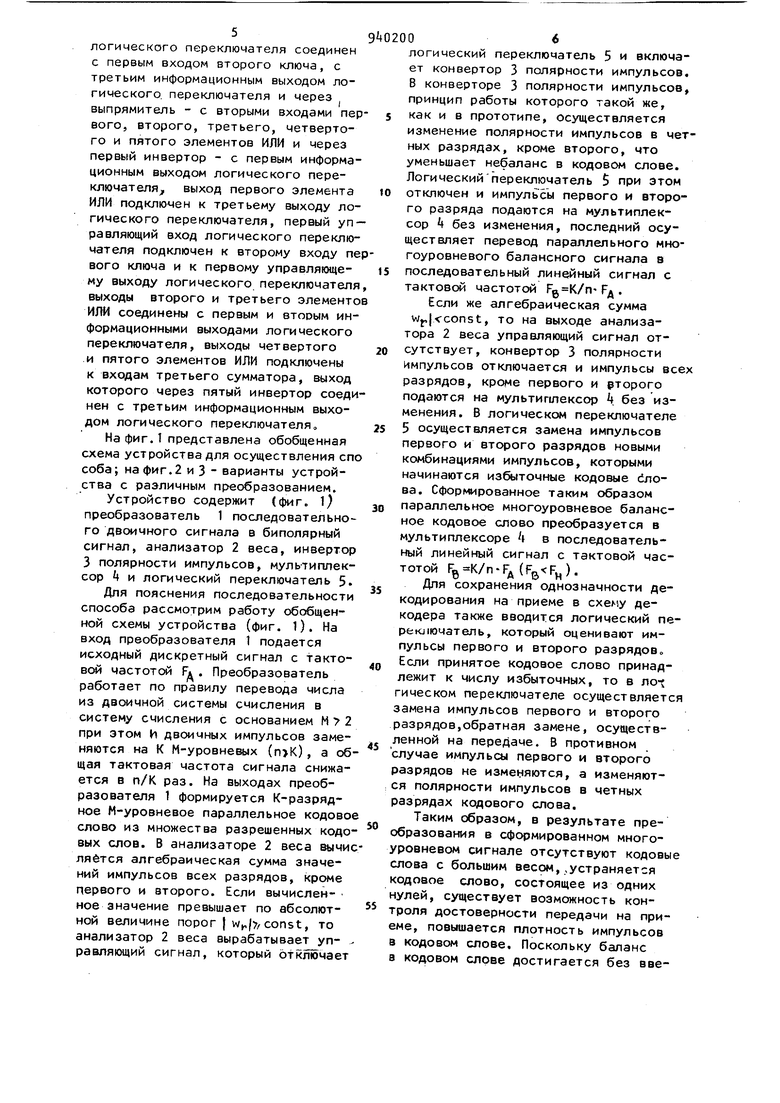

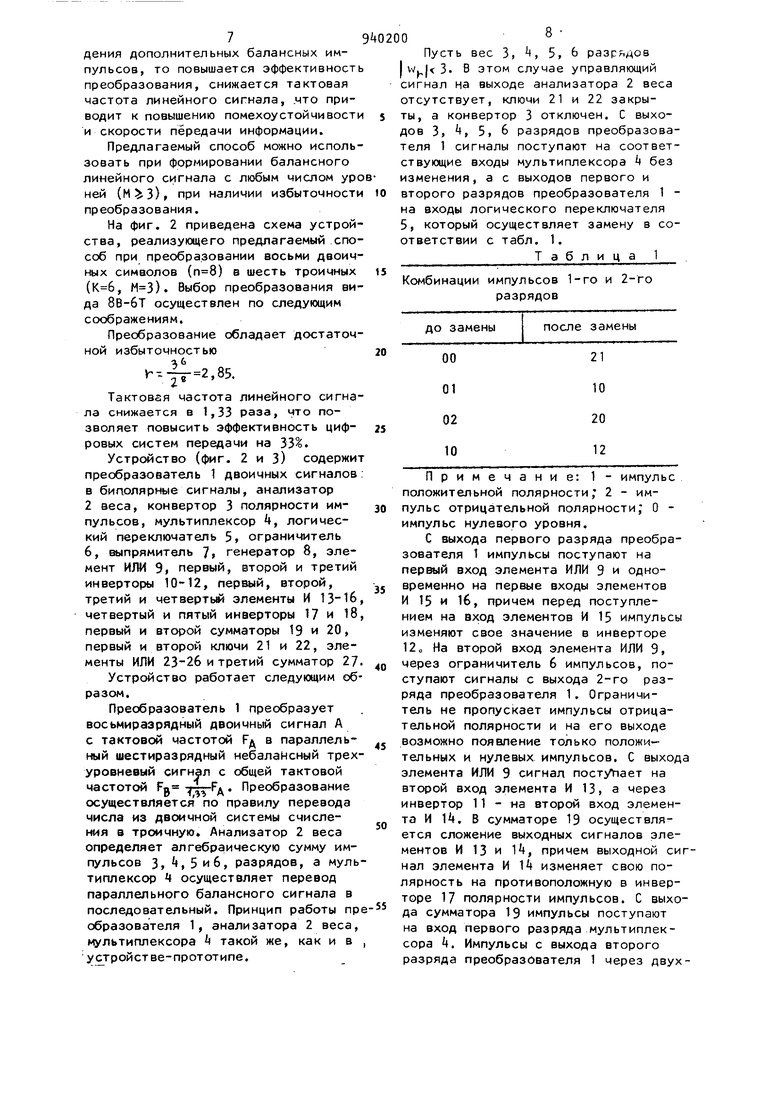

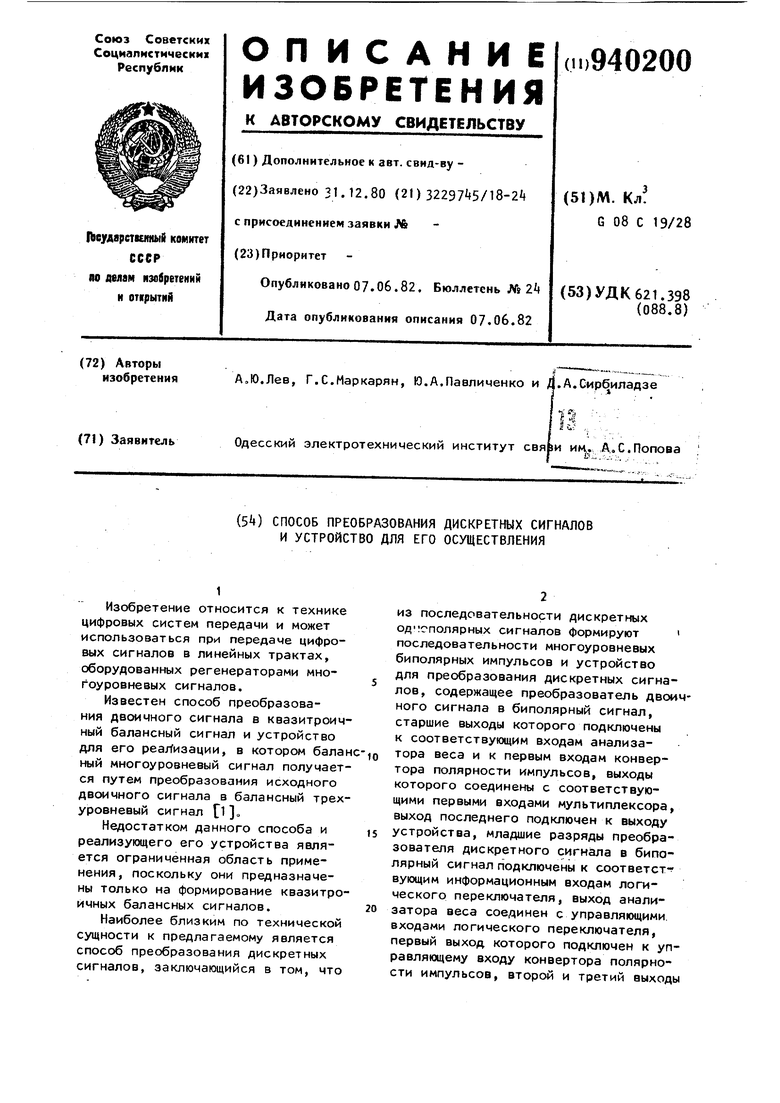

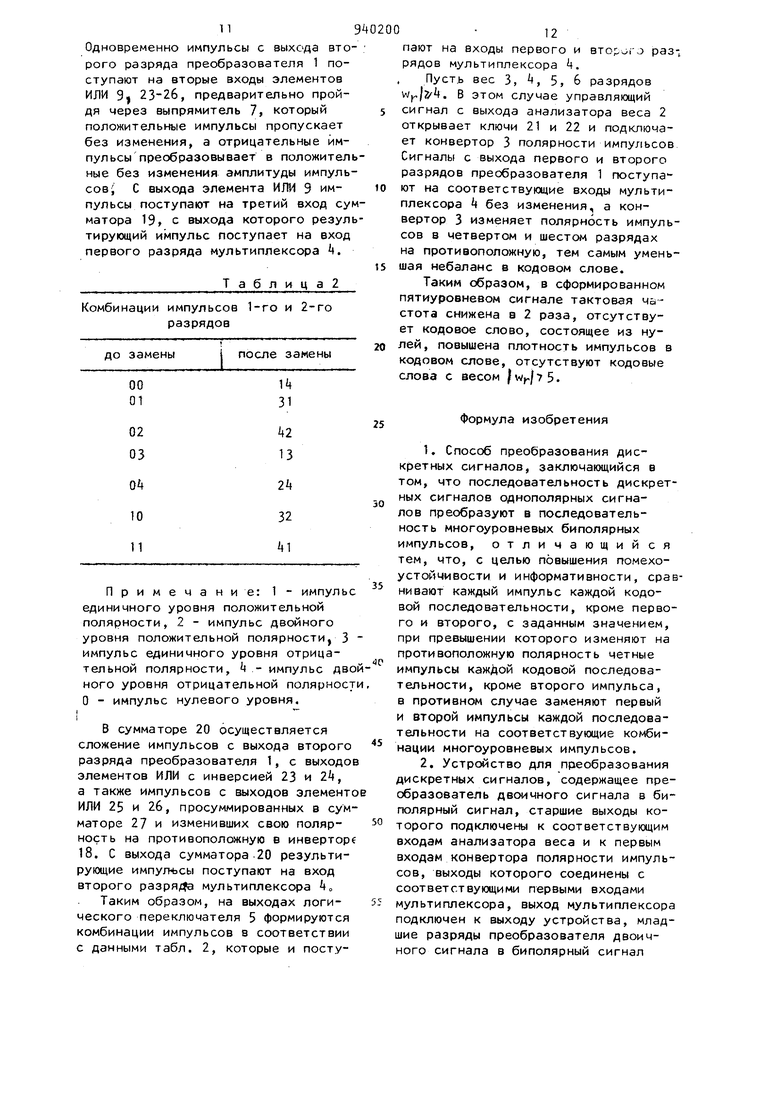

Jti Ф

Фик. 1

fO

Авторы

Даты

1982-06-30—Публикация

1980-12-31—Подача