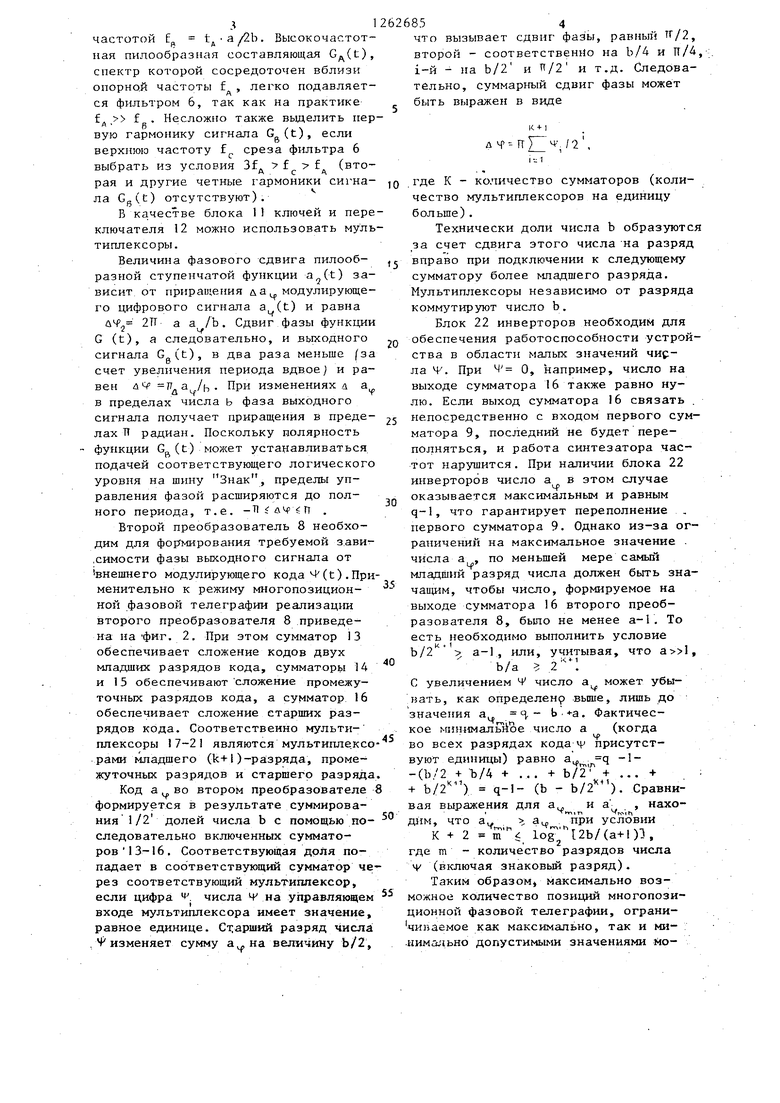

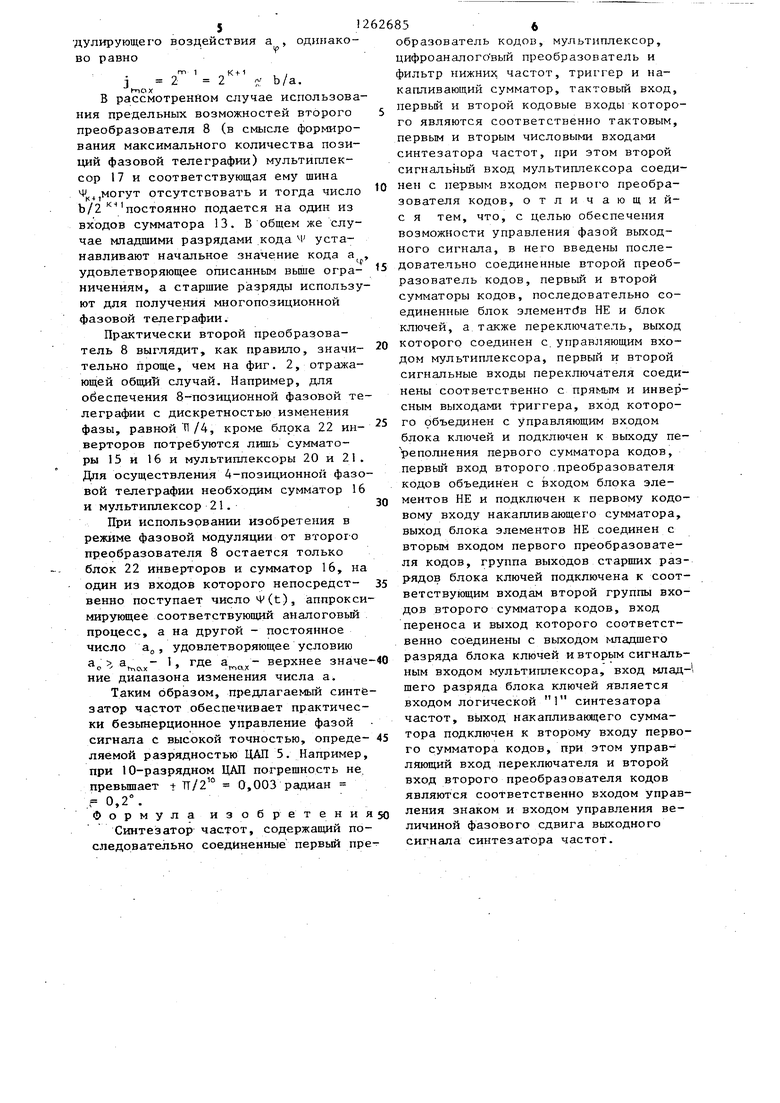

1 Изобретение относится к радиотехнике и может быть использовано в приемопередающей и измерительной аппаратуре. Целью изобретения является обеспечение возможности управления фазой выходного сигнала. На фиг. 1 представлена электричес кая структурная схема синтезатора частот; на фиг. 2 - пример выполнения второго преобразователя кодов. Синтезатор частот содержит накапливающий сумматор 1,, мультиплексор 2, триггер 3,первьй преобразователь 4 кодов, цифроаналоговьм преобразователь (ЦАП) 5, фильтр 6 нижних частот-, блок 7 элементов НЕ, второй преобразователь 8 кодов, первый сумматор 9 кодов, второй сумматор 10 кодов, блок 11 ключей, переключа|тель 12. При этом второй преобразователь 8 кодов содержит первый, второй, третий и четвертьй сумматоры 13 16 кодов, первьш, второй, третий, четвертый и пятый мультиплексоры 1721, блок 22 инверторов. Синтезатор частот работает следующим образом. Под действием тактовых импульсов 6(t), следующих с опорной частотой f , содержимое накапливающего сумматора 1 , имеющего в общем случае переменную емкость в, изменяется на величину а. Числа в и а задаются соответственно на первом и втором числовых входах синтезатора частот. Поступая на первый сумматор 9, функ1щя a(t) суммируется в нем с модулирующим воздействием ац). Диапазон возможных значений а выбирается из условия получения импульсов переполнения p(t). Минимальное значение а не должно быть менее q-b+a, ибо в противном случае первый сумматор 9 может не переполниться. С другой стороны, а; не должно превышать значения q-a, так как при нарушении последнего условия первый сумма- . тор 9 постоянно будет переполнен. Здесь q 2 - емкость первого сумматора 9, выполненного в виде п-разрядного двоичного сум)«атора. Моду(лирующее воздействие, таким образом должно удовлетворять условию q-a а. - Ъ + а. Сдвиг момента переполне НИН первого сумматора 9 пропорционален Изменениям числа а. Особенност технической реализации принципа уп852равления моментом переполнения первого сумматора9 заключается в том, что емкость b накапливающего сумматора 1 отличается от емкости первого сумматора 9, а именно b q.Поэтому функция а (t) на выходе первого сумматора 9 имеет разрывы, т.е. участки с приращениями, на q-b единиц превышающими величину а. Для устранения указанного явления служат второй сумматор 10 и блок 11 ключей. Импульс переполнения p(t) первого оумматора 9 открывает блок 11 ключей, и на один из входов второго сумматора 10 поступает инверсное число Ь, а на вход переноса - единица, т.е. на интервале переполнения первого сумматора 9 к функции а (t) добавляется величина (q-b), чем и устраняются отмеченные разрьгоы в сформированной таким образом функции а (t). Последняя передается на один из входов мультигшексора 2, на-другой вход которого поступает функция a.,(t) a(t) + Ъ + 1, получаемая с помощью первого преобразователя 4 и блока элементов НЕ 7. Первый преобразователь 4, как следует из выражения для a(t), представляет собой сумматор с блоком элементов НЕ на том входе, на который подается функция ajCt), причем вход переноса сумматора соединяется с шиной логической единицы. Мультиплексор 2 управляется импульсами q(t), формируег 1ми триггером 3 со счетным входом. Триггер 3 переключается импульсами переполнения p(t) первого сумматора 9. Полярность импульсов q(t) может изменяться с помощью переключателя 12, для чего входы последнего соединены с прямым и инверсным выходами триггера 3, а управляющий «ходс шиной Знак, на которую подается соответствующий логический уровень. В результате переключений триггера 3 на выход мультиплексора 2 поочередно проходят функции ) и ajjCt), преобразуемые далее с помощью ЦАП 5 в аналоговые эквиваленты. Таким образом формируется числовая функция g(t) и соответствующая ей аналоговая G(t). Функция представляет собой чередование восходящих и нисходящих участков, сопрягакщихся друг с другом таким образом, что среднее значение Gg(t), выделяемое фильтром 6, является периодической функцией с i: a/2b. Высокочастот частотой Сл() пая пилообразная составляющая j спектр которой сосредоточен вблизи опорной частоты f, легко подавляет ся фильтром 6, так как на практике f. f . Неслож Ю также выделить пер д 5 G,(t). вую гармонику сигнала верхнюю частоту f среза фильтра 6 выбрать из условия 3f. f f, tt . С рая и другие четные гармоники сигнала Gg(t) отсутствуют). В качестве блока 1f ключей и пере ключателя 12 можно использовать муль типлексоры. Величина фазового сдвига пилообразной ступенчатой функции a,j(t) зависит от приращения д а ц, модулирующего цифрового сигнала а (t) и равна а /Ь. Сдвиг фазы функции ДЧ2 2ТТ а G (t), а следовательно, и вькодного сигнала ь (.с;, в два раза меньше (за счет увеличения периода вдвое) и равен а а, ь При изменениях а а в пределах числа ь фаза выходного сигнала получает приращения в пределах ТТ радиан. Поскольку полярность функции Gj (t) может устанавливаться подачей соответствующего логического уровня на шину Знак, пределы управления фазой расширяются до полного периода, т.е. . Второй преобразователь 8 необходим для формирования требуемой зави.симости фазы выходного сигнала от внешнего модулирующего кода M(t) .При менительно к режиму многопозиционной фазовой телеграфии реализац1ш второго преобразователя 8 приведе на нафиг. 2. При этом сумматор 13 обеспечивает сложение кодов двух младших разрядов кода, сумматоры 14 и 15 обеспечивают сложение промежуточных разрядов кода, а сумматор 16 обеспечивает сложение старших разрядов кода. Соответственно мультиплексоры 17-2 являются мультипле.ксо рами младшего (k+1)-разряда, промежуточных разрядов и старшего разряда Код а , во втором преобразователе формируется в результате суммирования 1 /2 долей числа Ь с помощью последовательно включенных сумматоров 13- 16, Соответствующая доля попадает в соответствующий сумматор че рез соответствующий мультиплексор. еслк цифра числа Ч на управляющем входе мультиплексора имеет значение, равное единице. Старший разряд Числа , Чизменяет сумму а на величину Ь/2, 85 что вызывает сдвиг фазы, равньп ТГ/2, второй - соответственно на Ь./4 и 1Т/4, . i-й - на Ь/2 и Tt/2 и т.д. Следовательно, суммарный сдвиг фазы может быть выражен в виде Д 4 , i i 1 .где К - количество сумматоров (количество мультиплексоров на единицу больше). Технически доли числа Ь образуются за счет сдвига этого числа на разряд вправо при подключении к следующему сумматору более младшего разряда. Мультиплексоры независимо от разряда коммутируют число ь. Блок 22 инверторов необходим для обеспечения работоспособности устройства в области малых значений чирла Ч-. При О, например, число на выходе сумматора 16 также равно нулю. Если выход сумматора 16 связать . непосредственно с входом первого сумматора 9, последний не будет переполняться, и работа синтезатора частот нарушится. При наличии блока 22 инверторов число а в этом случае оказывается максимальным и равным q-1, что гарантирует переполнение первого сумматора 9. Однако из-за ограничений на максимальное значение . числа а , по меньшей мере самый младший разряд числа должен быть значаир м, чтобы число, формируемое на выходе сумматора 16 второго преобразователя 8, бьшо не менее а-1. То есть необходимо выполнить условие что , Ь/2 : а-1, или, учитывая. Ь/а С увеличением Ч число а может увы- вать, как определен выше, лишь до значения а Я- Ь.а. Фактичесое мин 1мальйое число а (когда о всех разрядах кода ч присутстуют единицы) равно a(,q -1(Ъ/2 + Ъ/4 + ... + Ь/2 + ... + Ь/2) q-1- (Ь - Ь/2). Сравниая выражения для а,„ и а.. , нахоч-.п -v.,-,f,при условии им, что а а ч, (a+l)l, К -ь 2 - т де m - количество разрядов числа у (включая знаковьш разряд). Таким образом максимально возожное количество позиций многопозиионной фазовой телеграфии, огрании))аемое как максимально, так и миимйльно допустимыми значениями но- дулирующего воздействия а, одинаково равно 1 2 В рассмотренном случае использова ния предельных возможностей второго преобразователя 8 (в смысле формирования максимального количества позиций фазовой телеграфии) мультиплексор 17 и соответствующая ему шина Ч,могут отсутствовать и тогда число Ь/2 постоянно подается на один из входов сумматора 13. В общем же случае младшими разрядами кода М устанавливают начальное значение кода а удовлетворяющее описанньм вьше ограничениям, а старшие разряды использу ют для получения многопозидионной фазовой телеграфии. Практически второй преобразователь 8 выглядит, как правило, значительно проще, чем на фиг. 2, отражающей общий случай. Например, для обеспечения 8-позиционной фазовой те леграфии с дискретностью изменения фазы, равнойП/4, кроме блока 22 инверторов потребуются лишь сумматоры 15 и 16 и мультиппексоры 20 и 21 Для осуществления 4-позиционной фазо вой телеграфии необходим сумматор 16 и мультиплексор 21. При использовании изобретения в режиме фазовой модуляции от второго преобразователя 8 остается только блок 22 инверторов и сумматор 16, на один из входов которого непосредственно поступает число Ч(t), аппрокси мирующее соответствующий аналоговьй процесс, а на другой - постоянное число а, удовлетворяющее УСЛОВИЮ а , 1, где верхнее знач ние диапазона изменения числа а, Таким образом, предлагаемый синт затор частот обеспечивает практичес ки безынерционное управление фазой сигнала с высокой точностью, опреде ляемой разрядностью ЦАП 5. Например при 10-разрядном ЦАП погрешность не превьш1ает t 0,003 радиан р 0,2°. Формула изобретени Синтезатор частот, содержащий по следовательно соединенные первый пр образователь кодов, мультиплексор, цифроаналоговый преобразователь и фильтр нижних частот, триггер и накапливающий сумматор, тактовый вход, первый и второй кодовые входы которого являются соответственно тактовым, первым и вторым числовыми входами синтезатора частот, при этом второй сигнальный вход мультиплексора соединен с первым входом первого преобразователя кодов, отличающийс я тем, что, с целью обеспечения возможности управления фазой выходного сигнала, в него введены последовательно соединенные второй преобразователь кодов, первый и второй сумматоры кодов, последовательно соединенные блок элементбв НЕ и блок ключей, а также переключатель, выход которого соединен с. управляющим входом мультиплексора, первый и второй сигнальные входы переключателя соединены соответственно с прямым и инверсным выходами триггера, вход которого объединен с управляющим входом блока ключей и подключен к выходу переполнения первого сумматора кодов, первьш вход второго .преобразователя кодов объединен с Входом блока элементов НЕ и подключен к первому кодовому входу накапливающего сумматора, выход блока элементов НЕ соединен с вторым входом первого преобразователя кодов, группа выходов старших разрядов блока ключей подключена к соответствующим входам второй группы входов второго сумматора кодов, вход переноса и выход которого соответственно соединены с выходом младшего разряда блока ключей и вторым сигнальным входом мультиплексора, вход младшего разряда блока ключей является входом логической 1 синтезатора частот, выход накапливакщего сумматора подключен к второму входу первого сумматора кодов, при этом управляющий вход переключателя и второй вход второго преобразователя кодов являются соответственно входом управления знаком и входом управления величиной фазового сдвига выходного сигнала синтезатора частот.

фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1985 |

|

SU1254576A1 |

| Синтезатор частот | 1988 |

|

SU1566455A1 |

| Синтезатор частот | 1987 |

|

SU1478327A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1988 |

|

SU1757080A1 |

| Синтезатор частот | 1986 |

|

SU1337990A1 |

| Синтезатор частот | 1987 |

|

SU1431034A1 |

| Делитель частоты | 1983 |

|

SU1162014A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Делитель-синтезатор частот | 1982 |

|

SU1149395A1 |

| Синтезатор частот | 1987 |

|

SU1610599A1 |

Изобретение относится к радиотехнике и обеспечивает возм1;жность управления фазой выходного сигнала. Синтезатор частот содержит накапливакядий сумматор 1, мультиплексор 2, триггер 3, преобразователи кодов (ПК) 4, 8, ЦАП 5, фильтр 6 нижних частот, блок злементов НЕ 7, сумматоры 9, 10 кодов, блок ключей 11 и переключатель 12. На накапливающий сумматор 1 поступают числа айв. Ж 8 необходим для формирования требуемой зависимости фазы выходного сигнала от внешнего модулирующего кода (t). На выходе сумматора 9 формируется ступенчатая функция, имеющая разрывы. Для их устранения служат сумматор IО и блок ключей 11. Импульс переполнения сумматора 9 открывает блок ключей 11 и через него на сумматор 10 поступает инверсное число в, а на вход переноса - 1. При этом на интервале переполнения сумматора 9 устраняются разрывы. Через мультиплексор 2, ЦАП 5 и 6 i нижних частот сигнал проходит на вы(Л ход. Мультиплексор 2 управляется импульсами, формируемыми триггером 3. Полярность импульсов управления изменяется при помощи переключателя 12 . На его управляющий вход подается сигнал З.нак . 2 ил. фиг.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты | 1983 |

|

SU1162014A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-10-07—Публикация

1985-04-19—Подача