(54) УСТРОЙСТВО ДЛЯ ПРИЕМА ТЕЛЕСИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема телесигналов | 1976 |

|

SU610152A1 |

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

| Устройство телесигнализации | 1983 |

|

SU1149297A1 |

| Устройство для передачи телесигналов | 1978 |

|

SU763945A1 |

| Устройство для приема команд телеуправления | 1981 |

|

SU991473A1 |

| Устройство для контроля приема телесигналов | 1981 |

|

SU1005150A1 |

| Устройство для передачи телесигналов | 1983 |

|

SU1113834A1 |

| Устройство для приема информации с обнаружением ошибок | 1975 |

|

SU556480A1 |

| Адаптивный приемник информации с рассредоточенных объектов | 1991 |

|

SU1807508A1 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

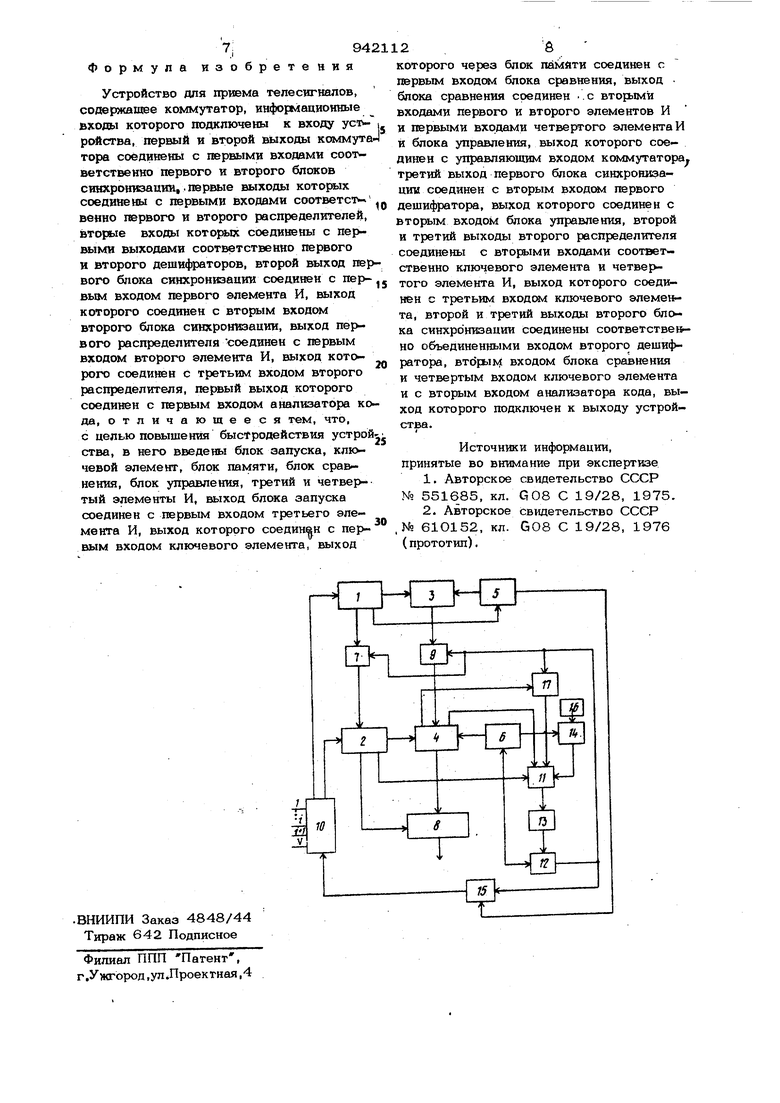

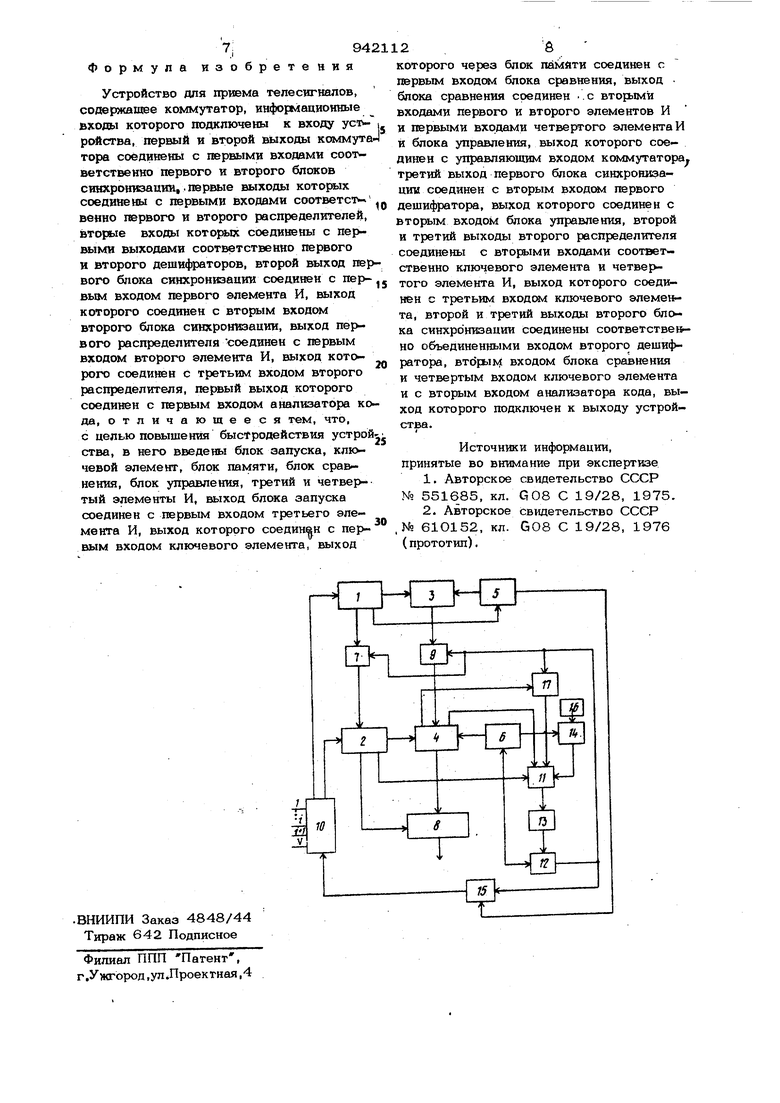

Изобретение относится к телемеханике и может быть использовано в устройствах телеуправления и телесигнализации рассредоточенных объектов. Известно устройство для приема теле- сигналов, содержащее регистры сдвига, распределители, дешифраторы, элементы И ИЛИ l. Недостатком устройства является значительное время, которое тратится на вхождение в синхронизм и цикловое фазирование приемников телесигнализации, что снижает скорость сбора информации от рассредоточенных объектов. Наиболее близким по технической сущности к предлагаемому является устройство для приема телесигналов, ct держащее коммутатор, информационные входы которого соединены с первым входом устройства, управляющий вход коммутатора объединен с управляющупи входами первого и второго элементов И и поог ключен к второму вхойу устройства, первый выход коммутатора соединен с первым входом первого блока фазирования (синхронизации) и третьего элемента И, первый, второй и третий млходьг первого блока фазирования соединены соответст -г венно с первыми входами первого распределителя и первого регистра сдвига, . входами первого и третьего элементов И, выход третьего элемента И соединен с вторым входом первого регистра сдвига, выход которого через дешифратор соединен с вторым входом первого распределителя,, выход которого соединен с вторым входом второго элемента И, выход которого соединен с первьм входом второго распределителя, второй выход коммутатора соединен с первым входом второго блока фазирования (синхронизации) и четвертого элемента И, вы:;од которого соединен с, первым входбм второго регистра сдвига, первый выход которого через второй дешифратор соединен с вторьц входом второго распределителя, второй вход второго блока фазирования соединен с выходом первого 394 элемента И, первый выход - с третьим входом второго распределителя и вторым входом второго регистра сдвига, .третий выход - с входом третьего распределителя, выход которого соединен с вторым входом четвертого элемента И и первым входил анализатора кода, второй и третий выходы которого соединены с первым выходом второго распределителя и рым выходом второго регистра сдвига, пе)звый и второй выходы анализатора кода и третий выход второго регистра сдви га соединены с соответствующими входами пятого элемента И, выход которого соединен с выходом устройства 2. В этом устройстве сокращается время, затрачиваемое на синхронизацию и цикловое фазирование, приемных устройств при переключении с канала на канал. Однако известное устройство обладает недостаточно высоким быстродействием, так как сигнал на переключение канала может передаваться либо от датчика времени, либо по окончании цикла телесигнализации, определяемого выделением ключевой кодовой комбинации, передаваемой в начале каждого цикла телесигнализации, то неизбежны потери времени: Э первом случае - за счет того, что период между переключающимися импуль сами должен соответствовать длительное- ти максимального цикла телесигнализации, а во втором случае - за счет ожидания ( в среднем половины цикла) прихода ключевой комбинации (несмотря на то, что устройство приема засинхронизир вано). Цель изобретения - повышение быстро действия устройства. Поставленная цель достигается тем, что в устройство для приема телесигналов, содержащее коммутатор, информацио ные входы которого подключены к входу устройства, первый и второй выходы коммутатора соединены с первыми входами соответственно первого и второго блоков синхронизации, первые выходы которых с динены с первыми входами соответственно первого и второго распределителей, вторые входы которых соединены с первыми выходами соответственно первого и второго дешифраторов, второй выход первого блока синхронизации соединен с первым входом первого элемента И, выход которого соединен с вторым входом второго блока синхронизации, выход первого распределителя соединен с первым входом второго элемента И, выход которого соединен с третьим входсм второго 24 распределителя, первый выход которого соединен с первым входом анализатора кода, введены блок запуска, ключевой элемент, блок памяти, блок сравнения, блок управления, третий и четвертый элементы И, выход блока запуска соединен с первым входом третьего элемента И, выход которого соединен с первым входом ключевого элемента, выход которого через ёлок памяти соединен с первым входом блока сравнения, выход блока сравнения соединен с вторыми входами первого и второго элементов И и первыми входами четвертого элемента И и блока управления, выход которого соединен с управляющим входом коммутатора, третий выход первого блока синхронизации соединен с вторым входом первого дешифратора, выход которого соединен с вторым входом блока управления, второй и третий выходы второго распределителя соединены с вторыми входами соответственно ключевого элемента и четвертого элемента И, выход которого соединен с третьим входом ключевого элемента, второй и третий выходы второго блока синхронизации соединены соответственно объединенными входом второго дешифратора, вторым входом блока сравнения и четвертым входся клк чевого элемента и с вторым входом анализатора кода, выход которого подключен к выходу устройства. На чертеже показана блок-схема устройства. Устройство содержит первый и второй блоки 1 и 2 синхронизации, хкрвый и второй распределители 3 и 4, первый и второй дешифраторы 5 и 6, первый элемент И 7, анализатор 8 кода, второй элемент И 9, коммутатор 10,, ключевой элемент 11, блок 12 сравнения, блок 13 памяти, третий элемент И 14, блок 15 управления, блок 16 запуска, четвертый элемент И 17. Устройство работает следующим образом. На информационные входы 1-f , 1 +1,...,V коммутатора 10 от группы рассредоточенных объектов поступает информация (телесигнализация) в виде непрерывной последовательности кодовых комбинаций. В начале каждого цикла телесигнализации следует фазирующая ключевая кодовая комбинация. Информация, поступающая в устройство по (1 +.)-4лу входу (каналу), подается на вход блока 1 синхронизации. С выхода блока 1 После регенерации информация 594 поступает в дешифратор 5 ключевой комбинации. После регистрации ключевой комбинации и ее декодирования дешифратором 5 на его выходе формируется импульс сброса распределителя 3 в исходное соотояние, т. е. тактовая синхронизация и цикловая фаза инфо1 4ации, поступающие по (i+1) каналу, запоминаются соответственно блоком 1 и распределителем 3. При этом, на втором выходе дешифратора 5 формируется сигнал, подготавливающий подключение первого блока 1 синхронизации к (ч +2)-му каналу, а второго блока 2 синхронизации к (1 +1)му каналу. Одновременно подобные комбинации телесигнализации, поступающие по i -ому каналу, подаются на вход блока 2 синхронизации и после регистрации поступают в дешифратор 6 ключевой комбинации. После регистрации ключевой комбинации на выходе дешифратора 6 появляется импульс сброса (установки) распредеп теля 4 в исходное состояние (осуществляет ся фазирование распределителя 4), после чего с анализатора 8 кода, на который с вы хода блока 2 и распределителя 4 посту- пают синхронизирующие импульсы, выдает ся сигнал, разрешающий деши4чзацшо при тплаемых кодовых комбинаций, поступающих по 1 -му каналу в дешифратор коман (не показан). Со второго выхода деши(} ратора б выдается сигнал, которж 1й (при наличии запускающего сигнала, поступак щего с блока 16) через элемент И 17 открывает ключевой элемент 11. Кодовые комбинации поступают через ключевой элемент 11 в блок 13 памяти, в котором запоминается первая пришедшая по каналу кодовая комбинация, и на блок 12 сравнения, где каждый цикл работы распределителя 4 сравнивается, кодовая комбинация приходит из канала с кодовой комбинацией, записанной в блоке 13 памяти. При завершении приема по -/-му каналу полного цикла телесигнализации на вход блока 2 и, следовательно, на вход блсжа 12 сравнения поступает кодовая комбинация, аналогичная записанной в блоке 13 памяти, в результате чего на выходе блока 12 сравнения появляется сигнал, по которому блок 15 управления коммутатором выдает команду на коммутатор 10, осуществляющий пбяключение ( 1 +2)-го канала, к входу блока 1 синхронизации, ( i +1 )-го канала к выход блока 2 синхронизации. Этим же сигналом осуществляется перефазированив 2 . блока 2 и распределителя 4 и через элемент И 17 снова разрешается запись в блок 13 памяти первой пришедшей по каналу (ч-И)-ной кодовой комбинации. ЕСЛИ в процессе анализа кодовых комбинаций, поступающих по (i+l)-My каналу, вследствии неисправности канала, дешифратором 5 не была зарегистрирована и декодирована ключевая кодовая комбинация, с второго выхода дешифратора 6 на блок 15 управления коммутатором выдается сигнал, подготавливающий подклк чение первого блока 1 синхронизации к ( 1 +2)-му каналу и запрещающий переключение второго блока 2 синхронизации с 1 на (-1+1)-ой канал. После выделения ключевой кодовой комбинации, принятой по ( 1+2)-му каналу, с дешифратора 5 выдается сигнал, по которому блок 15 подает команду в коммутатор 1О на подклк чение первого блока 1 синхронизации к ( i +3) каналу, а второго блока 2 си хронизашга к ( 4-2)-му каналу. . Таким образом, время, необходимое для сбора информации от рассредоточенных объекте сокращается за счет того, что исключается время ожидания от момента переключения каналов до прихода ключевс вой кодовой комбинации. По сравнению с устройством, в котором сигнал на переклк ченве каналов выдается после приема по i -му каналу ключевой комбинации, средний выигрыш по времени определяется выражением T,.i,W а по сравнению с устройством, где переключение производится от датчика времени, выражением N AV.2()tk где tj, - длительность приема одной кодовой комбинации, и- - число кодовых комбинаций, передаваемых в никле ТС по i нчу каналу; у.,„- число кодовых комбинаций в цнкле телесигнализации, имею- тем максимальную длительность; N - число опрашиваемых объектов (каналов). Расчеты, произведенные по приведенным формулам, показывают, что время сброса инфО1 5ации в первом случае ссжраошется в среднем в полтора раза, а во втором случае - в два раза. Формула изобрете н и я Устройство для приема телесигналов, содержащее коммутатор, информационные входы которого подключены к входу yciw ройства, первый и второй выходы коммута тора соединены с первыми входами соответственно первого и второго блоков синхронизации..первые выходы которых соединены с первыми входами соответст веино первого и второго распределителей, вторые входы которых соединены с перш 1МИ выходами соответственно первого и второго дешифраторов, второй выход пер вого блока синхронизации соединен с пер вьол входом первого элемента И, выход которого соединен с вторым входом второго блока синхронизации, выход nei вого распределителя соединен с первым входом второго элемента И, выход которогчз соеди{юн с третьим входом второго распределителя, гюрвый выход которого соединен с первым входом анализатора ко да, отличающееся тем, что. с целью повышения быстродействия устрой ства, в него введены блок запуска, клк чевой элемент, блок памяти, блок сравнения, блок управления, третий и четвертый элементы И, выход блока запуска соединен с первым входом третьего элемента И, выход которого соединен с первым входом ключевого элемента, выход 94 2а которого через блок памяти соединен с первым входсяи блока сравнения, выход блока сравнения соединен ,.с вторыми входами первого и второго элементов И первыми входами четвертого элементам лока управления, выход которого соединен с управляющим входом коммутатора, третий выход первого блока синхронизации соединен с вторым вxoдcйvl гюрвого дешифратора, выход которого соединен с вторым входом блока управления, второй и третий выходы второго распределителя соединены с вторь1ми входами соответственно ключевого элемента и четве{ того элемента И, выход которого соединен с третьим вхоасм ключевого элемента, второй и третий выходы второго блока синхронизации соединены соответстве но объединенными входом второго деши( ратора, вторьщ входом блока сравнения и четвертым входом ключевого элемента и с вторым входом анализатора кода, выход которого подключен к выходу устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 551685, кл. G08 С 19/28, 1975. 2.Авторское сввдетельство СССР № 61О152, кл. GO8 С 19/28, 1976 (прототип).

Авторы

Даты

1982-07-07—Публикация

1980-12-03—Подача