(54) УСТРОЙСТВО ДЛЯ ПРИЕМА ТЕЛЕСИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема телесигналов | 1980 |

|

SU942112A1 |

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

| Устройство для приема команд телеуправления | 1981 |

|

SU991473A1 |

| Адаптивное устройство для приема информации с групп рассредоточенных объектов | 1990 |

|

SU1837346A1 |

| Устройство для передачи и приема самосинхронизирующихся кодограмм | 1986 |

|

SU1403379A1 |

| Способ передачи сигналов точного времени по линиям связи с переменным временем распространения и устройство для его реализации | 1979 |

|

SU858058A1 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

| Устройство для контроля приема телесигналов | 1981 |

|

SU1005150A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

1

Изобретение относится к области телемеханики и может быть использовано при телемеханизации рассредоточенных объектов.

Известно устройство для приема телесигналов (1), содержащее регистры сдвига, распределители, блоки памяти и логнческие элементы И, ИЛИ.

Недостатком такого устройства является зиачительное время вхождения в синхронизм по Циклу и такту, что снижает скорость передачи информации.

Наиболее близким по технической сущности к изобретению является устройства для приема телесигналов 2, содержащее первый

блок фазирования, первый выход которого подключен ко входу первого распределителя, вто; рой выход - к первому входу второго распре- , делителя и к первому входу первого регистра сдвига. Первый выход первого распределителя соединен с первым входом первого элемента И, выход которого подключен ко второму входу первого регистра сдвига. Второй выход первого распределителя соединен с первым входом анализатора кода, ко второму входу которого подключен выход второго распределителя, а к третьему входу - первый выход первого регистра сдвига. Выходы анализатора кода соеаннены с первыми входами второго элемента И,

ко второму входу которого подключен второй выход первого регистра сдвига. Третий выход первого регистра сдвига через первый дешифратор соединен со вторым входом второго распределителя.

Недостатком известного устройства является низкое быстродействие, обусловленное длительным .временем вхождения в синхронизм. Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в предложенное устройство введены коммутатор, первый и второй выходы которого подключены соответственно к i-му и ( + 1)-му ннформационным Входам коммутатора, второй блок фазирования, третий распределитель, второй дешифратор, второй регистр сдвига, третий, четвертый и пятый элементы И. Информационные входы коммутатора подключены ко входам устройства, первый выход - ко входу первого блока фазирования и второму входу первого

элемента И, второй выход - ко входу второго блбка фазирования и к первому входу третьего элемента И, ко второму входу которого подключен перв1 й выход второго блока фазирования, а выход соединен с первым входом второго регистра сдвига, второй вход которого и

первый вход третьего распределителя соединеtabt со вторым выходом второго блока фазирования. Выход второго регистра сдвига через второй дешифратор подключен ко второму входу третьего распределителя, выход которого соединен с первым входом четвертого элемента И. Третий выход второго блока фазирования подключей к первому входу;пятого элемента И, выход которого соединен со вторым входом первого блока фазирования. Выход четвертого элемента И подключен к третьему входу второго распределителя. Управляющий вход устройства соединен со вторыми входами четвертого и пятого элементов И и со вторым входом коммутатора.

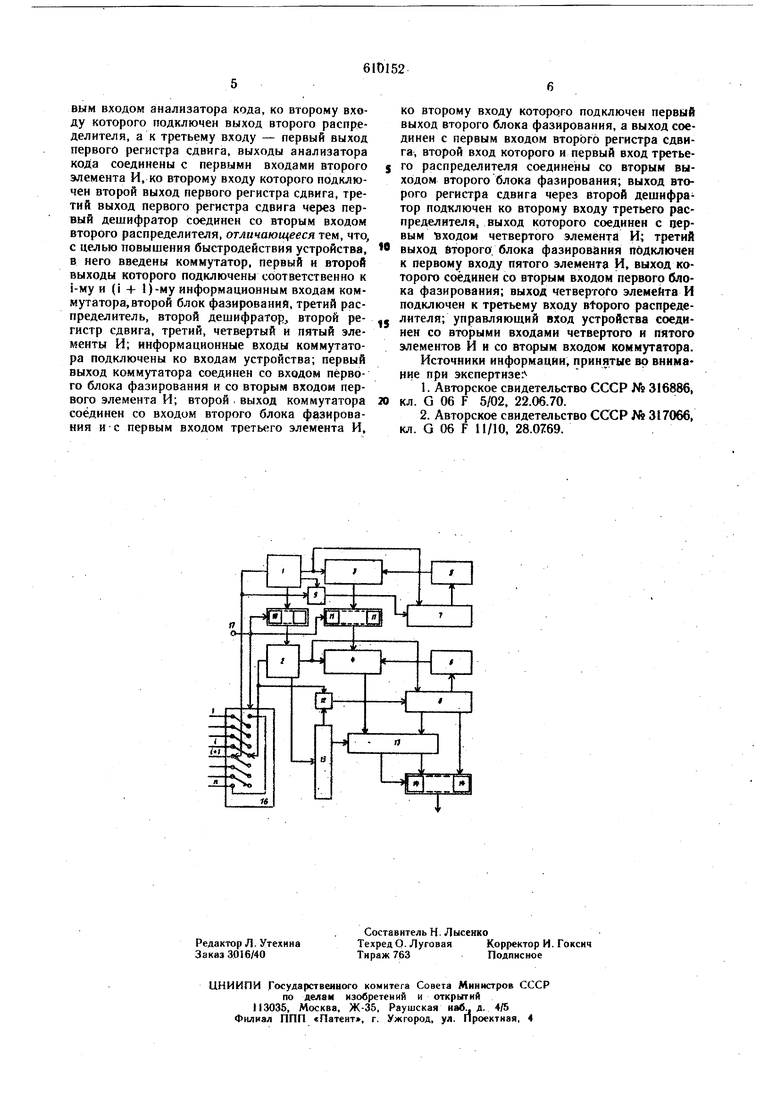

Функциональная схема устройства показана на. чертеже.

Устройство содержит второй 1 и первый 2 блоки фазирования, третий 3 и второй 4 распределители, второй 5 и первый 6 дешифраторы, второй 7 и первый 8 регистры сдвига, третий 9, пятый 10, четвертый 11 и первый J2 элементы И, анализатор кода 13, второй элемент И 14, первый распределитель 15 и ком мутатор 16.

Устройство работает следующим образом.

На информационные входы коммутатора 16 от группы рассредоточенных объектов поступает информация телесигнализации в виде непрерывной последовательности кодовых комбинаций. Информация телесигнализации, поступающая в устройство по (i -f 1)-му входу, подается на вход блока фазирования 1 и элемент И 9, на второй вход которого подаются стробирующне импульсы с блока 1. С выхода элемента И 9 ннформация записывается в регистр сдвнга 7. После регистрации кодовой комбинации циклового фазирования и ее декодирования блоком 5 на его выходе формируется импульс сброса распределителя 3 ц, исходное состояние. Таким образом, тактовая и цикловая фазы информации телесигнализации, поступающей по (i + 1) входу, запоминается соответственно блоками 1 и 3.

Одновременно кодовые комбинации телесигнализации, поступающие по i-му каналу, подаются на вход блока фазирования 2 и на элемент И 12, с выхода которого информация телесигнализации записывается в регистр сдвига 8. При регистрации кодовой комбинации циклового фазирования с выхода блока б навход распределителя тактов 4 поступает импульс его сброса в исходное состояние. Кодовые комбинации телесигнализации, записанные в блоке 8, анализируются анализатором кода 13, на предмет соответствия закону кодирования. Результаты проверки кодовых комбинаций преобразуются и поступают на вход элемента И 14, формируя импульс разрешения считывания информацни телесигнализации. Информация телесигнализации, поступающая на -й вход коммутатора 16, подается на вход блока 2 и на элемент И 12, записывается в регистр сдвига 8, проверяется и при отсутствии ощибок через элемент И 14 поступает на исполнительные элементы системы телеуправления. Информация телесигнализации, поступающая на (i + 1)-й вход коммутатора 16, подается на вход блока фазирования по такту 1 и на элемент И 9. Тактовая фаза запоминается блоком 1. После декодирования кодовой комбинации циклового фазирования импульсом с дешифратора 5 распределитель 3 запоминает цикловую фазу информации, поступающей по (i -f 1)-му входу.

Для переключения канала на управляющий, вход коммутатора 16 со входа 17 поступает импульс, который одновременно подается на

вторые входы элементов И 10 и 11. После пере1{лючения канала на вход блока фазирования 2 и на первый вход элемента И 12 подается информация телесигнализации (i + 1)-го канала, а тактовая и цикловая фазы, хранящиеся в блоках 1 и 3, через элементы И 10

и 1 переписываются в блоки 2 и 4, что обеспечивает немедленную после подключения канала регистрацию информации телесигнализации.

Таким образом, с приемом информации по

t-му входу одновременно производится установка начальной тактовой и цикловой фаз (i + })-го входа, и в момент переключения каналов тактовая и цикловая фазы этой информации устанавливаются на блоках 2 и 4 за счет ее переписывания из блоков I и 3.

Технико-экономическая эффективность предложенного устройства заключается в сокращении времени приема информации телесигнализации, что в целом повышает быстродействие устройства. Время приема информации телесигнализации от территориально рассредоточенных объектов связи состоит из времени фазирования по такту, времени ожидания поступления кодовой комбинации циклового фазирования, времени циклового фазирования и времени приема информации телесигнализации. При

оптимальном выборе числа кодовых комбинаций циклового фазирования для установления тактовой- и цикловой фаз устройства требуется от двух до 10 кодовых комбинаций. Цикл телесигнализации может состоять из двух и более кодовых комбинаций, поэтому выигращ во

времени приема информации составляет от 10 до 200% по сравнению с временем приема известных устройств.

Таким образом, использование предложенного устройства в системах телеуправления группы рассредоточенных объектов позволяет сократить время приема сигнализации об их состоянии, что повышает быстродействие системы.

Формула изобретения

Устройство для приема телесигналов, содержащее первьи блок фазирования,первый выход которого по.аключен ко входу первого распределителя, второй выход - к первому входу второго распределителя и к первому входу первого регистра сдвига, первый выход первого распределителя соединен с первым входом первого элемента И, выход которого подключен ко второму входу «ерБого регистра сдвига, второй выход первого распределителя соединен с первым входом анализатора кода, ко второму входу которого подключен выход второго распределителя, а к третьему входу - первый выход первого регистра сдвига, выходы анализатора кода соединены с первыми входами второго элемента И, ко второму входу которого подключен второй выход первого регистра сдвига, третий выход первого регистра сдвига через первый дешифратор соединен со вторым входом второго распределителя, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены коммутатор, первый и второй выходы которого подключены соответственно к i-му и (i + 1)-му информационным входам коммутатора, второй блок фазирований, третий распределитель, второй дешифратор, второй регистр сдвига, третий, четвертый и пятый элемеиты И; информационные входы коммутатора подключены ко входам устройства; первый выход коммутатора соединен со входом первого блока фазирования и со вторым входом первого элемента И; второй . выход коммутатора соединен со входом второго блока фазирования и с первым входом третьего элемента И,

ко второму входу которого подключен первый выход второго блока фазирования, а выход соединен с первым входом второго регистра сдвига, второй вход которого и первый вход третьего распределителя соединены со вторым выходом второго блока фазирования; выход второго регистра сдвига через второй дешифратор подключен ко второму входу третьего распределителя, выход которого соединен с оервым входом четвертого элемента Hi третий

выход второго, блока фазирования подключен к первому входу пятого элемента И, выход которого соединен со вторым входом первого блока фазироваиия; выход четвертого элемента И подключен к третьему входу Btoporo распределителя; управляюший вход устройства соединен со вторыми входами четвертого и пятого элементов И и со вторым входом коммутатора. Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1978-06-05—Публикация

1976-04-22—Подача