1

Изобретение относится к автоматике и передаче дифровых данных и может использоваться в иифОрмащионных системах для .отображеиия циф|ровой информации на (рассредоточеНных пунктах лриема.

Известны устройства для передачИ HI приема информации с временным уплотнением каналов связи. Для поддержания синхр-оинюсти и синфа.3ности передающих и приемных распределителей в них используются высокоста-бильные генераторы и сложные схемы поэлемеигной и цикловой синхронизации 1.

Изщ-естны также устройства для .приема ипформации, содержащие распределитель, выделптель си.,рон1ГЗирующего импульса, генератор импульсов, блок памяти и элементы И 2, а также устройство, в котором используется /непрерывный циклический огорос источник ощ информации 3. Однако в известных устройствах не производится обнаружение ошибок в .принимаемой ииформации, а приемные распределители должны иметь такое же количество элементов, как и передающие.

Известно также устройство для приема информации, осуществляющее последовательную обработку принятой информации и содержащее генератор импульсов, блок фазирования, преобразователь последовательного кода в параллельный, блок памяти, узел обнаружения ошибок, элементы сравнения и

элементы И 4. Однако это устройство громоздко в случае его технической реализации для приема большого объема передаваемых сообщений.

Наиболее близким к предлагаемому техническИМ решением -является устройство для приема информации с обнаружением ошибок, содержащее блок фазирования, первый вход которого и первый вход первого элемента И

соединены с входом устройства, лерв.ый выход блока фазирования нодключен к второму входу первого элемента И, выход которого соединен с входом дреобразователя последовательного кода в -параллельный, информационные выходы которого подключены к соответствующим входам блока памятн, разрешающие входы которого соединены с выходами информационных эле ментов И, лер-в-ые входы которых .подключены к выхода коммутатора, дешифратор и элементы ИЛИ и И 5.

Однако известное устройство не обеспечивает достаточной надежности приема при передаче на пункт большого чшсла сообщений.

Цель изобретения-повышение надежности приема больших объемов информации, поступающей с центрального пункта по одностороннему каналу связи.

Это достигается тем, что в предлагаемое

устройство введены двоичные счетчики групп

инфор.мации, и двоичные счетчики разрядов инфОрмацш, дополнительные элементы И, блок сравнения кодов и блок обнаружения ошибок, иервый выход которого подключен к второму (ВХОДУ блока фазирования и к управляющему входу блока памяти, второй выход соединен с вторы ги входами ииформационных элементов И, пе1рвый управляющий выход .преобразователя последовательмого кода в параллельный подключен к первому выходу блока обнаружения онгибок и к управляющим входам дешифратора и блока сра внения кодов, второй управляющий выход преобразователя последовательного кода в параллельный соединен со счетным входо1М двоичного счетчика разрядов информации, третий управляющий выход ссединен с первъкм входом второго элемента И и с вторым .входом блока обнаружения опгибок, четвертый управляющий выход .подключен к первому входу гретьего элемента И и к третьему входу блока обнаружения ошибок, второй выход блока фазирования подключен к четвертому входу блока обнаружения он1ибок, к входу сброса двоичного .счетчика блокоъ информации и к первому входу элемента ИЛИ, третий выход блока фазирования соединен с входом сброса дБОичного счетчика лрупп информации, выход третьего элемента И непосредственно и через двоичный счетчик групп ия.формаци-и соединен с еоответствующи.ми входами четвертого элемента И, выход второго элемента И непосредственно и через двоичный счетчик блоков информации Соединен с соответствующими входами .пятого элемента И, выходы двоичного счетчика групп информации, двоичного счетчика блоков информации и двоичного счетчика разрядов информа.ции подключены к входам коммутатора, информационные выходы преобразователя последовательного кода в параллельный, а также объединенные одноименные выходы четвертого и пятого элементов И подключены к соответствующим входам блока сравнения кодов, выход которого соединен с вторым входом элемента ИЛИ и пятым входом блока обнаружения ошибок, выход элемента ИЛИ подключен к входу сброса двоичного счетчика разрядов информации, выходы которого через дешифратор соединены соответств.енно с третьим входом блока фазирования и с вторыми входами второго и третьего элементов И. .

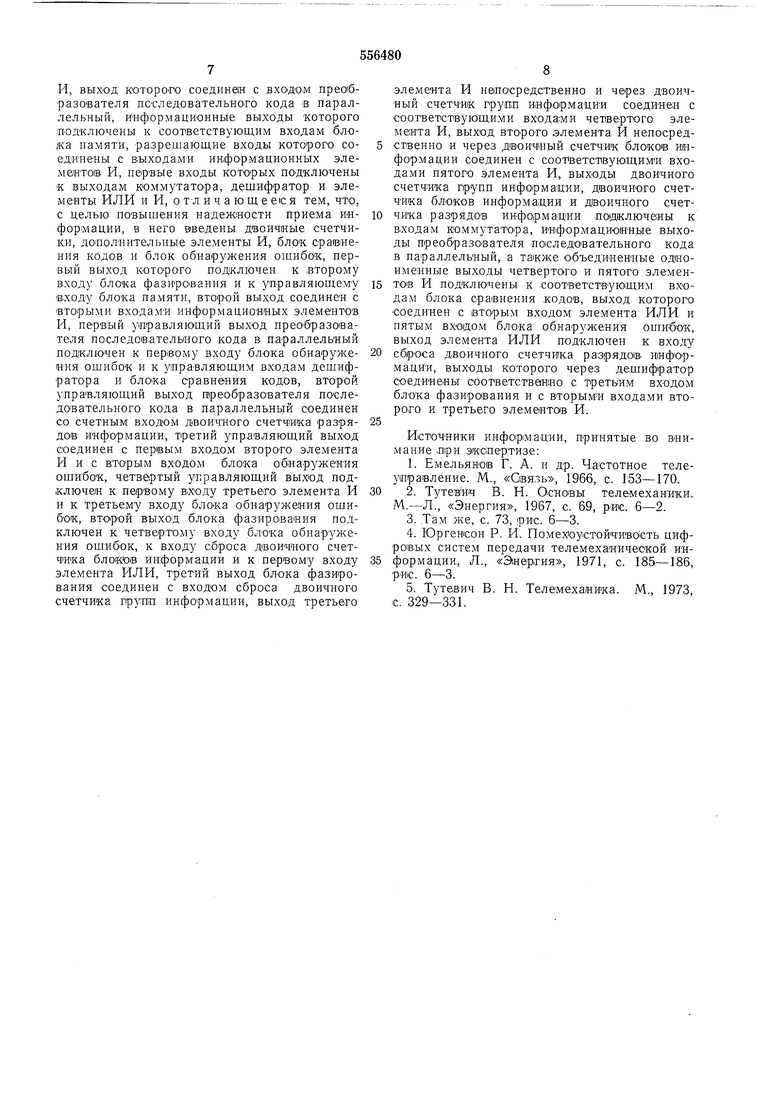

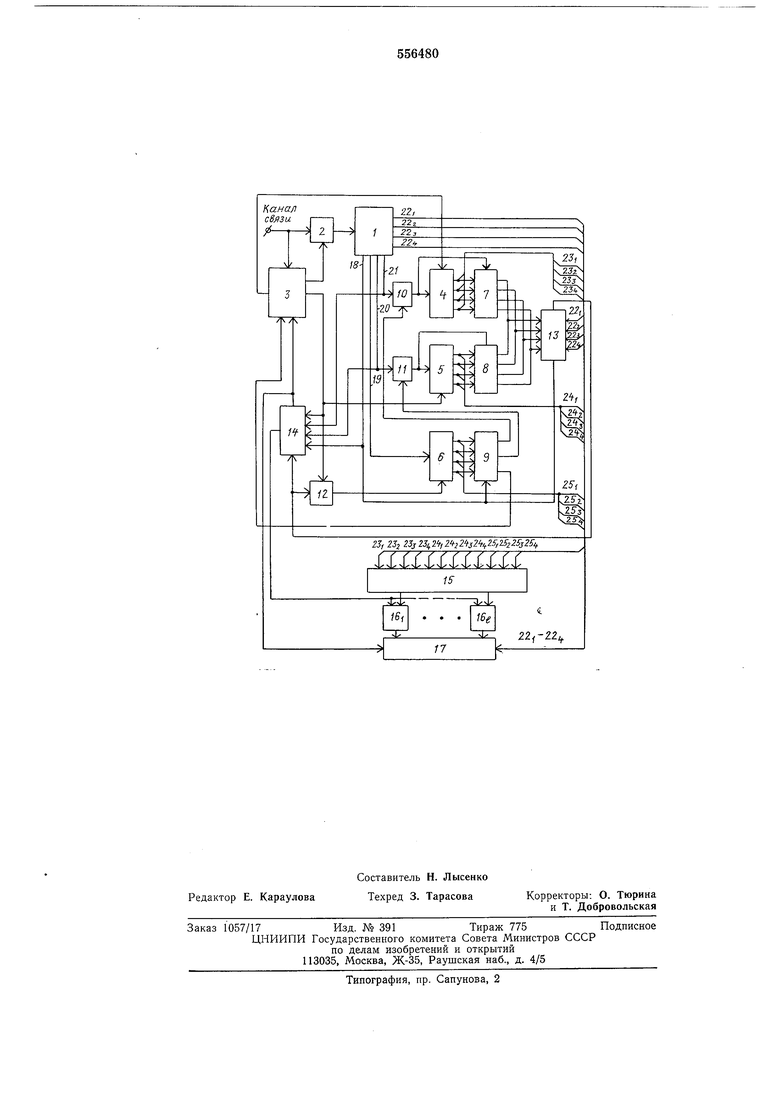

На чертеже .показана структурная схема пр е д л а г а о го ус тр о и ств а.

Устройство содержит преобразователь 1 последовательного кода в параллельный, элемент И 2, .блок 3 фазирования, двоичные счетчики групп информации, блоков информации, .разрядов информации 4, 5 и 6, элементы-И 7 и 8, дешифратор 9, элементы И 10 и II, элемент ИЛИ 12, блок 13 сравнения кодов., блок 14 обнаружения ошибок, ко;ммутатор ,15, информационные элементы И 16i- 16;, блок 17 памяти (18-21 - управляющие выходы преобразователя I; 22i-224 - его информационные выходы; 23i-23;; - кодовые выходы двоичного счетчика 4 лрунп информации; - кодовые выходы двоичного счетчика 5 блоков информации; 25i-264 - кодовые выходы двоичного счетчика 6 разрядов информации).

Работа устройства заключается в следующем.

На в-ход устройства по одностороинему каналу С1ВЯЗИ. поступает информация, содержащаяся в источниках информации, полный объем которых разбит на т грунп, каждая лртапа - на k .блоков, причем каждый ,блок содержит /разрядов (знаков). Весь объем информации, состоящий из m-ft-/ разрядов, передается последовательно, поразрядно в течение одного полного цикла в односторонний канал СВЕЗИ, при этом циклы .повторяются непрерывно. Скорость лередачи. о.пределяется

типом канала связи и допустимым временем ожидания. В одном .полном цикле на вход устройства поступает т адресных комбинаций .номеров груп.п, m-k адресных комбинаций номеров, блоков, т фазирующих ком;бинаций

«Начало цикла и одна фазирующая комбинация «Конец цикла. Все комбинации, .как информационные, так и адресные и фазирующие, передаются двОИчным семиэлементным кодом, например, старт-стопным способом.

Кодовая часть каждой комбинации состоит из четырех информационных элементов, двух элементов приз.нака группы или блока и. эле.мента дополнения до четности. К этим семи элементам добавляются фазирующие элемеиты-стартовый и стаповый.

В процессе передачи производится последовательный опрос разрядов первой грзпиы, затем второй и т. д. в порядке возрастания их номеров.

Иолный цикл передачи начинается передачей фазирующей комбинации «Номер цикла, например, состоящей из восьми «нулей, включая стартовый. По двухпроводной линии связи, соединяющей центральный пункт с

.пунктом приема, она поступает на вход блока 3 фазирования. Он подсчитывает количество «нулей, следующих один за др.угим, и если их поступит точно восемь подряд, выдает по одному выходу потенциальный сигнал, открывающий элемент И 2, а по друго-.му выходу - импульсный сигнал, устанавливающий в исходные состояния счетчик и 5 и 6. Счетчик 4 устанавливается в исходное состояние сигналом «Конец предыдущего цикла. Следующей

поступает комбинация номера первой группы, которая будет иметь вид «0010001. Здесь перв.ые четыре элемента, считая справа, представляют двоичное изображение десятичного числа «1, означающего .номер первой пруп.пы, а «единица пятого элемента несет .в себе пр.изнак того, что передаваемая комбинация является адресной и передается адрес группы. После приема преобразователем 1 этой комбинации на информационных выходах

22i-224 установится на время, равное длительности стоповой посььтки, комбинация «0001, cTaipTOBbift импульс с .выхода 19 зани.мает «едимицу в счетчике 6, а импулйс, соответствующий «едипице пятого элемента комбияации, с выхода 21 псступает иа в.ход элемента ,И 10. Декодирование состояний счетчика 6 осуществляется деш:ифратором 9. Проверка того, что после комбинации «начало цикла первой должна поступить ком-би ация номера группы, произ1водится соединением -первого выхода дешифратора 9 с вторым входом элемента И 10. Поэтому, если счетчик 6 находится в состоянии «0001, то элемент И 10 открыт и импульс с выхода 21 установит счетчик 4 .в состояние «0001, а также откроет элемент И 7.

Таким образом, на двух входов блока 13 сравнения кодов устаиа-вливаются кодовые комбИНации: «0001, действующая на выходах 22i-22, и «0001, дейст1вующая на выходах 23i-23л счетчика 4. Импульс, лодтверждаюишй четность принятой ком(бинации, с выхода 18 поступаетНа ст робирующий вход блока 13 сравнения кодов, который .проверяет идентичность кодов, и в случае их неидентичности на его выходе им:пуль1с не появляешься, благодагря чему блок 14 обнаружения ошибок вырабатывает сигнал «Отнибка, возвращающий блок 3 фазирования в исходное состояние, .при котором запрещен прием ком бданаций преобразователем 1. Если же коды идентичны и комбинация четная, преобразователь начинает .птием очередной комбинации, которая несет в себе номер первого блока первой группы и имеет вид «0100001. Здесь первые четыре элемента, считая справа, представляют двоичное изоб(ражение десятичного числа «1, означающего номер первого блока, а «единипа в шестом элементе означает признак номера блока. На выходах вновь з станавливается .комбинация «0001, в счетчик б добавляется «единица, сигналом с его второго выхода открывается элемент И 11 и с выхода 20 записывается «единица в счетЧИк 5, который устанавливается в состояние «0001. Блок 13 аравнения кодов проверяет, как и В .предыдущем случае, кодовое состояние счетчика 5 и код, поступающий по выходам 22i-22л. В случае идентиЧ1ности кодов на в.ыходе блока 13 сравнения кодов появляется импульс, подтверждающий верность приема этой адресной комбинации и через элемент ИЛИ 12 устанавливающий в исходное состояние Двои.чный счетчик 6. Вслед за этим начинают .поступать информационные комбинации разрядов первого блока первой группы, каждая из них проверяется на четность и по выходам 22,-224, передается в блок 17 памяти и сопровождается синхросигналом, вырабатываемым блоком 14 обнаружения ошибок.

После приема разрядов первого блока на вход преобразователя 1 комбинация номера второго блока «0100010. После ее пр.иема счетчик 6 устанавливается в (/+

-)-1)-е состояние (/ - количество разрядов в блоке). С (+1)-го выхода дешифратора 9 поступает сигнал, открывающий элемент И 11, благодаря чему с его выхода на вход двоичного счетчика 5 поступает имплльс, переводящий его в состояние «0010. После этого .блок 13 сравнения кодов сравнивает код на выходах 24i-244 счетчика 5 и код на выходах описанным порядком, после чего

вновь сбрасывается в исходное состояние Двоичный счетчик 5 и начинается прием разрядов второго блока и т. д.

После приема разрядов /г-го блока в первой группе поступает комбинация номера

втоПой группы, затем таким же порядком адресные и информапионные комбинации, относящиеся к этой группе.

С помощью коммутатора 15 производится выбор нужной ГРУППЫ и блока. Он

соединен с выходами двоичных счетчиков 4, 5 и 6 23,-23л, 24,-24д и 25,-25.,. В отрезки впемени. в течентуе которых принимаются комбинапии выбранного блока, поочередно, в порядке поступления разрядов этого блока, подготавливаются элементы И 16i-16-, а в моменты поступления на их .объединенные вторые входы синхросигнала в соответствуюнтие ячейки блока 17 памяти записываются .ния разрядов, поступающие по выходам 22,-

22....

После передачи всех / разрядов последнего fe-ro блока последней /тг-й грлппы передается (Ьязирующая кол бинания «Конец цикла. При на (/+П-М выходе дешифратора 9

должен появиться сигнал, разрешающий п.рием этой комбинании, состоящей, нанример. из восьлги «единиц, включая стоповую, блоком 3 фазирования. После ее приема устанавливается в исходное со-стояние двоичный счетчиж 4, а следующей за ней комбинацией «Начало цикла устанавливаются в исходные состояния двоичные счетчики 5 и 6, после чего продолжается аналогично работа в следующем цикле.

При обнаружении любой оигибки - в адресной или Ин.формациоН1ной комбинации - вход Бреобразов.ателя 1 закрьгвается сигнало М от блока 3 .фазирования, а блок 14 обнаружения о.шибоК выдает сигнал стирания, по

которому стирается информация в блоке 17 памяти.

В предлагаемом з стройстве улучшены экономические и эксплуатационные .характеристики; при использовании устройства упрощаются каналы связи, повыщаются до.стоверность приема информации и мобильность устройства.

Формула изобретения

Устройство для приема информации с обнаружением ошибок, содержащее блок фазирования, первый вход которого и первый вход первого элемента .И соединены с входом устройства, первый выход блока фазирования

подключен к второму входу первого элемента

:И, ВЫХОД которОГО соединан с входом преобразователя псследовательного кода в параллельный, информационные выходы которого .подключены к соответствующим входам блока памяти, разрешающие входы которого соединены с выходами информационных элементов И, парвые входы которых подключены « выходам коммутатора, дешифратор и элементы ИЛИ и И, о тЛ и ч а ю щ е ее я тем, что, с целью повышения надежиости приема и«формации, в него эведены двоичные счетчики, дополнительные элементы И, блок сравнения кодов и блок обнаружения ошибок, первый выход которого под/ключей к второму входу блока фазирования и к управляющему ВХоду блока памяти, второй выход соединен с вторыми входами информационных элементов И, первый управляющий выход преобразователя последовательного кода в параллельный подключен к первому входу блока обнаружения ошибок и к управляющим входам дешифратора и блока сравнения кодов, второй управляющий В.ЫХОД преобразователя последовательного кода в параллельный соединен со счетным входом двоичного счетчика разрядов информации, третий управляющий выход соедннен с первым входом второго элемента И и с вторым входом блока обнаружения ощибок, четвертый управляющий выход подключен к первому вжоду третьего элемента И и к третьему входу бло-ка обнаружения ошибок, второй выход блока фазнрования подключен к четвертому входу блока обнаружения ошибок, к входу сброса двоичного счетчика блоков информации и к первому входу элемента ИЛИ, третий выход блока фазирования соединен с входом сброса двоичного счетчика групп информации, выход третьего

элемента И непосредственно и через двоичный счетчик групп информации соединен с соответствующими входами четвертого элемента И, выход второго элемента И непосредственно и через двоич ный счетчик блоков информации соединен с соответствующими входами пятого элемента И, выходы двоичного счетчика групп информации, двоичного счетчика блоков информации и дйоичного счетчика разрядов информации подключены к в.ходам коммутатора, информационные выходы преобразователя последовательного кода в параллельный, а также объединенные одноименные выходы четвертого и пятого элементов И подключены к соответствующим входам блока сравнения кодов, выход которого соединен с вторым входом элемента ИЛИ и пятым входом блока обнарул ения ошибок, выход элемента ИЛИ подключен к входу

сброса двоичного счетчи1ка разрядов, информации, выходы которого через дешифратор соединены соответственно с третьим входом блока фазиро)вания и с вторыми входами второго и третьего элементов И.

Источники иифор1мации, принятые во внимание .при экспертизе:

1. Емельянов Г. А. и др. Частотное телеуправление. М., «Связь, 1966, с. 163-170.

2. Тзтевич В. Н. Основы телемеханики. М.-Л., «Энергия, 1967, с. 69, рис. 6-2.

3.Там же, с. 73, рис. 6-3.

4.Юргеисон Р. И. Помех1оустойчиво;сть цифров.ых систем передачи телемеханической информации. Л., «Энергия, 1971, с. 185-186, рис. 6-3.

5.Тутевич В. Н. Телемеханика. М., 1973, €. 329-331.

23, 23s23 2t,Zt22t32 2Sf2S22S3252f

Jx six si N1 Jx six six sLx Jx six NJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора передачи и приема информации | 1975 |

|

SU550666A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ БЛОКОВ ИНФОРМАЦИИ | 2003 |

|

RU2249920C2 |

| Устройство для синхронизации биимпульсного сигнала | 1985 |

|

SU1350837A1 |

| Устройство для обнаружения ошибок | 1974 |

|

SU517173A1 |

| Устройство для передачи и приема самосинхронизирующихся кодограмм | 1986 |

|

SU1403379A1 |

| Устройство для обнаружения ошибок | 1980 |

|

SU932636A2 |

| Устройство для кодирования и декодирования циклических кодов | 1985 |

|

SU1302440A1 |

| Устройство фазирования по циклам вСиСТЕМЕ пЕРЕдАчи дАННыХ | 1979 |

|

SU813809A1 |

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

| Устройство для сбора, передачи и приема информации | 1977 |

|

SU690527A1 |

1Б€

17

Авторы

Даты

1977-04-30—Публикация

1975-06-23—Подача