(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля матриц памяти | 1980 |

|

SU898507A1 |

| Устройство для контроля матриц памяти | 1982 |

|

SU1027780A2 |

| Устройство для контроля памяти | 1977 |

|

SU698056A1 |

| Устройство для контроля памяти | 1978 |

|

SU765884A1 |

| Устройство для регистрации динамических процессов | 1988 |

|

SU1624437A1 |

| Устройство для контроля блоковОпЕРАТиВНОй пАМяТи | 1979 |

|

SU824317A1 |

| Устройство для диагностирования телевизионной аппаратуры | 1983 |

|

SU1124330A1 |

| Устройство для контроля блоков оперативной памяти | 1985 |

|

SU1348912A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1411809A1 |

| Устройство контроля качества датчиков времени | 1986 |

|

SU1422218A1 |

1

Изобретение относится к запоминаю.щим устройствам.

Известны устройства для контроля блоков памяти, содержащие схему форМ1фования растра, формгфователи управ.ляющих сигналов, схему гоавненич р..

Однако устройство не обеспечивает автоматизированного -выявления взаимного влияния ячеек памяти.

Наиболее близким техническим решением к предлагаемому является устройство для контроля блоков памяти, содержащее генератор кодов адреса, соединенный с блоком управления, формирователем координатной сетки и телевизионным приемником, блок утфавления соединен с компаратором, выход которого через смеситель оединен с телевизионным приемником, причем второй вход смесителя подключен к выходу генератора координатной сетки 2l.

Недостаток устройства состоит в низ- кой эффективности контроля, обусловленНОЙ недостаточной надежностью выявления, одиночных сбоев.

Цель изобретения - повышение достоверности контроля за счет надежного выявления одиночных сбоев.

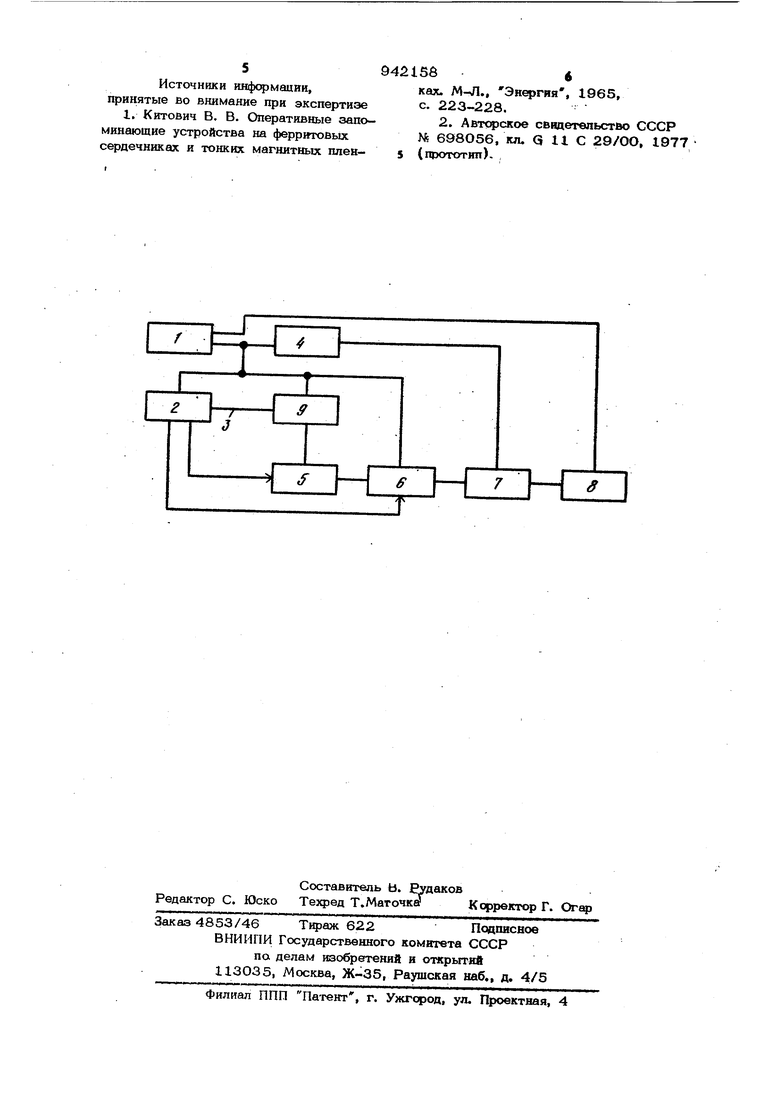

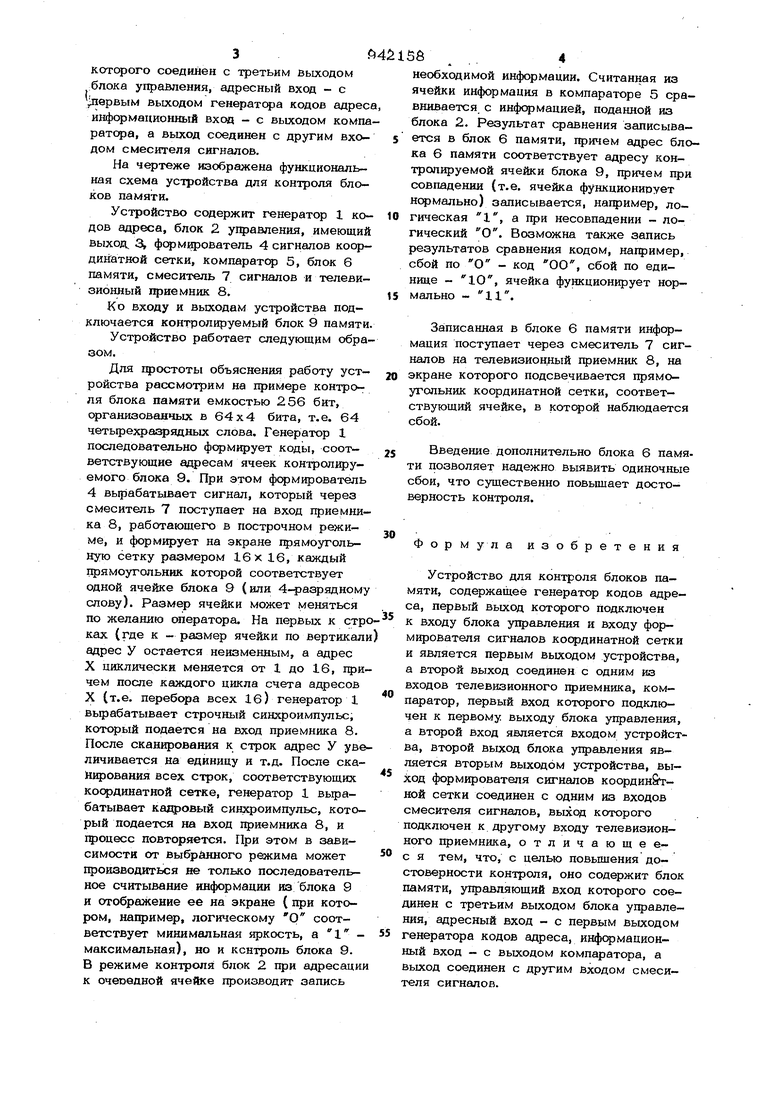

Поставленная цель достигается тем, что в устройство для контроля блоков памяти, содержащее генератор кодов адреса, первый выход которого подключен к входу блока утфавления и входу ф(рМ1фователя сигналов координатной сетки и является первым выходом устройства, а второй выход соединен с одним из входов телевизионного приемника, компаратор, первый вход которого под-. ключей к первому выходу блока управления, а второй вход является входом устройства, второй выход блока управления является вторым выходом устройства, выход фс мкрователя сигналов координатной сетки соединен с одним из входов смесителя сигналов, выход которого подключен к другому входу телевизионного приемника, введен блок памяти, управляющий вход которого соединен с третьим выходом блока управления, адресный вход - с врвым выходом генератсра кодов адрес информационш 1й Вход - с выходом компа ратора, а выход соединен с другим входом смесителя сигналов. На чертеже изображена функциональная схема устройства для контроля блоков памяти. Устройство содержит генератор 1 кодов адреса, блок 2 управления, имеющий выхоя 3, фсрмирователь 4 сигналов координатной сетки, компаратор 5, блок 6 памяти, смеситель 7 сигналов и телевизионный приемник 8. Ко входу и выходам устройства подключается контролируемый блок 9 памяти Устройство работает следующим обра зом. Для щэостоты объяснения работу устройства рассмотрим на примере контроля блока памяти емкостью 256 бит, органиаованчьис в 64x4 бита, т.е. 64 четьфехразрядных слова. Генератор 1 последовательно формирует коды, соответствующие адресам ячеек контролируемого блока 9. При этом формирователь 4 вырабатывает сигнал, который через смеситель 7 поступает на вход приемника 8, работающего в построчном режиме, и формирует на экране прямоугольную сетку размером 16 х 16, каждый прямоугольник которой соответствует одной ячейке блока 9 (или 4-разрядному слову). Размер ячейки может меняться по желанию оператора. На первых к стр ках (где к - размер ячейки по вертикал адрес У остается неизменным, а адрес X циклически меняется от 1 до 16, при чем после каждого цикла счета адресов X (т.е. перебора всех 1б) генератор 1 вырабатывает строчный синхроимпульс, подается на вход приемника 8. После сканирования к строк адрес У уве личивается на единицу и т.д. После скайирования всех строк, соответствующих координатной сетке, генератор 1 вырабатывает кадровый синхроимпульс, который подается на вход приемника 8, и iponecc повторяется. При этом в зависимости от выбранного режима может производиться не только последовательное считывание информации из блока 9 и отображение ее на экране ( при котором, например, логическому О соответствует минимальная яркость, а 1 максимальная), но и контроль блока 9. В режиме контроля блок 2 при адресаци к очеоедной ячейке производит запись необходимой информации. Считанная из ячейки информация в компараторе 5 сравнивается с информацией, поданной из блока 2. Результат сравнения записывается в блок 6 памяти, причем адрес блока 6 памяти соответствует адресу контролируемой ячейки блока 9, причем при совпадении (т.е. ячейка функциониоует нормально) записывается, нащзимер, логическая 1, а при несовпадении - логический О. Возможна также запись результатов сравнения кодом, нахфимер, сбой по О - код ОО, сбой по единице - Ю, ячейка функционирует нормально - 11. Записанная в блоке 6 памяти информация поступает через смеситель 7 сигналов на телевизионный приемник 8, на экране которого подсвечивается прямоугольник координатной сетки, соответствующий ячейке, в наблюдается сбой. Введение дополнительно блока 6 памяти позволяет надежно выявить одиночные сбои, что существенно повьщ1ает достоверность контроля. Форм у л а изобретения Устройство для контроля блоков памяти, содержащее генератор кодов адреса, первый выход которого подключен к входу блока управления и входу формирователя сигналов координатной сетки и является первым выходом устройства, а второй выход соединен с одним из входов телевизионного гфиемника, компаратор, первый вход которого подключен к первому выходу блока управления, а второй вход является входом устройства. Второй Выход блока управления является Вторым выходом устройства, вьг- ход формирователя сигналов коордкнижной сетки соединен с одним из входов смесителя сигналов, выход которого подключен к другому входу телевизионного приемника, отличающеес я тем, что, с целью повыщения достоверности контроля, оно содержит блок памяти, управляющий вход которого соединен с третьим выходом блока управления, адресный вход - с первым выходом генератора кодов адреса, информационный вход - с выходом компаратора, а выход соединен с другим входом смесителя сигналов.

Источники информации, принятые во внимание при экспертизе

ках. ., Энергия, 1965, с. 223-228.

Авторы

Даты

1982-07-07—Публикация

1980-07-23—Подача