Изобретение относится к запомина щим устройствам. Известно устройство, содержащее устройство управления, адресное уст ройство, блок памяти, формирователь эталонной информации, входной 5)егис числа, схему сравнения, устройство индикации JYJ . Недостатком этого устройства явл ется низкое быстродействие. Наиболее близким техническим реше нием к данному изобретению является устройство, содержащее формирователь кодов адресов, формирователь сигналов координатной сетки, блок управления, схему сравнения, смеситель и телевизионный приемник 2 Недостатком этого устройства явля ется низкое быстродействие контроля при определении области устойчивой, работы контролируемого оперативного запоминающего устройства (ОЗУ) и отсутствие возможности контроля хранения информации при аварийном отключе нии и последующем включении питания ОЗУ. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем .что в устройство для контроля блоков оперативной- памяти, содержащее блок управления, формирователь сигналов координатной сетки, формирователь кодов адресов и схему сравнения,причем первый и второй выходы блока управленкя подключены соответственно к первому выходу устройства и ко входу формирователя сигналов координатной сетки, выход которого соединен со вторым выходом устройства, первый и второй входы схемы сравнения подключены соответственно к выходу формирователя кодов адресов и третьему выходу устройства и ко входу устройства, введены блок местного управления, преобразователь код-напряжение, формирователь сигналов сбоя, формирователь сигналов обращения и формирователь эталонных сигналов, причем первый и второй входы и выход блока местного управления подключены соответственно к выходу формирователя сигналов сбоя, к первому выходу и к первому входу блока управления, входы формирователя сигналов сбоя соединены соответственно с первым входом схемы сравнения, со вторым входом блока управления и выходом схемы, сравнения и с выходом формирователя сигналов координатной сетки, вход форглирователя эталонных сигналов подключен к третьему выходу блока управления, а выход - ко входу формирователя кодов адресов, вход формирователя сигналов обращения соединен с четвертым выходом блока управления, а выход - с четвертым выходом устройства, вход и выход преобразователя код-напряжение подключены соответственно ко второму и к пятому выходам устройства. При этом блок местного управления целесообразно выполнить содержащим два элемента И-НЕ, три элемента задержки, два триггера и счетчик,причем выход первого элемента И-НЕ соединен со входом первого элемента задержки , а первый вход - со входом второго элемента задержки, входом счетчика и инверсным выходом первого триггера, входы которого соединены соответственно с выходами первого и второго элементов задержки, выход счетчика подключен к первому входу второго триггера, прямой и инверсный выходы которого соединены соответственно с первым входом второго элемента И-НЕ и со входом третьего элемента задержки, выход которого подключен ко второму входу второго элемента И-НЕ, вторые входы первого элемента И-НЕ и второго триггера -и выход второго элемента И-НЕ являются соответственно первым и вторым входами и выходом блока местного управления.

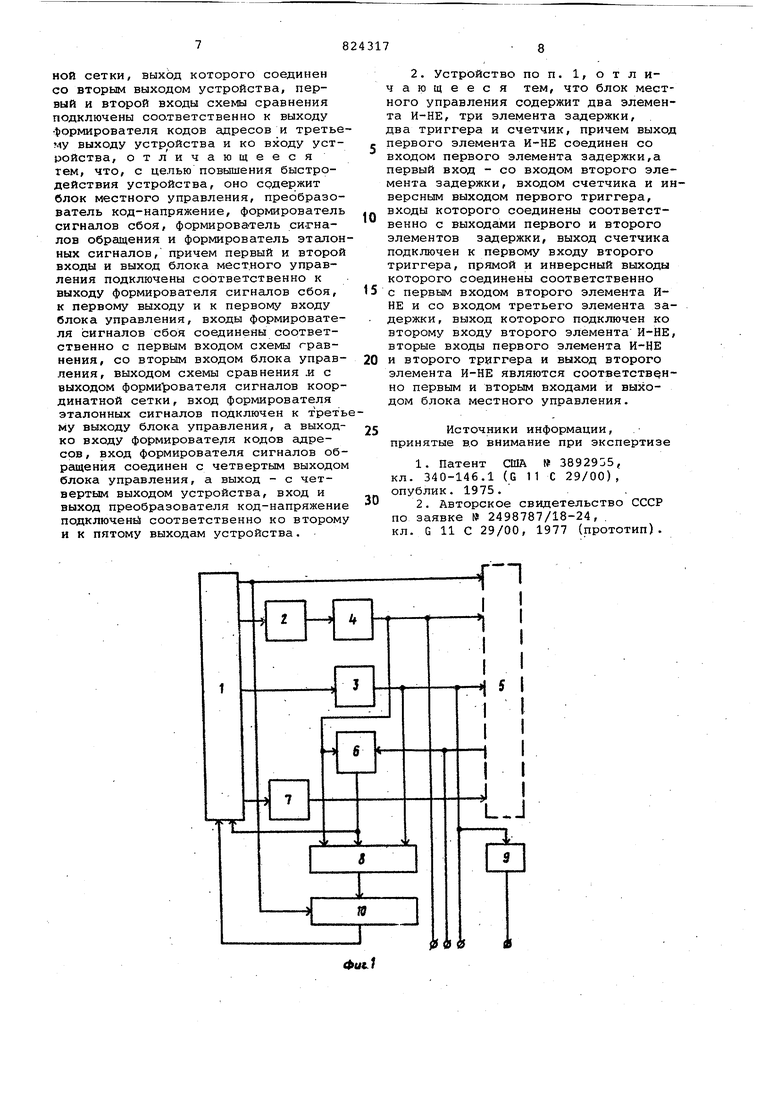

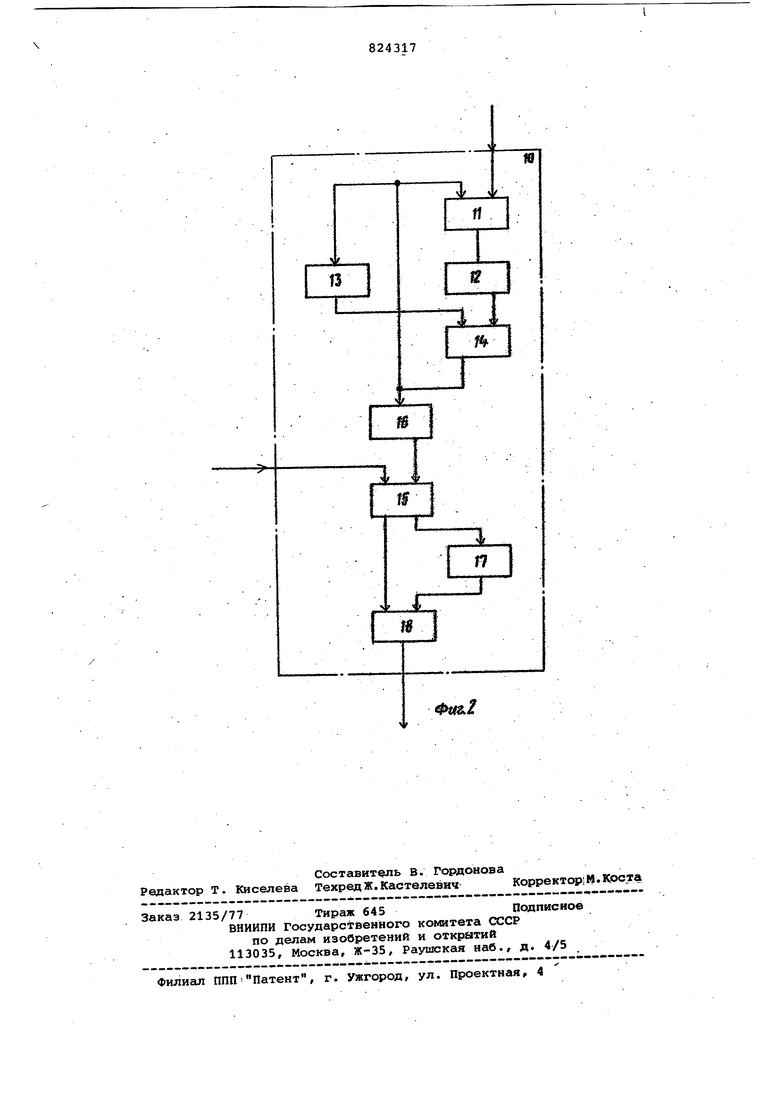

На фиг. 1 изображена функциональная.схема предлагаемого устройства; на фиг. 2 - функциональная схема блока местного управления.

Устройство (фиг. 1) содержит блок 1 управления, формирователь 2 эталонных сигналов, формирователь 3 сигналов координатной сетки, формирователь 4 кодов адресов, контролируемый блок 5 оперативной памяти.Устройство для контроля блоков оперативной памяти содержит также схему6 сравнения, формирователь 7 сигналов обращения, формирователь 8 сигналов сбоя, преобразователь 9 код-напряжение и блок 10 местного управления.

Первый и второй входы блока 1 управления подключены соответственно к первому выходу устройства и ко входу формирователя 3 сигналов координатной сетки, выход которого соединен со вторым выходом устройства. Первый и второй входы схемы б сравнения подключены соответственно к выходу формирователя 4 кодов адресов и третьему выходу устройства и ко входу устройства.

Первый и второй входы и выход блока 10 местного управления подключены соответственно к выходу формирователя 8 сигналов сбоя, к первому выходу и к первому входу блока 1 управления Входы формирователя 8 сигналов сбоя соединены соответственно с первым входом схемы б сравнений, со вторым

входом блока 1 управления, выходом схемы 6 сравнения и с выходом формирователя 3 сигналов координатной сетки . Вход формирователя 2 эталонных сигналов подключен к третьему выходу .блока 1 управления, а выход - ко входу формирователя 4 кодов адресов. Вход формирователя 7 сигналов обращения соединен с четвертым выходом блока 1 управления, а выход - с четвертым выходом устройства. Вход и выход преобразователя 9 код-напряжение подключены соответственно ко второму и к пятому входам устройства.

Первый, второй , третий и четвертый выходы и вход устройства подключаются соответственно ко входам и выходу контролируемого блока 5 оперативной памяти. Второй выход, третий выход и вход и пятый выход устройства подключаются соответственно ко входу синхронизации, ко входам 2 и входу у осциллографа (на фиг не показано).

Блок 10 местного управления содер жит (фиг.2) первый элемент 11 И-НЕ, первый 12 и второй 13 элементы задержки, первый 14 и в.торой 15 триггеры, счетчик 16, третий элемент 17 задержки и второй элемент 18 И-НЕ.

Выход первого элемента 11 И-НЕ соединен со входом первого элемента 12 задержки, а первый вход - со входом второго элемента 13 задержки, входом счетчика 16 и инверсным входом первого триггера 14., входы которого соединены соответственно с выходами первого 12 и второго 13 элементов задержки..

Выход счетчика 16 подключен к первому входу второго.триггера 15, прямой и инверсный выходы которого соединены соответственно с первым входом второго элемента 18 И-НЕ и со входом третьего элемента 17 задержки вы.ход которого подключен ко второму входу второго элемента 18 И-НЕ. Вторые входы первого элемента И-НЕ и второго триггера 15 и выход второго элемента И-НЕ 18 являются соответственно первым и вторым входами и выходом блока местного управления.

Устройство работает следующим образом. ..

Блок 10 местного управления вырабатывает команду Запуск, которая периодически, без вмешательства оператора, запускает устройство после прерывания его. работы, вызванного появлением сбоя.

Принцип автоматической выработки сигнала Запуск в блоке 10 местного управления (фиг. 1) состоит в задержке сигнала Сбой, подаваемого с выхода схемы б сравнения на время t 0,5-5 с и формировании одиночного импульса синхронно с тактовыми

сигналами, приходящими с первого выхода блока 1 управления. Управляя длительностью сигнала Запуск, мрж осуществить автоматический переход устройства к контролю всех последую щих адресов или перевести устройств на время t п 1 мс в режим работы без фиксации одиночного сбоя, чтобы преодолеть переходные процессы в ис точниках питания и в неисправном контролируемом блоке памяти или осуществить пропуск большого массив неисправных адресов. Рассмотрим режим контроля блока 5 оперативной памяти. При помощи формирователя 2 эталонных сигналов и формирователя 4 кодов адресов задается любая тест вая программа (тяжелый код, шахматный порядок, доисдь, бегающая единица и т.д.) . Программа под ется на третий вход контролируемого блока 5 оперативной памяти; одновре менно на другие входы которого пода ется переменный сигнал Запись-Считывание (например, Запись -, Считывание -0) с выхода формирова теля 7 сигналов обращения и код адреса - с выхода формирователя 3 сигналов координатной сетки. При по ключении ко входу Z осциллографа си нала с выхода формирователя 4 кодов адресов на экране наблюдается качес венная структура эталонной тестовой программы. При отсутствии -сбоев хра нимая в блоке 5 оперативной памяти программа во время действия.сигнала Считывание совпгщает с эталонной и схема б сравнения подает на вход блока 1 управления команду Работа (например, логическая 1). Эта команда запускает формирователь 8 сиг налов сбоя, который выключает блок 10 местного управления. ПрИпоявлений одиночного сбоя с выхода схемы б сравнения на второй вход блока I управления и вход формирователя 8 сигналов сбоя поступает сигнал Сбой (например, одиночный импульс).который прерывает работу устройства для контроля блоков. .Адрес сбоя и информации о неисправном разряде поступает в формирователь 8 сигналов сбоя, сигнал Сбой с выхода которого формирует в блоке 10 местного управления сигнал Запуск . Если сбой случайный, то по истечении времени t 0,5-5 с после (сигнала Запуск устройство перехошит к контролю всех последующих адресов . Рассмотрим режим контроля при определении области устойчивой работы блока оперативной памяти. При изменении питающих напряжений на границах допустимых зон появляется постоянный сбой. Адрес сбоя и информация о неисправном разряде фиксируется формирователем 8 сигналов сбоя. Блок |10 местного управления с заданным 1периодом (например, Т п 1 с) подает на входблока 1 управления сигнал Запуск до тех пор, пока значения питающих напряжений не окажутся в доп стимых пределах. При помощи формирователя 3 сигналов координатной сетки выбирается любой массив, необходимый для исследования, из общегоинформационного объема блока5 оперативной памяти. В режиме контроля хранения информации при аварийном отключении питания блока 5 .оперативной памяти с выхрд-а формирователя 7 сигналов обращения подается признак Запись (например , логическая 1), и при помощи формирователя 2 эталонных сигналов и формирователя 4 кодов адресов задается любая тестовая программа, качественная структура которой контролируется по осциллографу. . После записи программы с выхода формирователя 7 сигналов о.бращения подается признак Считывание (например,- логический О ).. После аварийного отключения и последугацего включения питания записанная программа контролируется формирователем 8 сигналов сбоя на экране осциллографа. При появлении одиночного сбоя в формирователе 8 сигналов сбоя фиксируется адрес сбоя и неисправный разряд, затем блок 10 местного управления с заданным периодом запускает блок 1 управления. Для качественного исследования сбоя период запуска увеличи-: вается или блок 10 местного управления и схема б сравнения выключается. Формирователь 3 сигналов координатной сетки фиксирует адрес сбоя и на экране осциллографа наблюдается строка с дефектом. , Технико-экономическое преимущество предлагаемого- изобретения заключается в его высоком быстродействии, остигаемом за счет введения автоматического запуска устройства после прерывания его работы, вызванного, появлением сбоя в контролируемом блоке оперативной памяти, и таким образом сключения ручных операций при опрет елении областей устойчивой работы лока оперативной памяти при колебаиях напряжения питания и при контоле хранения информации после аваийного выключения напряжения питаия. - Формула изобретения 1. Устройство для контроля блоков перативной памяти, содержащее блок правления, формирователь сигналов оординатной сетки, формирователь одов адресов и схему сравнения,прием первый и второй выходы блока правления подключены соответственно первому выходу устройства и ко вхоУ Формирователя сигналов KOOpjlwHarной сетки, выход которого соединен со вторым выходом устройства, первый и второй входы схемы сравнения подключены соответственно к выходу формирователя кодов адресов и третьему выходу устройства и ко входу устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит блок местного управления, преобразователь код-напряжение, формирователь сигналов сбоя, формирователь сигналов обращения и формирователь эталонных сигналов, причем первый и второй входы и выход блока местного управления подключены соответственно к выходу формирователя сигналов сбоя, к первому выходу и к первому входу блока управления, входы формирователя сигналов сбоя соединены соответственно с первым входом схемы гравнения, со вторым входом блока управления, выходом схемы сравнения .и с выходом форми эователя сигналов координатной сетки, вход формирователя эталонных сигналов подключен к третьму выходу блока управления, а выходко входу формирователя кодов адресов, вход формирователя сигналов обреицения соединен с четвертым выходом блока управления, а выход - с четвертым выходом устройства, вход и выход преобразователя код-напряжение подключен соответственно ко второму и к пятому выходам устройства.

2. Устройство по п. 1, отличающееся тем, что блок местного управления содержит два элемента И-НЕ, три элемента задержки, два триггера и счетчик, причем выход первого элемента И-НЕ соединен со входом первого элемента задержки,а первый вход - со входом второго элемента задержки, входом счетчика и инверсным выходом первого триггера, входы которого соединены соответственно с выходами первого и второго элементов задержки, выход счетчика подключен к первому входу второго триггера, прямой и инверсный выходы которого соединены соответственно с первым входом второго элемента ИНЕ и со входом третьего элемента задержки, выход которого подключен ко второму входу второго элемента И-НЕ, вторые входы первого элемента И-НЕ и второго триггера и выход второго элемента И-НЕ являются соответств нно первым и вторым входами и выходом блока местного управления.

Источники информации,

принятые в.о внимание при экспертизе

1. Патент США 38929j5, кл. 340-146.1 (G 11 С 29/00), опублик. 1975.

2. Авторское свидетельство СССР по заявке № 2498787/18-24, . кл. G 11 С 29/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной памяти | 1985 |

|

SU1348912A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля матриц памяти | 1982 |

|

SU1027780A2 |

| Устройство для контроля матриц памяти | 1980 |

|

SU898507A1 |

| Устройство для контроля памяти | 1978 |

|

SU765884A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для контроля блоков памяти | 1980 |

|

SU862239A1 |

| Устройство для управления виртуальной памятью | 1986 |

|

SU1327113A2 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957278A1 |

Авторы

Даты

1981-04-23—Публикация

1979-06-11—Подача