Изобретение относится к вычислительной технике и может быть использовано для контроля работоспособности блоков оперативной памяти.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения режима визуального наблюдения результатов контроля по всем адресам много- разрядных блоков памяти.

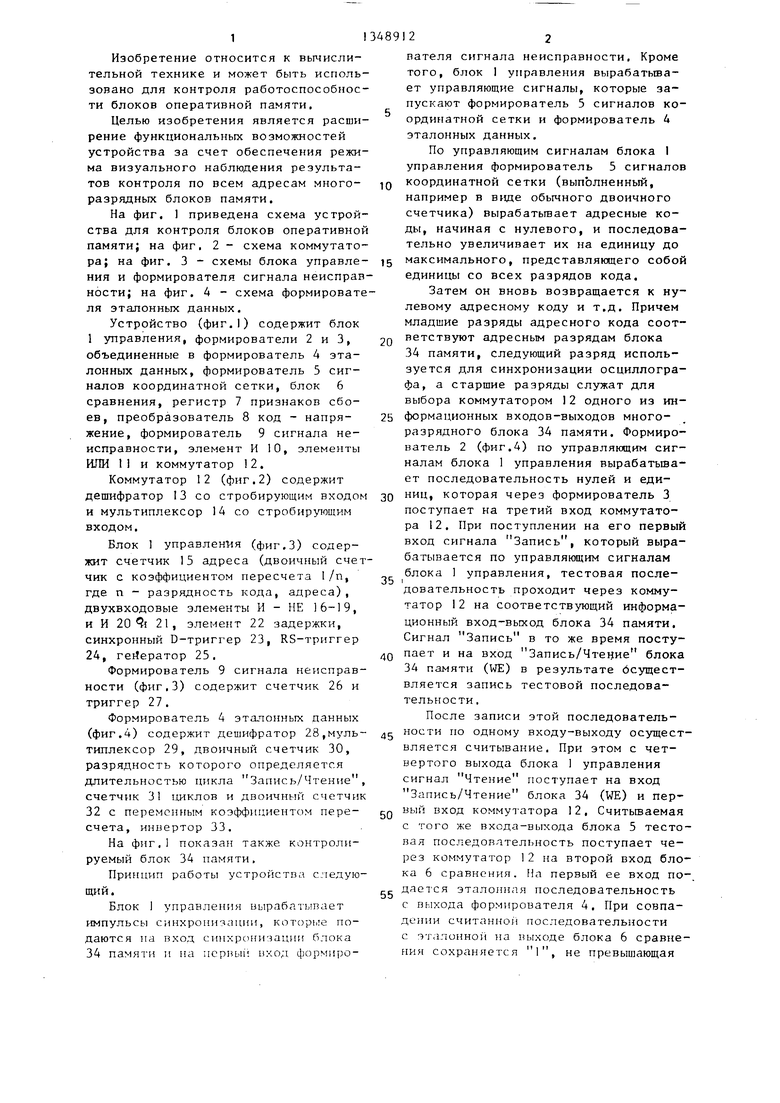

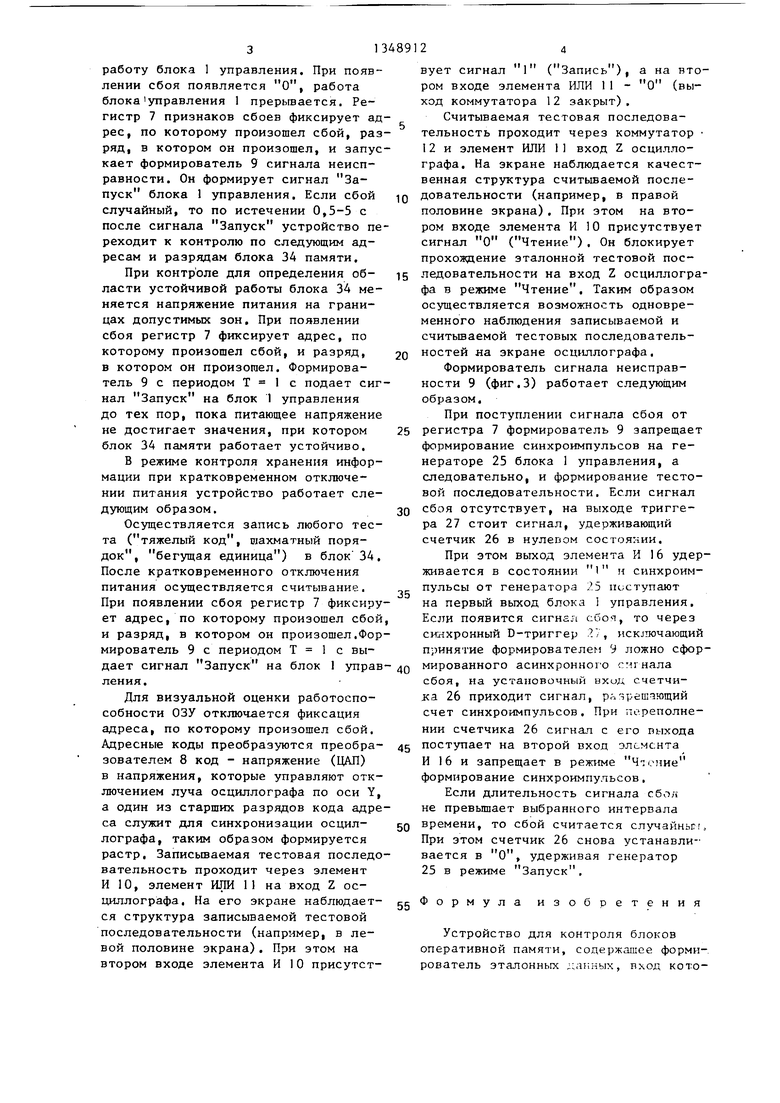

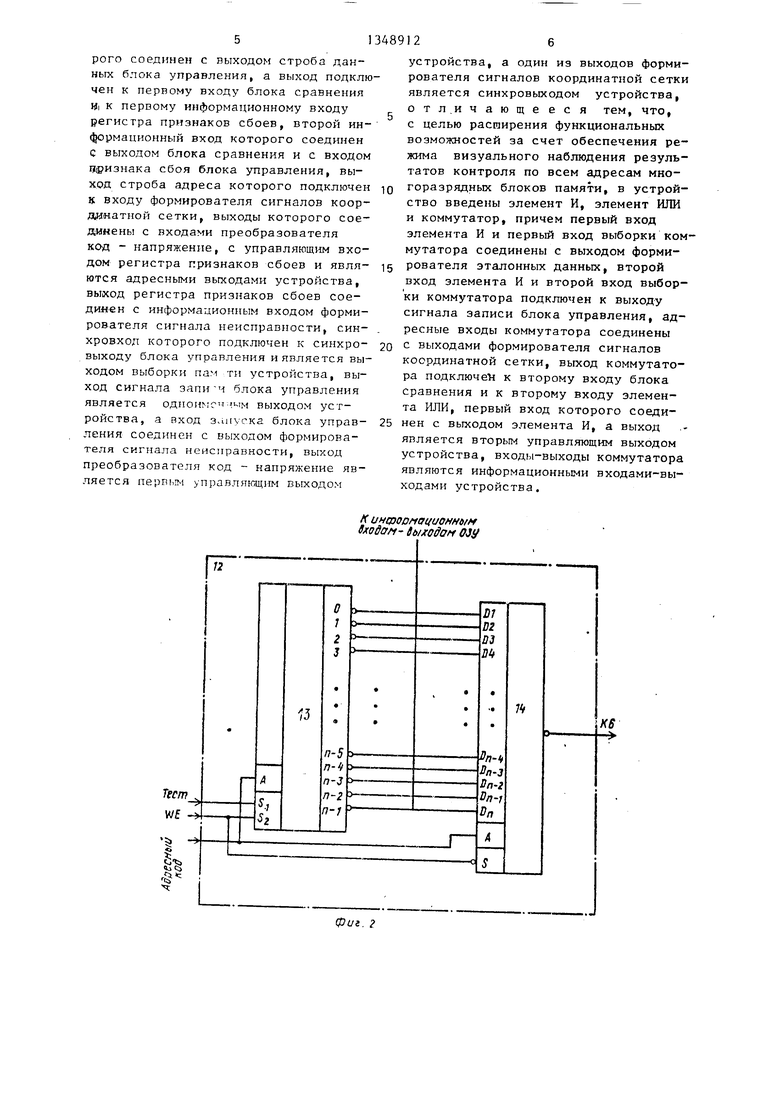

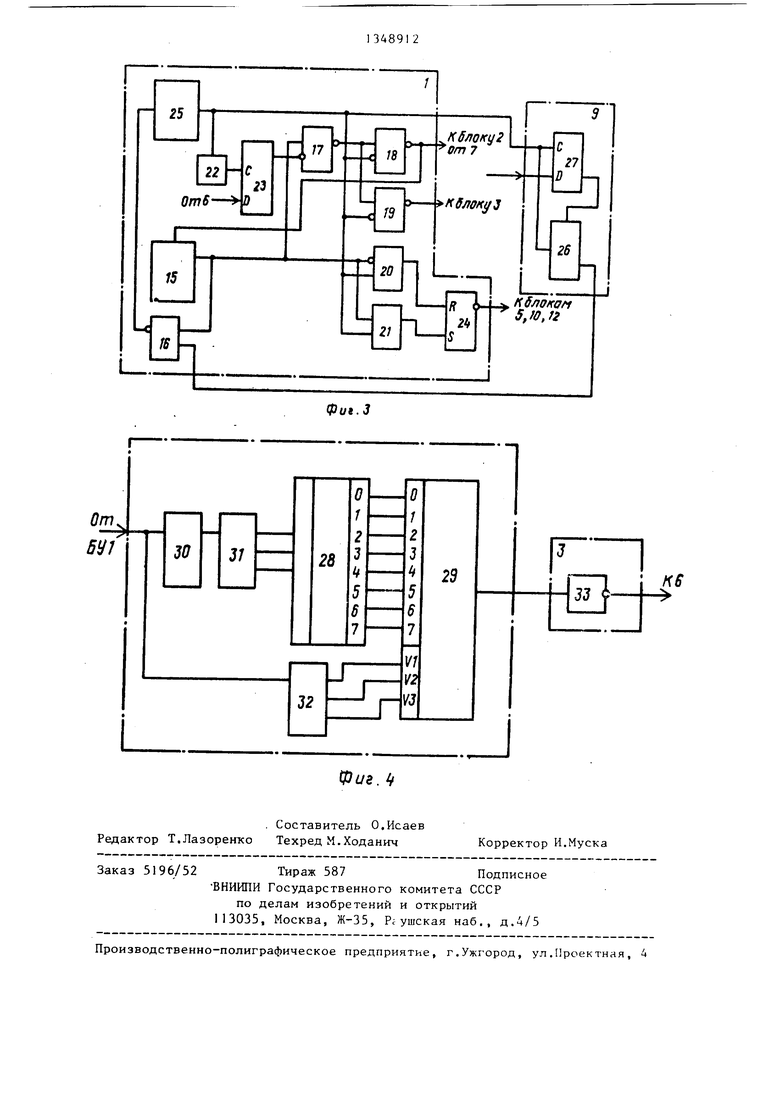

На фиг, 1 приведена схема устройства для контроля блоков оперативной памяти; на фиг, 2 - схема коммутатора; на фиг. 3 - схемы блока управле- ния и формирователя сигнала неисправности; на фиг. А - схема формирователя эталонных данных.

Устройство (фиг,1) содержит блок 1 управления, формирователи 2 и 3, объединенные в формирователь А эталонных данных, формирователь 5 сигналов координатной сетки, блок 6 сравнения, регистр 7 признаков сбоев, преобразователь 8 код - напря- жение, формирователь 9 сигнала неисправности, элемент И 10, элементы ИЛИ 11 и коммутатор 12.

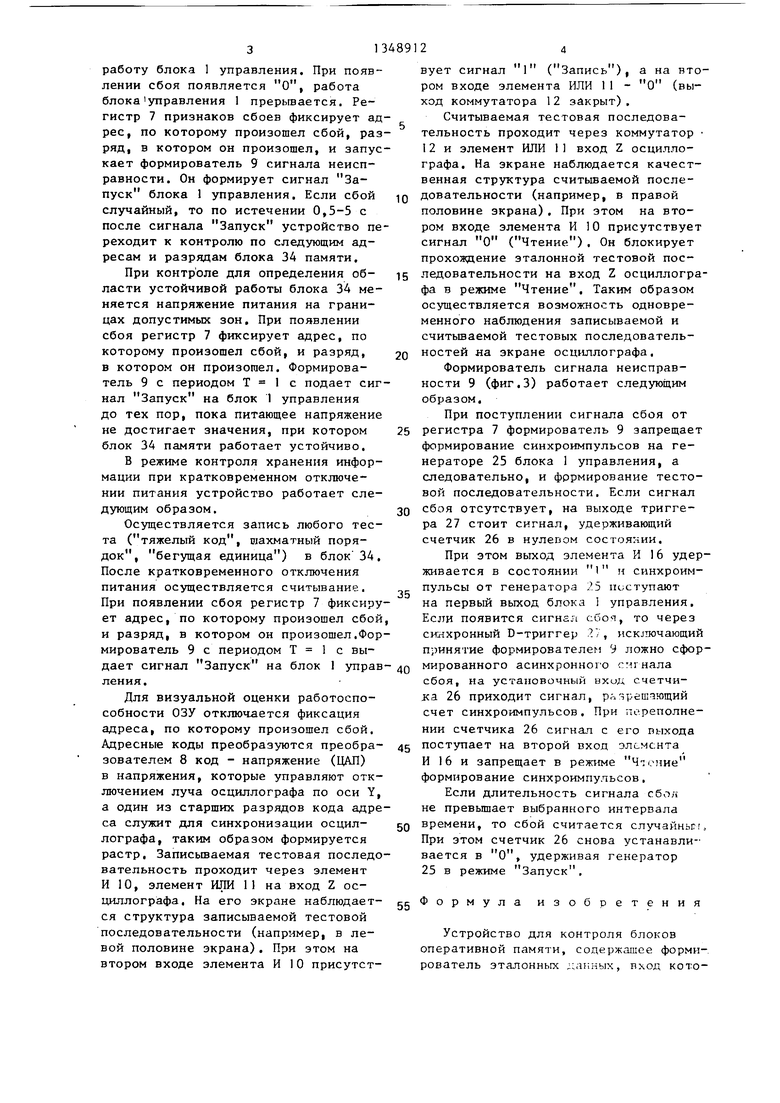

Коммутатор 12 (фиг,2) содержит дешифратор 13 со стробирующим входом и мультиплексор 14 со стробирующим входом.

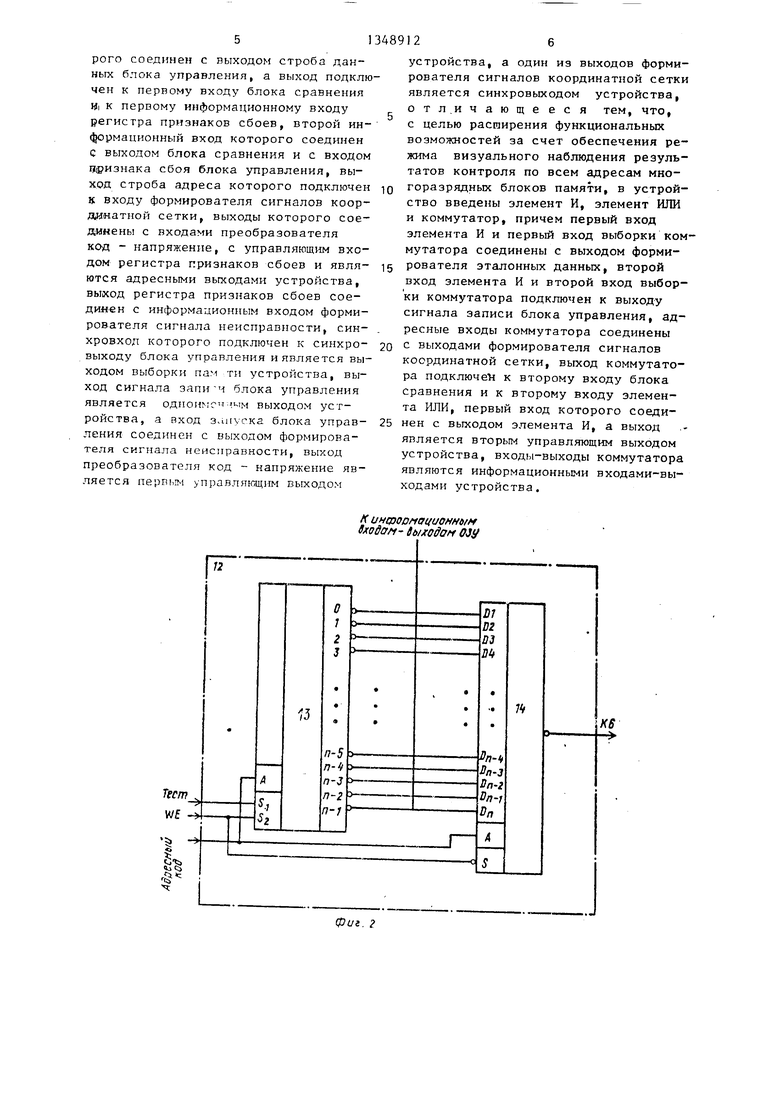

Блок 1 управления (фиг.З) содержит счетчик 15 адреса (двоичный счетчик с коэффициентом пересчета 1 /п, где п - разрядность кода, адреса), двухвходовые элементы И - НЕ 16-19, и И 21, элемент 22 задержки, синхронный D-триггер 23, RS-триггер 24, генератор 25,

Формирователь 9 сигнала не1 справ- ности (фиг,3) содержит счетчик 26 и триггер 27,

Формирователь 4 эталонных данных (фиг.4) содержит дешифратор 28,муль- типлексор 29, двоичный счетчик 30, разрядность которого определяется длительностью цикла Запись/Чтение, счетчик 31 1ЩКЛОВ и двоичный счетчик 32 с переменным коэффициентом пере- счета, инвертор 33,

На фиг,1 показан также контролируемый блок 34 памяти.

Принцип работы устройства следующий.

Блок 1 управления вырабатывает импульсы синхронитации, которьте подаются }ia вход синхронизации блока 34 памяти и на первьи вход формирою

15 2025

зо

-40

45 Q

55

489122

вателя сигнала неисправности. Кроме того, блок 1 управления вырабатьша- ет управляющие сигналы, которые запускают формирователь 5 сигналов координатной сетки и формирователь 4 эталонных данных.

По управляющим сигналам блока 1 управления формирователь 5 сигналов координатной сетки (выполненный, например в виде обычного двоичного счетчика) вырабатьгаает адресные коды, начиная с нулевого, и последовательно увеличивает их на единицу до максимального, представляющего собой единицы со всех разрядов кода.

Затем он вновь возвращается к нулевому адресному коду и т.д. Причем младшие разряды адресного кода соответствуют адресным разрядам блока 34 памяти, следующий разряд используется для синхронизации осциллографа, а старшие разряды служат для выбора коммутатором 12 одного из информационных входов-выходов многоразрядного блока 34 памяти. Формирователь 2 (фиг.4) по управляющим сигналам блока 1 управления вырабатьта- ет последовательность нулей и единиц, которая через формирователь 3 поступает на третий вход коммутатора 12. При поступлении на его первый вход сигнала Запись, который вырабатывается по управляющим сигналам блока 1 управления, тестовая последовательность проходит через коммутатор 12 на соответствующий информационный вход-выход блока 34 памяти. Сигнал Запись в то же время поступает и на вход Запись/Чтение блока 34 памяти (WE) в результате бсущест- вляется запись тестовой последовательности .

После записи этой последовательности по одному входу-выходу осуществляется считывание. При этом с четвертого выхода блока 1 управления сигнал Чтение поступает на вход Запись/Чтение блока 34 (WE) и первый вход коммутатора 12. Считьшаемая с того же входа-выхода блока 5 тестовая последовательность поступает через коммутатор 12 на второй вход блока б сравнения. Па первый ее вход подается эталопппя последовательность с выхода формирователя 4. При совпа- дс1П1и считанной последовательности с эталонной на выходе блока 6 сравнения сохраняется 1, не превышающая

313

работу блока 1 управления. При появлении сбоя появляется О, работа блока Iуправления 1 прерьшается. Регистр 7 признаков сбоев фиксирует адрес, по которому произошел сбой, разряд, в котором он произошел, и запускает формирователь 9 сигнала неисправности. Он формирует сигнал Запуск блока 1 управления. Если сбой случайный, то по истечении 0,5-5 с после сигнала Запуск устройство переходит к контролю по следующим адресам и разрядам блока 34 памяти.

При контроле для определения об- ласти устойчивой работы блока ЗА меняется напряжение питания на границах допустимых зон. При появлении сбоя регистр 7 фиксирует адрес, по которому произошел сбой, и разряд, в котором он произошел. Формирователь 9 с периодом Т 1 с подает сигнал Запуск на блок 1 управления до тех пор, пока питающее напряжение не достигает значения, при котором блок 34 памяти работает устойчиво.

В режиме контроля хранения информации при кратковременном отключении питания устройство работает следующим образом.

Осуществляется запись любого теста (тяжелый код, шахматный порядок, бегущая единица) в блок 34. После кратковременного отключения питания осуществляется считывание. При появлении сбоя регистр 7 фиксирует адрес, по которому произошел сбой и разряд, в котором он произошел.Формирователь 9 с периодом Т 1 с выдает сигнал Запуск на блок 1 управ ления.

Для визуальной оценки работоспособности ОЗУ отключается фиксация адреса, по которому произошел сбой. Адресные коды преобразуются преобра- зователем 8 код - напряжение (ЦАП) в напряжения, которые управляют отключением луча осциллографа по оси Y, а один из старших разрядов кода адреса служит для синхронизации осцил- лографа, таким образом формируется растр. Записьшаемая тестовая последовательность проходит через элемент И 10, элемент ИЛИ 11 на вход Z осциллографа. На его экране наблюдает- ся структура записываемой тестовой последовательности (например, в левой половине экрана). При этом на втором входе элемента И 10 присутст

5

0

о

5 0 с

5

24

вует сигнал 1 (Запись), а на втором входе элемента ИЛИ 11 - О (выход коммутатора 12 закрыт).

Считываемая тестовая последовательность проходит через коммутатор I2 и элемент ИЛИ 11 вход Z осциллографа. На экране наблюдается качественная структура считьшаемой последовательности (например, в правой половине экрана). При этом на втором входе элемента И 10 присутствует сигнал О (Чтение) . Он блокирует прохождение эталонной тестовой последовательности на вход Z осциллографа в режиме Чтение. Таким образом осуществляется возможность одновременного наблюдения записываемой и считьшаемой тестовых последовательностей на экране осциллографа.

Формирователь сигнала неисправности 9 (фиг.З) работает следующим образом.

При поступлении сигнала сбоя от регистра 7 формирователь 9 запрещает формирование синхроимпульсов на генераторе 25 блока 1 управления, а следовательно, и формирование тестовой последовательности. Если сигнал сбоя отсутствует, на выходе триггера 27 стоит сигнал, удерживающий счетчик 26 в нулевом состоянии.

При этом выход элемента И 16 удерживается в состоянии 1 и синхроимпульсы от генератора 25 поступают на первый выход блока 1 управления. Если появится сигнал сбоя, то через синхронный D-триггер 27, иск:ж)чающий принятие формирователем 9 ложно сформированного асинхронног о сигнала сбоя, на установочный вход счетчика 26 приходит сигнал, р иярешэющий счет синхроимпульсов. При переполнении счетчика 26 сигнал с его пыхода поступает на второй вход элемента И 16 и запрещает в режиме Чтение формирование синхроимпульсов.

Если длительность сигнала сбои не превьш1ает выбранного интервала времени, то сбой считается случайны;., При этом счетчик 26 снова устанавливается в О, удерживая генератор 25 в режиме Запуск,

Формула изобретения

Устройство для контроля блоков оперативной памяти, содержащее формирователь эталонных ;;а1;ных, вход которого соединен с выходом строба данных блока управления, а выход подключен к первому входу блока сравнения И: к первому информационному входу регистра признаков сбоев, второй информационный вход которого соединен С выходом блока сравнения и с входом признака сбоя блока управления, выход строба адреса которого подключен к входу формирователя сигналов координатной сетки, выходы которого соединены с входами преобразователя код - напряжение, с управляющим входом регистра признаков сбоев и явля- ются адресными выходами устройства, выход регистра признаков сбоев соединен с информационным входом формирователя сигнала неисправности, син- хровход которого подключен к синхро- выходу блока управления и является выходом выборки пам ти устройства, выход сигнала запи-ч блока управления является выходом устройства, а вход блока управ- ления соединен с выходом формирователя сигнала неисправности, выход преобразователя код - напряжение является nepniiiM управляющим выходом

Тест WE

§

устройства, а один из выходов формирователя сигналов координатной сетки является синхровыходом устройства, отл,и чающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения режима визуального наблюдения результатов контроля по всем адресам многоразрядных блоков памяти, в устройство введены элемент И, элемент ИЛИ и коммутатор, причем первый вход элемента И и первый вход выборки коммутатора соединены с выходом формирователя эталонных данных, второй вход элемента И и второй вход выборки коммутатора подключен к выходу сигнала записи блока управления, адресные входы коммутатора соединены с выходами формирователя сигналов координатной сетки, выход коммутатора подключен к второму входу блока сравнения и к второму входу элемента ИЛИ, первый вход которого соединен с выходом элемента И, а выход является вторым управляющим выходом устройства, входы-выходы коммутатора являются информационными входами-выходами устройства.

К инфосмоционногн входом- tbixodofi OJy

Г

27

кблок 13

25

1 KS OKOfi 5,Ю.12

Фи.3

. Составитель О.Исаев Редактор Т.Лазоренко Техред М.Ходанич

Заказ 5196/52 Тираж 587Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Рсушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,

фиг. h

Корректор И.Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

Изобретение относится к вычисли- тельной технике и может быть использовано для контроля работоспособногти блоков оперативной памяти. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения режима визуального наблюдения результатов контроля по всем адресам многоразрядных блоков памяти. Устройство содержит блок управления формирователи 2,3, объединенные в формирователь 4 эталонных данных, формирователь сигналов координатной сетки 5, блок 6 сравнения, регистр 7 признаков сбоев, преобразователь 8 код - напряжение, формироя тсль 9 сигнала неисправности, элемент И 10, элемент ИШ1 11 и коммутатор 1 2 . 4 ил , С со 4 00 со

| Устройство для контроля блоков памяти | 1980 |

|

SU898508A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устройство с автономным контролем | 1979 |

|

SU855739A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-10-30—Публикация

1985-03-19—Подача