(54) ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1979 |

|

SU809547A1 |

| Цифроаналоговый преобразовательС АВТОМАТичЕСКОй КОРРЕКциЕй НЕли-НЕйНОСТи | 1979 |

|

SU809549A1 |

| Цифро-аналоговый преобразователь с автоматической коррекцией нелинейности | 1980 |

|

SU930651A2 |

| Цифро-аналоговый преобразователь с автоматической коррекцией нелинейности | 1980 |

|

SU951692A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УДЕЛЬНОЙ ЭЛЕКТРОПРОВОДИМОСТИ МОРСКОЙ ВОДЫ | 2007 |

|

RU2366937C2 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Измерительное устройство к балансировочному станку | 1985 |

|

SU1259119A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

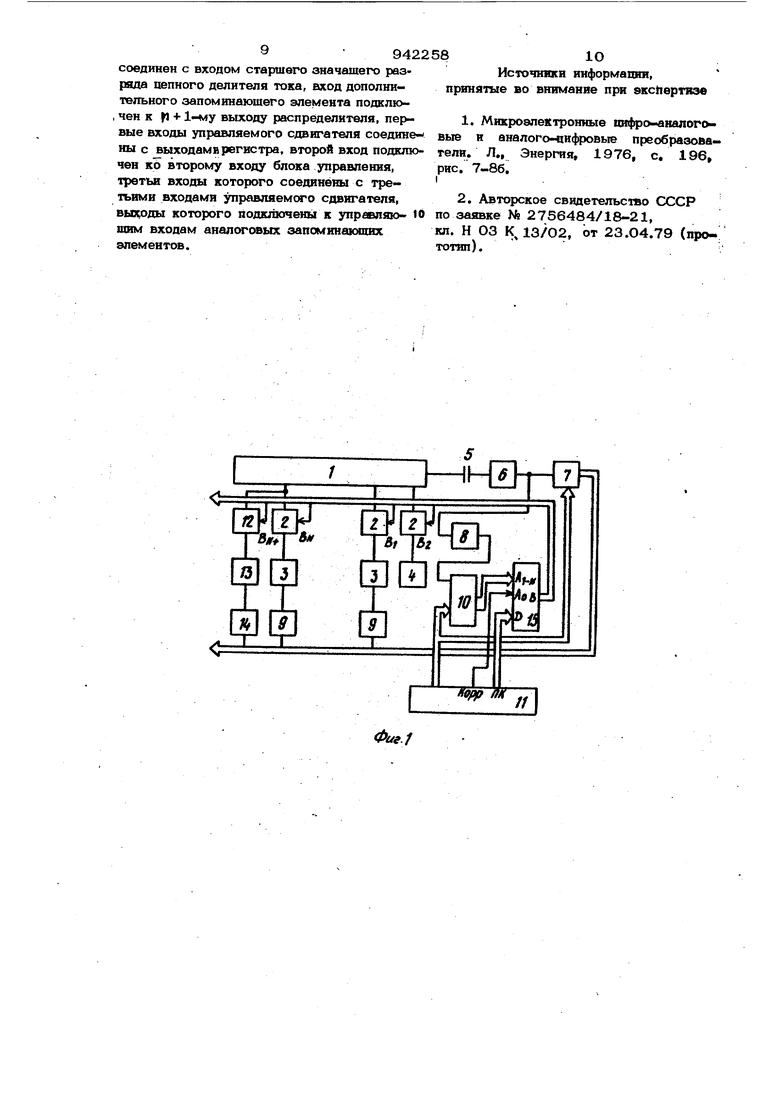

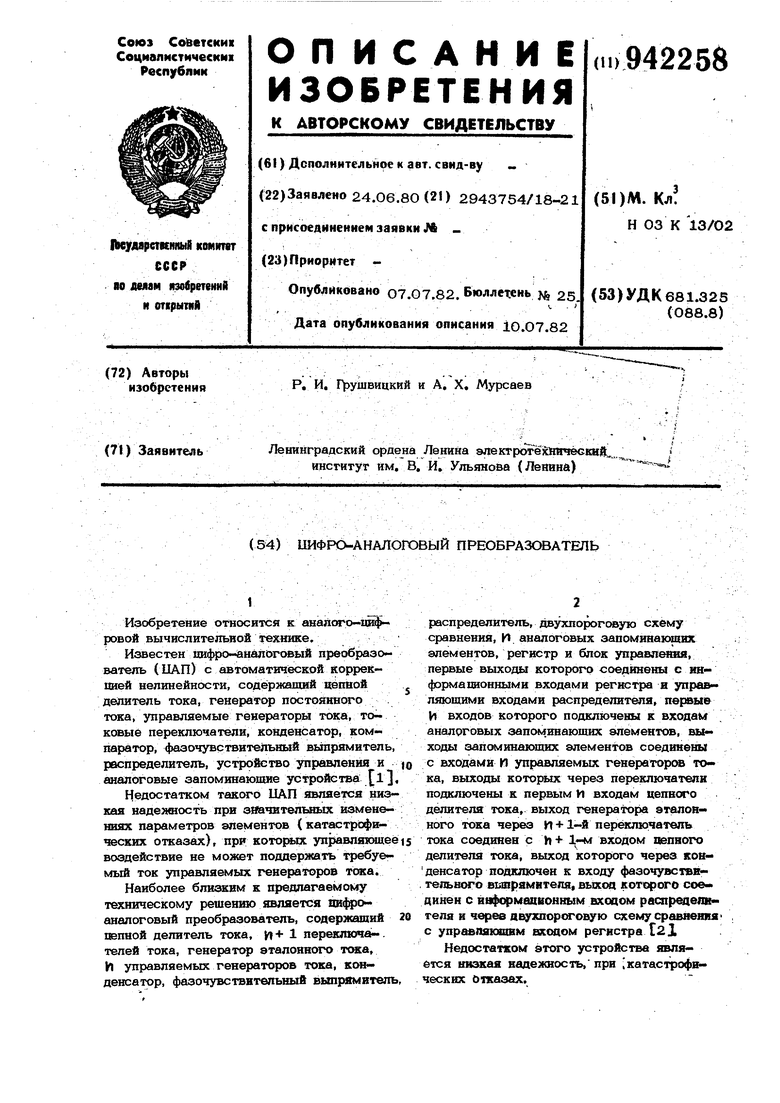

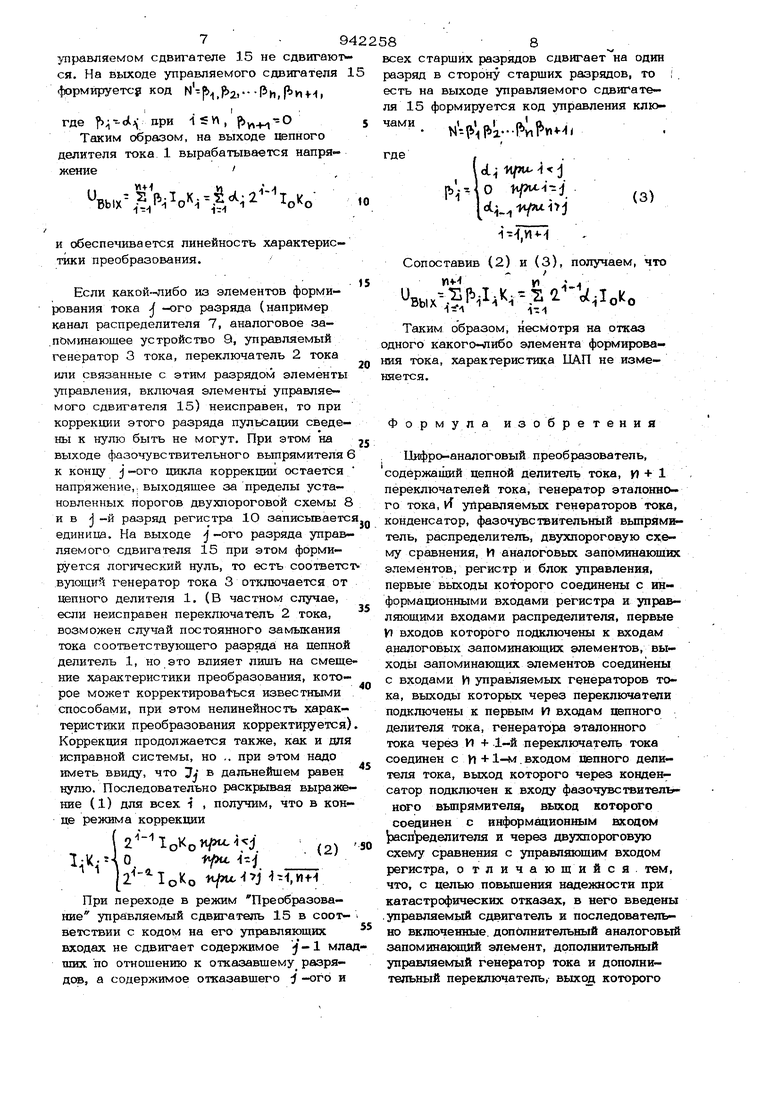

. - 1,:.-.Изобретение относится к анаяого-шфровай вычислительной технике. Известен цифро-аналоговый преобразователь (UAn) с автоматической йоррек1Шей нелинейности, содержащий цепной делитель тока, генератор постоянного тока, управляемые генераторы тока, токавыё переключатели, конденсатор, компаратор, с|)азочувствительный вьп1рямитель распределитель, устройегао управления и аналоговые запоминающие устройства |l j Недостатком такого ЦАП является низ кая надежность при заачительных изменениях параметров элементов ( катастрофических отказах), при которьрс управлякнце воздействие не может поддержать требуемый ток управляемых генераторов тока. Наиболее близким к предлагаемому техническому решению является шфроаналоговый преобразователь, содержащий цепной делитель тока. 1 переключи, телей тока, генератор эталонного тсика, h управляемых генераторов тока, кон денсатор, фазочувствительный выпрямител распределитель, двутшорогснаую схему сравнения, И аналоговых запоминающих элементов, регистр и блок управле«ия, первые выходал которого соединены с информа тонным и входами регистра и управляющими входами распределителя, первые И входов которого подключены к входам аналоговых запок§инающих элементов, выходы запоминакяцих элементов соединены с входами К управляемых генераторе тока, выходы которых через переключатели подключены к первым И входам цепнся о делителя тока, выход генератора эталонного тока через И +1-и переключатель тока соединен с h + входом цепного делителя тока, выход которого через конденсатор подключен к входу фазочук:твйтельного всшрямите1Ш| выход которого соединен с информационным входом распределнгеля и черев двухпорсмговую схему сравнения с упрсюяяюшвм входом регистра Г21 Недостатком этого устройства является низкая надежность,при катастрофе ческах Отказах. 394 Цель изобретоиия - повышение надежffocTH при катастроф1Г сскнх отказах. Указанная цель достигается тем, что в пифро-аналоговый преобразователь, содержащий цепной делитель тока, К1+ 1 переключателей тока, генератор эталонного тока, И управляемых генераторов тока, конденсатор, фазочувствительный выпрямитель, распределитель двухпороговуго схему сравнения, И аналоговых зопоминаюших элементов, регистр и блок управления, первые выходы которого соединены с информационными входами регистра и управляющими входами распределителя, первые И входов которого подключены к входам аналоговых запоминающих элементов, выходы запоминающих элементов соединены с входами и управляемых генераторов тока, выходы которы через переключатели подключены к первым Ц входам цепного делителя тока, вы ход reiEpaTopa эталонного тока через h + 1-й переключатель тока соединен с Y + 1-м входом цепного делителятока, выход которого через конденсатор подклк чей к входу фазочувствительного выпрямителя, выход которого соединен с инфор мационным входом распределителя и чере двухпорогоную схему сравнения с управляющим входом регистра, введены управляемый сдвигатель, и последовательно включенные дополнительный аналоговый запоминающий элемент, дополнительный управляемый генератор тока и дополнительный переключатель, выход которого соединен с входом старшего значащего разряда цепного делителя тока, вход дополнительного запоминающего элемента подключен к h + 1-му выходу распределителя, первые входы управляемого сдвигателя соединены с выходами регистра, второй вход подключен ко второму входу блока управления, третьи входы которого соединены с третьими входами управляемого сЬвигателя, выходы которого подключены к управляющим входам аналоговых запоминающих элементов. Принцип действия изобретения состои в том, что при обнаружении отказа в каком-либо разряде генератор тока этого разряда отключается от цепного делителя калвдый следующий разряд автоматически уменьщает свой весовой коэффициент вдвое, выполняя таким образом роль пре дыдущего, старщий разряд замещается дополнительным разрядом. Управляемый сдвигатель в режиме преобразования выполняет сдвиг старщей относительно мес 84 та отказа части декодируемого кода на один разряд в сторону старших разрядов. На фиг. 1 приведена схема цифро-аналогового преобразователя; на фиг. 2 один из возможных вариантов реализации управляемого сдвигателя. Цифро-аналоговый преобразователь содержит цепной делитель 1 тока, входы которого соединены с выходами переключателей 2 тока, информационный вход одного из которых соединен с выходом генератора 3 постоянного тока, а остальных - с выходами управляемых генераторов 4 тока. Выход цепного делителя тока через конденсатор 5 соединен с вхо« дом фазочувствительного выпрямителя 6, выход которого соединен с информщионным входом распределителя 7 и входом двухпороговой схемы 8 сравнения. Выходы распределителя соединены с входами аналоговых запоминающих устройств 9, выходы которых соединены с входами управляемых генераторов тока. Выход двухпороговой схемы сравнения соединен с управляющим входом регистра 1О, информационные входы которого соединены с выходами устройства 11 управления и управляющими входами распределителя 7. Выход дополнительного управляемого генератора 12 тока соединен с информацк- oHHbiM входом дополнительного переклк Чателя 13 TOKia, а вхрд- с выходом дополнительного аналогового запоминающего устройства 14, выход которого соединен с выходом распределителя. Выход дополнительного переключателя тока соединен с выходом переключателя тока старшего разряда. Выходы регистра соединены с управляющими входами управляемого сдвигатепя 15, информационные входы которого соединены с выходами устройства управления. Выходы управляемого сдвнгателя соединены с управляющими входами переключателей тока. Все элементы схемы являются стандартными и ширсжо известными. Блок управления может быть выполнен в виде распределителя импульсов. Управляемый сдвигатель может быть реализован разными способами, например, на базе микропроцессора. Вариант реализации управляемого сдвигателя 15 приведен на логических микросхемах малой степени интеграции. Управляющие входы сдвигателя на логических микросхемах ( Aj AM подключены к первым входам элементов ИЛИ/ИЛИ-НЕ 16, второй вход каждого последующего из которых соединен с неинвертирующим выходом предыдущего, второй вход перво5942го элемента ИПИ/ИЛИ-НЕ 16 соединен с его первым входом. Выходы элементов ИЛИ/ИЛИ-НЕ 16 соединены с первыми входами первой и второй групп входов элементов И-ИПИ 17, вторые входы первой группы каждого последующего элемента И-ИЛИ 17 соединены со вторыми входами второй группы предыдущего элемента и информационным входом управляемого сдвигателя. Второй вход второй группы последнего элемента И-ИЛИ 17 и второй вход первой группы первого элемента И-ИЛИ 17 соединены с общей шиной устройства. Третьи входы первых и вторых групп входов элементов И-ИЛИ 17 соединены с выходом инвертора 18, вход которого соединен с, управляющим входом управляемого сдвигателя ( АО ), который соединен с первыми входами третьих групп входов элементов И-ИЛИ 17, вторые входы третьих групп входов элементов И-ИЛИ 17 соединены со вторыми входамп вторых групп входов тех же элементов. Выходы элементов И-ИЛИ 17 соединены с перзыми входами элементов Запрет 19, вто- 2 рые входы которых соединены с управляющими входами управляемого сдвигателя. Устройство работает следующим образом. Предусмотрено два режима работы: зо Коррекция и Преобразование. В режиме Коррекция на вход управляемого сдвигателя 15 с устройства 11 управления подается уровень, соответствующий логической единице. Управляемый сдвигатель при этом не сдвигает кодов, поступающих на информационные входь. Режим коррекции состоит из N + 1 циклов ( N разрядность 11АП). Каждый шшл состоит из нескольких ( Ю - 20) тактов, каждый из которых разбит на два полутакта. В каждом 1 -ом цикле в первом полутакте каждого такта на выходе устройсгва 11 управления вырабатывается код, содержащий логическую единицу в эталонном разряде ив i - 1 младших разрядах. Во втором полутакте вырабатьгоается код, содержащий единицу только в -f -ом разряде. На распределитель 7 в течение цикла непрерывно подается код, обеспечивающий его коммутацию таким образом, что выход фазочувствительного вьшрямителя 6 соединяется с входом аналогового запоминающего устройства -го разряда. Замкнутая цепь отрицательной обратной связи (конденсатор 5 - фазочувствительны вьшрямитель 6 - аналоговое запоминакице устройство 9 -1 -ого разряда - управляемый генератор тока 3 - переключатель 2 8 тока -ого разряда - цепной делитепь 1 тока (стремится при достаточно коэффициенте усиления фазочувствительного выпрямителя 6 и исправности элементов i -го разряда к состоянию, при котором пульсации на выходе цепного делителя тока 1 близки к нулю. То есть где If, - значение тока генератора 4 постоянного тока; I.J - значение тсжа генератора 3 тока младшего по отношению к 1-ому разряду; коэффициенты передачи cooi ветствующего тока на выход делителя 1, имеющие размерность сопротивления; Kplo -весовой коэффи1иент i -ого разряда. При этом на выходе фазочувствительного вьшрямителя 6 к KOHI цикла устанавливается некоторое напряжение управпения генератором 3 тока в пределах шкалы допустимых управляющих напряжений. Это напряжение запоминается на аналоговом запоминакяцем устройстве 9 i -го разряда. Пороги двухпороговой схемы 8 сравнения установлены вблизи границ допустимых управляющих напряжений. Если входное напряжение двухпороговой схемы 8 сравнения находится между порогами, на ее выходе пртсутствует сигнал, соответст вукмций логическому нулю, в противном случае - логической единице. В конце Ч -го цикла коррекции сигнал с выхода двухпороговой схемы 8 сравнения записы веется в i-й разряд регистра 10. Если все разряды исправны, то после М циклов коррекции для каждого разряда усганавливается такой ток. что . . а во всех разрядах регистра 10 записаны логические нули. Устройство переходит в режим Преобразование, при котором на выходы устройства 11 управления подается преобразуемый код N vi,,2. -ot, oC,.i). На управляющем входе управляемого сдвигателя 15 связанного с устройством 11 управления устанавливается логический нуль, но так как на остальных входах управляемого сдвигателя 15 также присутствуют логические нули, коды в управляемом сдвигателе 15 не сдвигают ся. На выходе управляемого сдвигателя 1 формгфуетс код N-p,}),. Ph., .О где f) при 15У, jby, Таким образом, на выходе цепного делителя тока 1 вырабатывается напряжение%, и сйеспечивается линейность характеристики преобразования. Если какой--пибо из элементов формирования тока -j -ого разряда (например канал распределителя 7, аналоговое за.п&минаюшее устройство 9, управляемый генератор 3 тока, переключатель 2 тока или связанные с этим разрядом элементы управления, включая элементы управляемого сдвигателя 15) неисправен, то при коррекции этого разряда пульсации сведены к нулю быть не могут. При этом на выходе фазочувствительного вьшрямителя к концу j-ого цикла коррекции остается напряжение,, выходящее за пределы установленных порогов двухпороговой схемы 8 ив j -и разряд регистра 10 записьгоаетс единица. На выходе j -ого разряда управ ляемого сдвигателя 15 при этом формируется логический нуль, то есть соответс вующий генератор тока 3 отключается от цепного делителя 1. (В частном случае, если неисправен переключатель 2 тока, возможен случай постоянного замыкания тока соответствующего разряда на цепной делитель 1, но это влияет лишь на смеще ние характеристики преобразования, которое может кoppeктиpoвatьcя известными способами, при этом нелинейность характеристики преобразования корректируется Коррекция продолжается также, как и для исправной системы, но ,. при этом надо иметь ввиду, что Jv в дальнейшем равен нулю. Последовательно раскрывая выраже ние (1) для всех 1 , получим, что в конце режима коррекции и2 loKo«/ « JОfi i-j bl.MH При переходе в режим Преобразование управляемый сдвигатель 15 в соответствии с кодом на его управляющих входах не сдвигает содержимое ;/- мла ших по отношению к отказавшему разрядов, а содержимое отказавшего -j -ого и всех старших разрядов сдвигает на один разряд в сторону старших разрядов, то есть на выходе управляемого сдвигателя 15 формируется код управления клк чамиN--lb a--PytNM/ ({bUlo lipw-i-j |o«-|. i-f.Mv-f и (3), получаем, Сопоставив (2) . «-(iloKo Таким образом, несмотря на отказ дного какого-либо элемента формироваия тока, характеристика ЦАП не измеяется. Формула изобретения Цифро-аналоговый преобразователь, содержащий цепной делитель тока, М+1 переключателей тока, генератор эталонного тока, кГ уйравляемых генераторов тока, конденсатор, фазочувствительный выпрямитель, распределитель, двухпороговую схему сравнения, И аналоговых запоминающих элементов, регистр и блок управления, первые выходы которого соединены с информационными входами регистра и управляющими входами распределителя, первые V) входов которого подключены к входам аналоговых запоминающих элементов, выходы запоминающих элементов соединены с входами И управляемых генераторов тока, выходы которых через переключатели подключены к первым И входам цепного делителя тока, генератора эталонного тока через И + 1-и переключатель тока соединен с Ц + 1-м. входом цепного делителя тока, выход которого через конденсатор подключен к входу фазочувс тфительногр вьшрямитепя, выход которого соединен с информационным входом эасп делителя и через двухпороговую схему сравнения с управл5пощим входом регистра, о тличающийся тем, что, с целью повыщения надежности при катастрофических отказах, в него введены .управляемой сдвигатель и последовательно включенные, дополнительный аналоговый запоминакжшй элемент, дополнительный управляемый генератор тока и дополнительный переключатель, выхрд которого

соединен с входом старшего значащего разряда цепного делителя тока, вход дополнительного запоминающего элемента подклю, чен к fJ + 1-му выходу распределителя, первые входы управляемого сдвягателя соединены с выходами регистра, второй вход подключен ко второму входу блока управления, третьи входы которого соединены с третьими входами управляемого сдвига теля, выходы которого подклхпены к управляю- щим входам аналоговых запоминающих элементов.

Источники информашт, принятые во внимание при экспертизе

рис. 7-86,

I

кл. Н 03 К, 13/02, от 23.04.79 (прототип).

Авторы

Даты

1982-07-07—Публикация

1980-06-24—Подача