(54) ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ

С АВТОМАТИЧЕСКОЙ КОРРЕКЦИЕЙ НЕЛИНЕЙНОСТИ

ния в фазовом детекторе и аналоговых запоминающих элементах конденсаторов большой емкости.

Цель изобретения - повышение быстродействия преобразователя и улучшение технологичности его изготовления .

Поставленная цель достигается тем НТО в цифроаналоговый преобразовател с автоматической коррекцией нелинейности, содержащий цепной делитель тока, генератор постоянного тока и управляемое генераторы тока, выходы которых соединены с информационными входами переключателей тока, первые выходы которых соединены с входами цепного делителя тока, а вторые -. с общей шиной, блок управления и аналоговые запоминающие элементы,выходы которых соединены с входами управляемых генераторов тока, включены регистр сдвига, дополнительный аналоговый запоминающий элемент, операционный усилитель с дифференциальным входом, первая группа элементов ИЛИ, вторая группа элементов ИЛИ элементы И и Запрет по числу разрядов преобразователя, причем выходы каждого предыдущего из первой группы элементов ИЛИ соединены с первым входом последующего, а у первого из них входы объединены, выходы- всех элементов ИЛИ второй группы и одного элемента И соединены с управляющими входами переключателей тока, первые входы элементов ИЛИ второй группы соединены с выходами преобразуемого кода блока управления, вторые входы - с выходами элементов И, а третьи - с выходами элементов Запрет и управляющими входами аналоговых запоминающих элементов информационные входы которых соединены с выходом операционного усилителя с дифференциальным входом, неинвертирующий вход которого соединен с выходом .Цепного делителя тока, а инвертирующий - с выходом дополнительного аналоговогозапоминающего элемента, выход, синхроимпульсов блока управления соединен с первыми входами элементов R и Запрет,управляющим входом дополнительного аналогового запоминающего элемента и входом синхронизации регистра сдвига информационный вход которого соединен с выходом блока управления, а выходы - со вторыми входами элементов Запрет и вторыми входами элементов ИЛИ первой группы, вторые выходы которых соединены со вторыми входами элементов И.

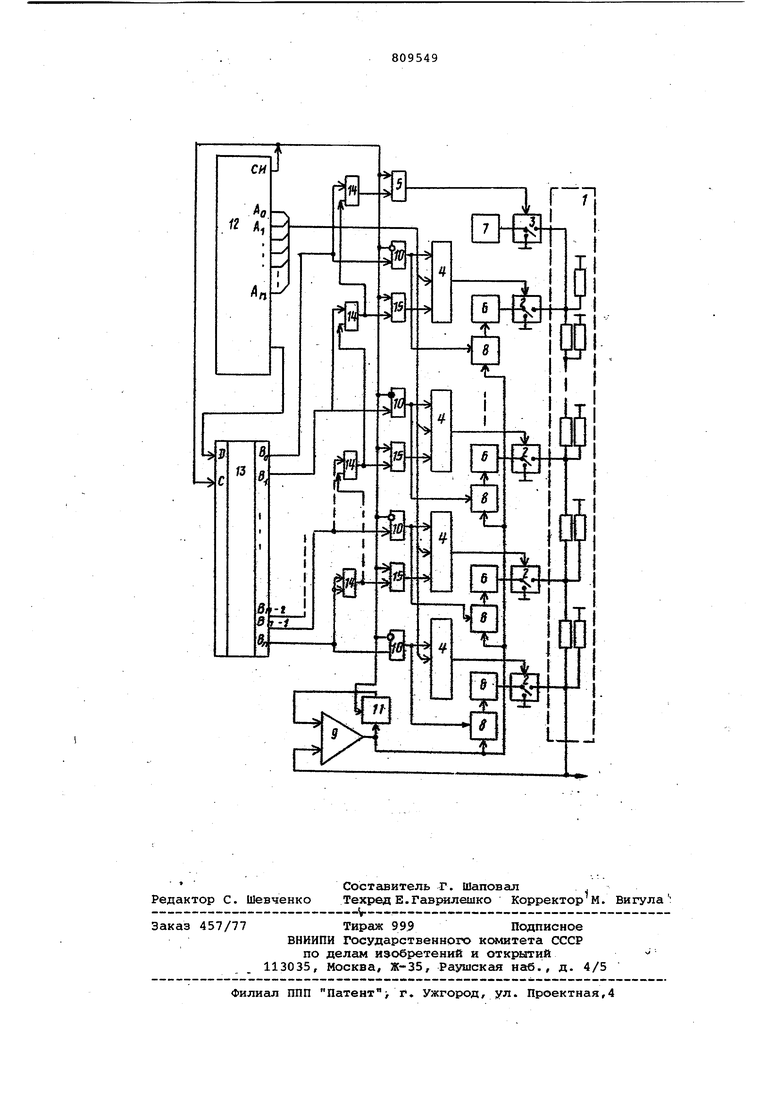

На чертеже представлена блок-схема предлагаемого устройства.

Цифроаналоговый преобразователь с автоматической коррекцией нелинейности содержит цепной делитель 1 тока, входы которого соединены с выходами переключателей 2 тока рабочих разрядов и переключателя 3 тока эталонного разряда, вторые выходы которых соединены с общей шиной, управляющие входы переключателей 2-е выходами элементов ИЛИ 4 переключателя 3-е выходом элемента И 5, информационные входы переключателей 2 рабочих разрядов соединены с выходами управляемых генераторов 6 тока, а вход переключателя 3 эталонного разряда - с выходом генератора постоянного тока 7 Входы управляемых генераторов 6 постоянного тока соединены с выходами аналоговых запоминающих элементов 8, информационные входы, которых соединены с выходом дифференциального операционного усилителя 9 а управляющие входы - с выходами элементов 10 Запрет, Нейнвертирующий вход усилителя 9 соединен с выходом цепного делителя 1 тока, а инвертирующий - с вьрсодом дополнительного аналогового запоминающего элемента 11, информационный вход которого соединен с выходом операционного усилителя 9, а управляющий - с выходом синхроимпульсов (си) блока 12 управления и входом синхронизации с регистра 13 сдвига. Информационный вход регистра 13 сдвига соединен с выходом блока 12 управления. Выходы Вр,В,...Вц регистра 13 сдвига- соединены с первыми .входами цепочки элементов ИЛИ 14, второй вход каждого из которых соединен с выходом следующего, а оба входа первого элемента ИЛИ 14 соединены между собой Первые входы элементов И 15 и элементов 10 Запрет соединены с выходом СИ блока 12 управления. Вторые входы элементов 10 Запрет соединены с выходами B(j, В,...Вц регистра 13 сдвига, а вторые входы элементов И 15 соединены с выходами элементов ИЛИ 14. Выходы элементов 10 Запрет и элементов И 15 попарно соединены соответственно с первыми и вторыми входами элементов ИЛИ 4, третьи входы которых подключены к выходам блока 12 управления, на них поступает преобразуемый код

АП , А,

.AL

о f 1 и

Все элементы устройства широко известны. Блок 12 управления может быть регшизован в виде генератора и распределителя импульсов. Кон-, кретная схема распределителя импульсов определяется областью применения ЦАП.

Устройство работает следующим образом.

Предусмотрены два режима работы коррекция и преобразование. В режиме коррекция блок 12 управления прекращает выдачу преобразуемых кодов, и на соответствующих выходах устанавливаются напряжения, соответствующие логическому нулю.

Одновременно на выходе блока 12 управления, соединенном с информационным входом D регистра 13 сдвига появляется импульс, устанавливающий младший разряд регистра 13 сдвига в единичное состояние. Цикл коррекции занимает N тактов (N разрядность ЦАП).В каждом такте единица, записанная в регистр 13 сдвига сдвигается на один разряд в сторону старших разрядов.

В первом такте коррекции, пока существует синхроимпульс, сигналы, соответствующие логической единице , присутствуют на выходах последней ячейки цепочки элементов ИЛИ 14 и первого элемента И 5. При этом ток генератора 7 постоянного тока поступает на вход делителя 1 тока и разрешается запись напряжения в дополнительный аналоговый запоминающий элемент 11. На выходе элемента 11-за счет глубокой отрицательной обратной связи через операционный усилитель с дифференциальным входом устанавливается напряжение

J doKo + е ) ..

где I о - ток генератора постоянного тока; К Q - коэффициент передачи

тока.генератора постоянного тока на выход Е делителя, имеющий размерность сопротивления; К и коэффициенты усиления

операционного, усилителя по инвертирующему и неинвертирующему входам соответственно;

е - ЭДС смещения операционного усилителя.

После окончания синхроимпульса генератор 7 постоянного тока отключается от входа цепного делителя 1 тока. Сигналы, соответствующие логической единице возникают на выходах элемента 10 Запрет и элемента. ИЛИ 4, соответствующих младшему разряду ЦАП и -на управляющем входе аналогового §апоминаю1цего элемента 8, соединенного с генератором 6 тока этого разряда.

За счет глубокой отрицательной обратной связи на аналоговом запоминакнцем элементе 8 младшего разряда устанавливается напряжение, сводящее к нулю разбаланс напряжений на входах операционного усилителя 9. При этом

Ьых i.K U v«4-/ --e

где К - коэффициент передачи тока младшего разряда на выход цепного делителя 1. Таким образом, напряжение, создаваемое на выходе ЦАП генератором

б тока млс1дшего разряда становится равным напряжению, создаваемому генератором 7 постоянного тока.

Аналогично в каждом очередном i-OM такте коррекции во время существования синхроимпульса на выходе блока 12 управления в дополнительном аналоговом запоминающем элементе 11 запоминается напряжение, равное с точностью до ЭДС смещения операционного усилителя и неидентичности

0 его коэффициентов передачи по разным входам) сумме весовых коэффициентов всех младших i-1 разрядов и эталонного, .а после окончания синхроимпульса на аналоговом запоми5нающем элементе 8 i-го разряда устанавливается такое напряжение, что весовой коэффициент этого разряда равен

2 -to-Ко

И I)-KJ IO-KO

20

При этом ошибки, вызванные ЭДС смещения и неидентичностью коэффициентов передачи по разным входам операционного усилителя в каждом

5 такте компенсируются.

После N тактов коррекции токи во всех разрядах устанавливаются такими, что весовые коэффициенты каждого разряда пропорциональны

0 целой степени двух.

Блок 12 управления автоматически переходит в режим преобразование. При этом на выходы блока 12 управ-. Ленин поступают коды, подлежащие

5 декодированию. Через элементы ИЛИ 4 эти коды поступают на управляющие входы переключателей 2 тока. Напряжение на выходе цепного делителя 1 тока при этом пропорционально числу,

0 представленному входным позиционным двоичным кодом

п -1 X OCi-2 ,

1

о

Н

где afi 0 или 1 - значение i-ro разряда преобразуемого кода. Таким образом, обеспечивается линейность преобразования независимо от конкретных характеристик (в частности от точности изготовления) генераторов тока, токовых ключей и цепного делителя тока.

Масштаб преобразования при этом не стабилизируется, для этого могут быть применены известные узлы автоматической коррекции масштаба преобразования.

Таким образом, предлагаемое устройство, обеспечивает высокую точность преобразования без предъявления существенных требований к точности изготовления элементов схемы.

В отличие от известных устройств оно не требует многократного чередования состояний ключей при коррекции каждого разр.яда и фильтрации

импульсных сигнсшов в фазовом .детекторе, что существенно (в 50-100 раз) сокращает необходимое время коррекции. .

Дополнительный эффект, который дает предлагаемое устройство эаклю.чается в снижении необходимых номиналов емкостей в аналогсэвых запоминакщих элементах и фазрйых детекторах, чтообеспечивает возможность интегральной реализации устройства.

Формула изобретения

Цифроаналоговый преобразователь с автоматической коррекцией нелиней ности, содержащий цепной делитель тока, генератор постоянного тока и управляемые генераторы тока, выходы которых соединены с информационными входа1«1 переключателей тока, первые выходы которых соединены с входами цепного делителя тока, а вторые с общей шиной, блок управления и аналоговые запоминаннцие элементы, ,выходы которых соединены с входами управляемых генераторов тока, о.тличающийся тем, что, с целью повышения быстродействия преобразователя и улучшения технологичности его изготбвления, в него включены регистр сдвига, дополнительный аналоговый запоминающий эле мент, операционный усилитель с дифференциальным входом, первая группа элементов ИЛИ,вторая группа элементов ИЛИ, элементы И и Запрет, по числу разрядов преобразователя, причём выходы каждого предь1цущего из первой группы элементов ИЛИ соединены с первым входом последующего, а у первого из них входы объединены, выходы всех элементрв ИЛИ второй группы и одного элемента И соединены с управлякяцими входами переключателей тока, первые входы элементов ИЛИ второй группы соединены с выходами преобразуемого кода блока управления, вторые входы - с выходами элементов И, а третьи - с выходами элементов Запрет и управляющими входами аналоговых запоминающих элементов, информационные входы которых соединены с выходом операционного усилителя с дифференциальным входом, неинвертирукнций вход которого соединен с выходом цепного делителя тока, а инвертирующий - с выходом дополнительного аналогового запоминакидего элемента, выход синхроимпульсов блока управления соединен с первыми входами элементов и и Запрет , управлякици «1 входом дополнительного аналогового запоминагацего элемента и входом синхронизации регистра сдвига, информационный вход которого соединен с выходом блока управления, а выходы - со вторыми входами элементов Запрет и вторыми входами элементов ИЛИ первой группы, вторые выходы которых соединены со вторыми входами элементов И.

Источники информации, принятые во внимание при экспертизе

1..Авторское свидетельство СССР № 349099, кл. Н 03 К 13/00, 25.07.72

2. Микроэлектронные кодирующие и декодирующие преобразователи. Под ред. Смолова В.Б. Л., Энергия, 1976 (прототип) ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифро-аналоговый преобразователь с автоматической коррекцией нелинейности | 1980 |

|

SU951692A1 |

| Цифро-аналоговый преобразователь с автоматической коррекцией нелинейности | 1980 |

|

SU930651A2 |

| Цифроаналоговый преобразователь | 1980 |

|

SU942258A1 |

| Цифроаналоговый преобразователь | 1979 |

|

SU809547A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1984 |

|

SU1259492A1 |

| Множительно-делительное устройство | 1980 |

|

SU949662A1 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

Авторы

Даты

1981-02-28—Публикация

1979-04-16—Подача