(5) ЦИФРОЛНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ С АВТОМАТИЧЕСКОЙ КОРРЕКЦИЕЙ НЕЛИНЕЙНОСТИ Изобретение относится к аналогоцифровой вычислительной технике и может найти применение в информационноизмерительных системах, системах управления, гибридных вычислительных устройствах. Известно устройство с автоматической коррекцией нелинейности, содержащее основной и корректирующий цифро аналоговые преобразователи (ЦАП), вычислительное устройство, блок управления, компаратор и аналоговый сумматор напряжений L1. Известное устройство обладает слож ной функциональной схемой и ограниченной точностью коррекции нелинейное ти преобразования при воздействии дестабилизирующих факторов,например температуры. Наиболее близким по технической сущности к предлагаемому является цифроаналоговый преобразователь автоматической коррекцией нелинейности, содержащий цепной делитель тока, генератор эталонного тока, п управляемых генераторов тока, п+1 пере-. ключателей тока, п аналоговых запоминающих элементов, регистр.сдвига, первую группу из п и вторую группу из п+1 элементов ИЛИ, инвертирующий усилитель, дополнительный аналоговый запоминающий элемент, п+1 элементов ЗАПРЕТ, п+1 элементов И и блок управления, п информационных выходов которого соединены с первыми входами первой группы элементов ИЛИ, вторые входы которых подключены к выходам элементов ЗАПРЕТ и управляющим входам аналоговых запоминающий устройств, третьи входы п-1 элементов ИЛИ первой группы, соответствующих менее значающим разрядам устройства, соединены с выходами п-1 элементов И, первые входы п элементов И и элементов ЗАПРЕТ подключены к входу синхронизации регистра сдвига и к выходу синхронизации блока управления, выходы элементов ИЛИ первой группы 39 соединены с управляющими входами И переключателей тока, аналоговые входы которых подключены к выходам управляемых генераторов тока, первые выходы переключателей тока соединены с разрядными входами цепного делителя тока, вторые выходы переключателе тока подключены к общей шине, выхЪд п-го элемента И соединен с.управляющим входом (п+1)-го переключателя тока, аналоговый вход которого подключен к выходу генератора эталонного тока, первый выход (п+1)-го переключателя тока соединен с входом менее значащего разряда цепного дели|теля, второй выход (п+1)-го переключателя тока подключен к общей шине, выход инвертирующего усилителя соеди нен с информационным входом дополнительного аналогового запоминающего элемента и с информационными входами других У аналоговых запоминающих элементов, выходы которых подключены к входам управляемых генераторов тока , выход коррекции блока управления соединен с входом записи регистра сдвига, выходы которого подключены к первым входам элементов ИЛИ второй группы и к вторым входам элементов ЗАПРЕТ, выходы элементов ИЛИ второй группы соединены с вторыми входами элементов И и вторыми входами предыд щих элементов ИЛИ второй группы, пер вый и второй входы (п+1)-го элемента ИЛИ второй группы, соответствующего наиболее значащему разряду устройства, подключены к первому входу этого элемента t2. Недостатком такого устройства является ограниченная точность коррекции нелинейности, связанная с нестабильностью импульсной помехи uU , возникающей при переходе дополнитель ного аналогового запоминающего элемента в режим хранения и обусловленной прохождением фронта управляющего сигнала через паразитную емкость переключательного элемента. Цель изобретения - повью ение точности коррекции нелинейности. Поставленная цель достигается тем что в цифроаналоговыйI преобразовате с автоматической коррекцией нелинейности, содержащий цепной делитель то ка, генератор эталонного тока, И управляёмый генераторов тока, И+1 пере ключателей тока, И аналоговых запоми нающих элементов, регистр, сдвига, 2 первую группу из Л и вторую группу из и+1 элементов ИЛИ, инвертирующий усилитель, дополнительный аналоговый запоминающий элемент, И+1 элементов ЗАПРЕТ, и + 1 элементов И и блок управления, и информационных выходов которого соединены с первыми входами первой группы элементов ИЛИ, вторые входы которых подключены к выходам элементов ЗАПРЕТ и управляющим входам аналоговых запоминающих устройств, третьи входы -1 элементов ИЛИ первой группы, соответствующих менее значащим разрядам устройства, соединены с выходами Ц-1 элементов И, первые входы элементов И и элементов ЗАПРЕТ подключены к входу синхронизации регистра сдвига и к выходу синхронизации блока управления, выходы элементов ИЛИ первой группы соединены с управляющими входами И переключателей тока, аналоговые входы которых Подключены к выходам управляемых генераторов тока, первые выходы переключателей тока соединены с разрядными входами ценного делителя тока,вторые выходы переключателей тока подключены к общей шине, выход п-го элемента И соединен с управляющим входом (п+1)-го переключателя тока, аналоговый вход которого подключен к выходу генератора эталонного тока, первый выход (п+1)го переключателя тока соединен с входом менее значащего разряда цепного делителя, второй выход (п+1)-го переключателя тока подключен к общей шине, выход инвертирующего усилителя соединен с информационным входом дополнительного аналогового запоминающего элемента и с информационными входами других п аналоговых запоминающих элементов, выходы которых подключены к входам управляемых генераторов тока, выход коррекции блока управления соединен с входом записи регистра сдвига, выходы которого подключены к первым входам элементов ИЛИ второй группы и к вторым входам элементов ЗАПРЕТ, выходы элементов ИЛИ-второй группы соединены с вторыми входами элементов И и вторыми входами предыдущих элементов ИЛИ второй группы, первый и второй входы (п+1)-го элемента ИЛИ второй группы, соответствующего наиболее значащему разряду устройства, подключен к первому входу этого элемента, введены входной и промежуточный аналоговые зaпo lИнaющиe элементы.

вычитающий усилитель, входной резистор, резистор обратной связи, дополнительный элемент И и блок задержки, вход которого соединен с выходом синхронизации блока управления 5 и первым входом дополнительного элемента И, первый .выход блока задержки подключен к управляющему входу входного аналогового запоминающего элемента, второй выход блока задержки соединен с BtopNM входом дополнительного элемента И, выход которого подключен к управляющему входу промежуточного аналогового запоминающего элемента, третий выход блока задерж- ки соединен с управля ющим входом дополнительного аналогового запоминающего элемента, выход которого через резистор обратной связи подключен к входу инвертирующего усилителя и о первому выводу входного резистора, выход цепного делителя тока соединен с неинвертирующим входом вычитающего усилителя и с информационным входом входного аналогового запоминающего элемента, выход которого подключен к инвертирующему входу вычитающего усилителя, выход вычитающего усилителя соединен с информационным входом промежуточного аналогового запо- 30 минающего элемента, выход которого |Подключен к второму выходу входного резистора.

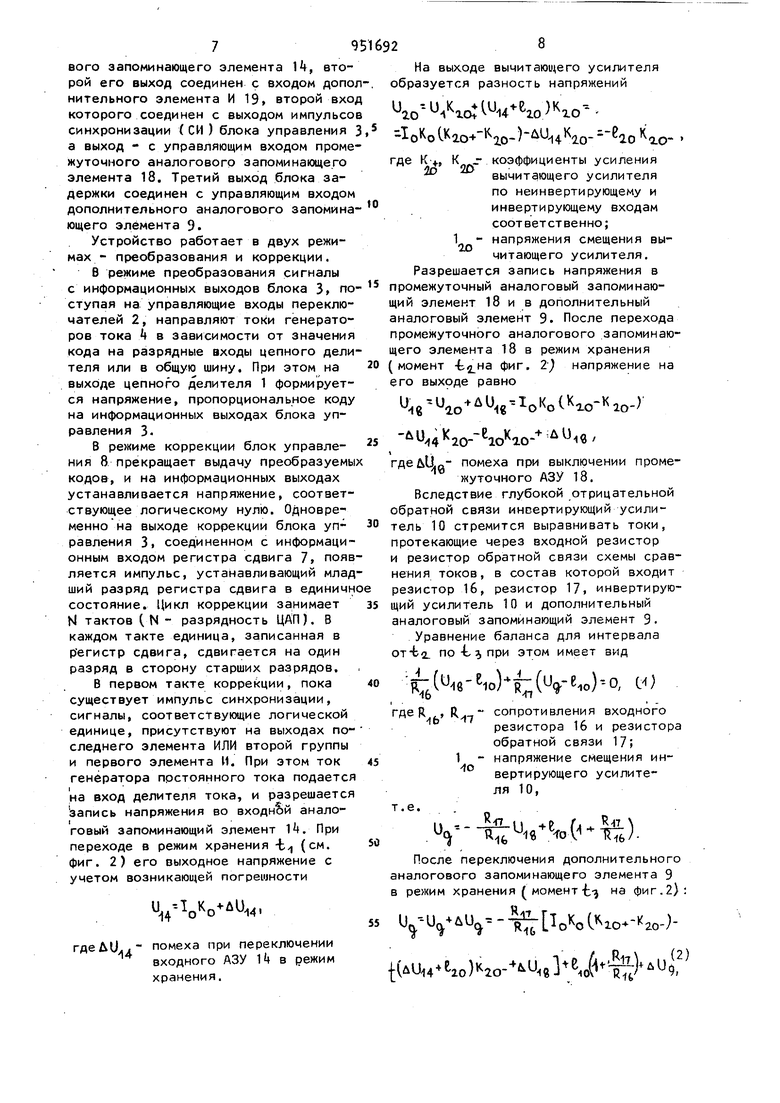

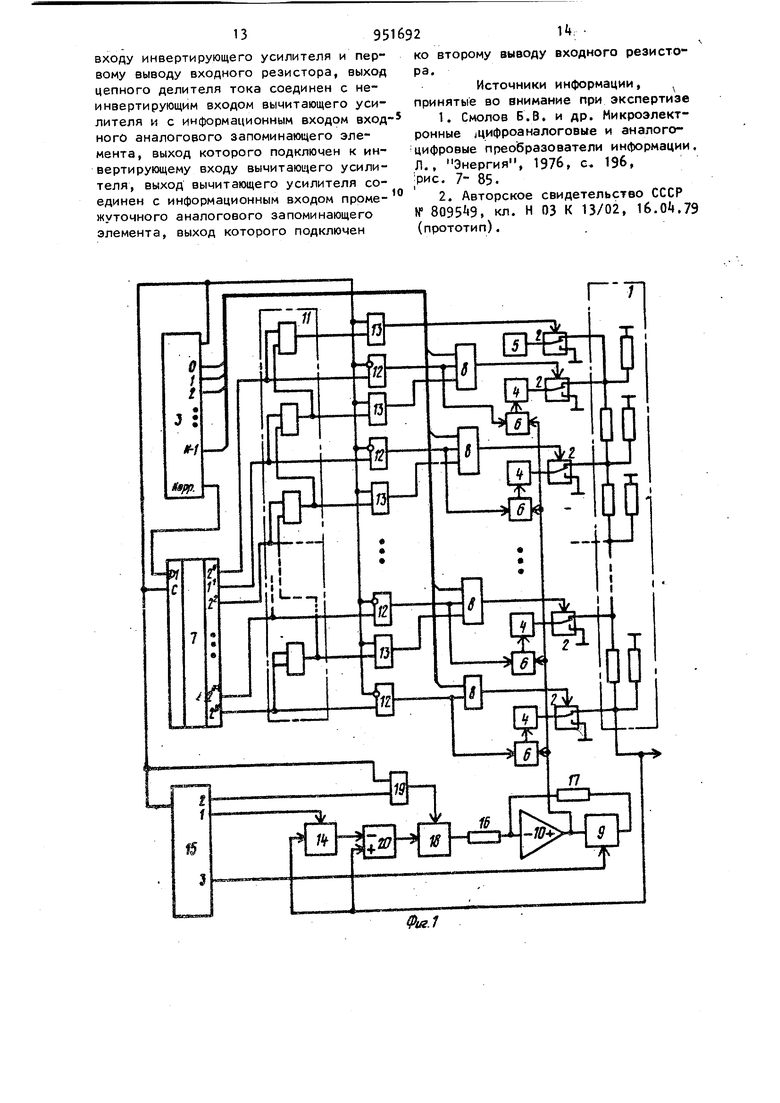

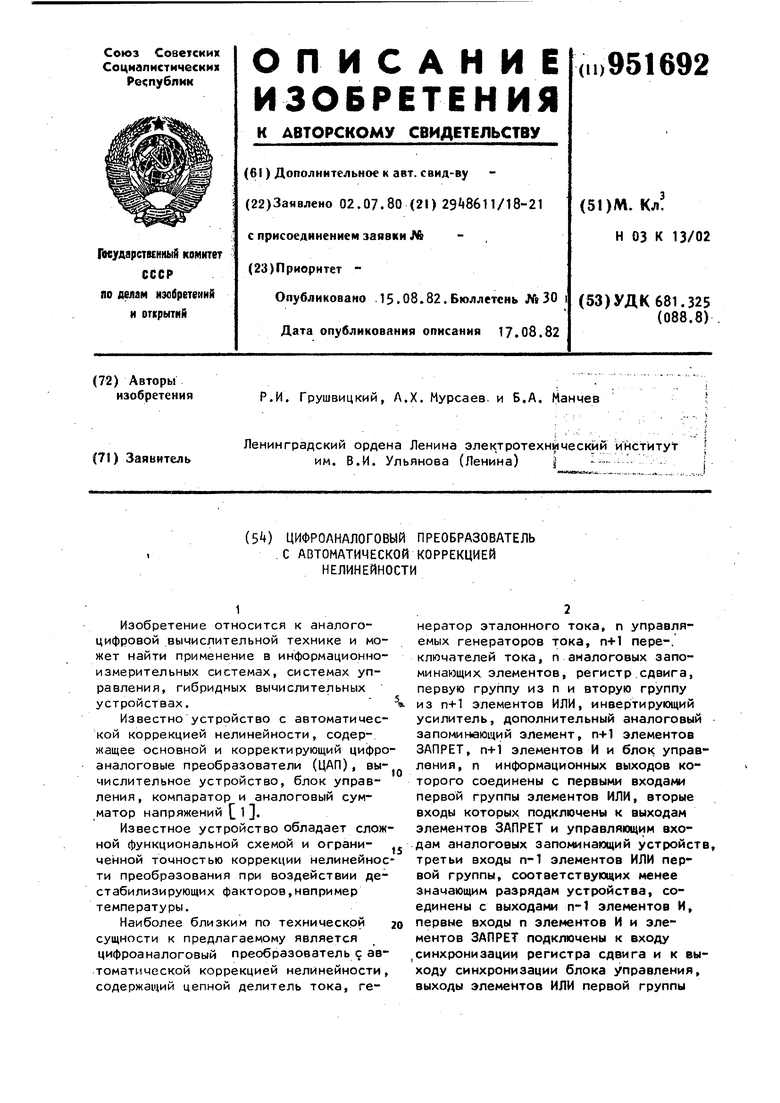

. На фиг. 1 приведена схема устройтва; на фиг. 2 - временная диаграма работы блока задержки.

Устройство содержит цепной делиель тока 1,Vi+1 переключателей тока 2, блок управления 3, управляе440. , , генератор

талонного тока 5,VI аналоговых заоминающих элементов 6, регистр сдвига 7, первую группу из VI элемен-. тов ИЛИ 8, дополнительный аналоговый запоминающий элемент 9 инвертируюий усилитель 10, вторую группу из +1 элементов ИЛИ 11,И+1 элементов ЗАПРЕТ 12,Vi+l элементов И 13г входной аналоговый запоминающий элемент Il, блок задержки 15, входной резистор 1б, резистор обратной связи 17, промежуточный аналоговый запоминающий элемент 18, дополнительный элемент И 19 и вычитающий усилитель 20. Выходы управляемых гене- раторов тока 4 и генератора эталонного тока 5 соединены с информационными входами переключателей тока 2,

первые входы которых соединены с вхо дами цепного делителя тока, а вторые с общей шиной. Входы управляемых генераторов тока 5 соединены с выхода ми аналоговых запоминающих элементов 6. Выходы каждого предыдущего из второй группы элементов ИЛИ 11 соединены с первым входом последующего, а у (п+1)-го из них входы объединены. Выходы всех элементов ИЛИ ; первой группы 8 и одного элемента И 13 соединены с управляющими входами переключателей тока 2. Первые входы элементов ИЛИ первой группы 8 соединены с выхода)«1 преобразуемого кода блока управления 3, вторые - с выходами

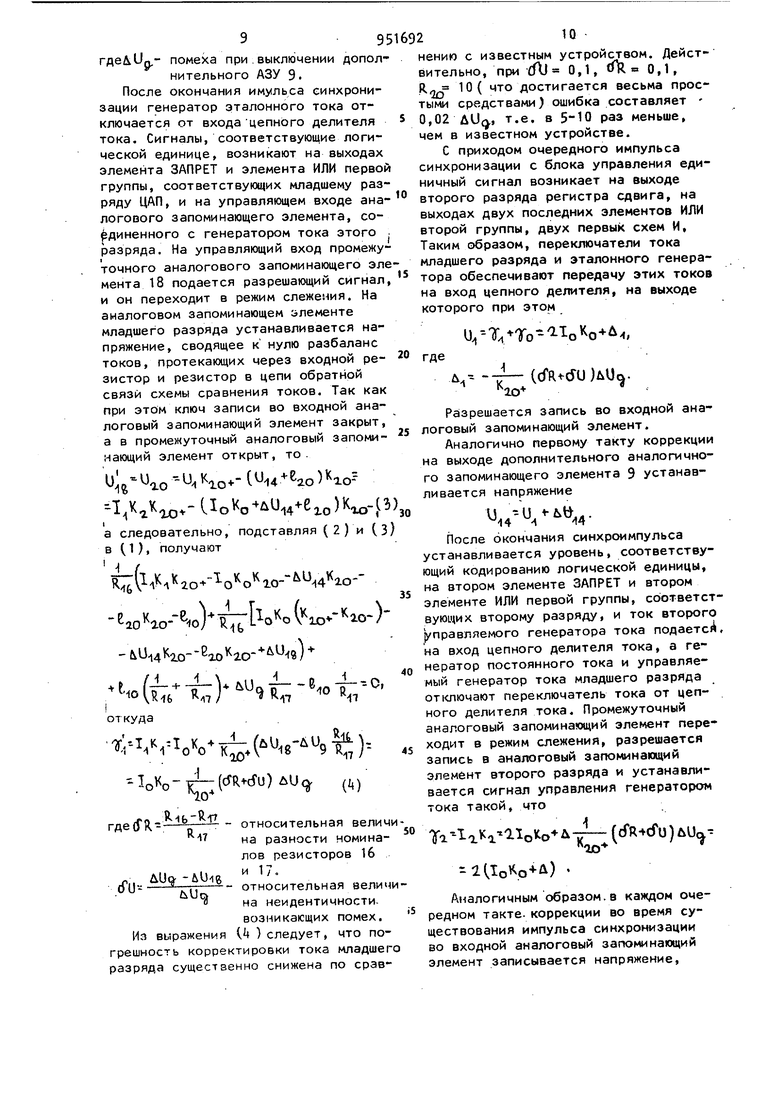

элементов И 13, а третьи - с выходами элементов ЗАПРЕТ 12 и управляющими входами переключателей тока 6. Вы ход синхроимпульсов блока управления 8 соединен с первыми входами элементов И 13 и ЗАПРЕТ 12, управляющим входом дополнительного аналогового запоминающего элемента 9 и входом синхронизации регистра сдвига 7. Информационный вход регистра сдвига 7 соединен с выходом коррекции блка управления 3 а выходы - с вторыми входами элементов ЗАПРЕТ 2 и вто рыми входами элементов ИЛИ второй группы. Выход инвертирующего усилителя 10 соединен с аналоговыми входами аналоговых запоминающих элементов бис .аналоговым входом дополнительного аналогового запоминающего элемента 91 выход которого подключен к первому выводу резистора обратной связи 17. К входу инвертирующего усилителя 10 подключены второй вывод pe (Зистора обратной связи 17 и первый вывод входного резистора 16, второй вывод которого соединен с выходом промежуточного аналогового запоминающего элемента 18. Аналоговый вход промежуточного аналогового зaпo 1нaющего элемента 18 с выходом вычитающего усилителя 20. Первый вход вычитающего усилителя 20 и аналого.вый вход входного аналоговогб запоминающего элемента 1 соединены с выходом цепного делителя тока 1 выход входного аналогового запоминающего элемента соединен с вторым входом вычитающего усилителя. Вход блока задержки 15 соединен с выходом синхроимпульсов блока управления 3. Первый выход блока задержки 15 соединен с управляющим входом входного аналого79вого запоминающего элемента 1, егорой его выход соединен с входом допо нительного элемента И 19, второй вхо которого соединен с выходом импульсо синхронизации (СИ ) блока управления а выход - с управляющим входом проме жуточного аналогового запоминающего элемента 18. Третий выход блока задержки соединен с управляющим входом дополнительного аналогового запомина ющего элемента 9. Устройство работает в двух режимах - преобразования и коррекции. В режиме преобразования сигналы с информационных выходов блока 3, по ступая на управляющие входы переключателей 2, направляют токи генераторов тока h в зависимости от значения кода на разрядные входы цепного дели теля или в общую шину. При этом на выхЬде цепного делителя 1 формируется напряжение, пропорциональное коду на информационных выходах блока управления 3. В режиме коррекции блок управления 8 прекращает выдачу преобразуемы кодов, и на информационных выходах устанавливается напряжение, соответствующее логическому нулю. Одновременно на выходе коррекции блока управления 3, соединенном с информационным входом регистра сдвига 7, появ ляется импульс, устанавливающий млад ший разряд регистра сдвига в единичн состояние. Цикл коррекции занимает Ы тактов (N - разрядность ЦАП). В каждом такте единица, записанная в регистр сдвига, сдвигается на один разряд в сторону старших разрядов. В первом такте коррекции, пока существует импульс синхронизации, сигналы, соответствующие логической единице, присутствуют на выходах последнего элемента ИЛИ второй группы и первого элемента И. При этом ток генератора постоянного тока подается на вход делителя тока, и разрешается запись напряжения во входнЬй аналоговый запоминающий элемент 14. При переходе в режим хранения -t (см. фиг. 2) его выходное напряжение с учетом возникающей погрешности . гдеДи..- помеха при переключении входного АЗУ Т в режим хранения. 28 На выходе вычитающего усилителя образуется разность напряжений .. .i. и (, р i/ 2.О 1 10/ 1О () го-- го г.о- где коэффициенты усиления Г) Vt вычитающего усилителя по неинвертирующему и инвертирующему входам соответственно; 1 - напряжения смещения выючитающего усилителя. Разрешается запись напряжения в промежуточный аналоговый запоминающий элемент 18 и в дополнительный аналоговый элемент 9. После перехода промежуточного аналогового запоминающего элемента 18 в режим хранения (момент 4:.на фиг. 2) напряжение на $го выходе равно ,( -ли К -t К .+ ди fl где&Ц,.- помеха при выключении промежуточного АЗУ 18. Вследствие глубокой отрицательной обратной связи инвертирующий усилитель 10 стремится выравнивать токи, протекающие через входной резистор и резистор обратной связи схемы сравнения токов, в состав которой входит резистор 16, резистор 17, инвертирующий усилитель 10 и дополнительный аналоговый запоминающий элемент 9. Уравнение баланса для интервала OT-fei по-t. 3, при этом имеет вид 4(e-O-(VU-o, гдеR , R - сопротивления входного резистора 16 и резистора обратной связи 17; 1 - напряжение смещения вертирующего усилителя 10, ). После переключения дополнительного аналогового запоминающего элемента 9 в режим хранения ( момент-t фиг.2): и -и -ли - 1оКоСК о--К о. (4.o),).

995169210

гдеЛУр,- помеха при . выключении допол- нению с известным устройством. Дейстнительного АЗУ 9. После окончания имульса синхронизации генератор эталонного тока отключается от входа цепного делителя тока. Сигналы, соответствующие логической единице, возникают на выходах элемента ЗАПРЕТ и элемента ИЛИ первой группы, соответствующих младшему разряду ЦАП, и на управляющем входе ана-®второго разряда регистра сдвига, на

логового запоминающего элемента, со-выходах двух последних элементов ИЛИ

единенного с генератором тока этого .второй группы, двух первый схем И,

разряда. На управляющий вход промежу-Таким образом, переключатели тока

точного аналогового запоминающего эле-младшего разряда и эталонного генерамента 18 подается разрешающий сигнал, тора обеспечивают передачу этих токов и он переходит в режим слежения. На аналоговом запоминающем элементе младшего разряда устанавливается напряжение, сводящее к нулю разбаланс токов, протекающих через входной резистор и резистор в цепи обратной связи схемы сравнения токов. Так как при этом ключ записи во входной аналоговый запоминающий элемент закрыт а в промежуточный аналоговый запоминающий элемент открыт, то . ()Чо,,) W а следовательно, подставляя (2) и (З в 1 ) получают , . (,гo о 20 0 0 10- |4 10r-0 irlo o( ,4Kio--EюЧo- %) /d, X -.. откуда ()- -Vo-iq H rfu)Au (Ц) л гдеаЯ-- -- относительная велич на разности номиналов резисторов 16 и 17. л . AUq- -&Uie hUt относительная велич на неидентичностивозиикающих помех. Из выражения (k ) следует, что погрешность корректировки тока младшег разряда существенно снижена по сраввительно, при 0,1, tHl 0,1, R.,jQ 10{ что достигается весьма простыми средствами) ошибка составляет S 0,02 uU(v. т.е. в 5 10 раз меньше, чем в известном устройстве.

С приходом очередного импульса синхронизации с блока управления единичный сигнал возникает на выходе на вход цепного делителя, на выходе которого при этом 0,--Ti To-2.IoKo+A,, л,-- ((fR rfUMUa. Srt+ Разрешается запись во входной аналоговый запоминающий элемент. Аналогично первому такту коррекции на выходе дополнительного аналогичного запоминающего элемента 9 устанавливается напряжение Ч4--..4После окончания синхроимпульса устанавливается уровень, соответствующий кодированию логической единицы, на втором элементе ЗАПРЕТ и втором элементе ИЛИ первой группы, соответствующих второму разряду, и ток второго управляемого генератора тока подается, на вход цепного делителя тока, а генератор постоянного тока и управляемый генератор тока младшего разряда отключают переключатель тока от цепного делителя тока. Промежуточный аналоговый запоминахщий элемент переходит в режим слежения, разрешается запись в аналоговый запокмнающий элемент второго разряда и устанавливается сигнал управления генератором тока такой, что Тг-1г г 1о о Д1Г ( Ллл -H,) Аналогичным образом.в каждом очередном такте, коррекции во время существования импульса синхронизации во входной аналоговый запоминающий элемент записывается напряжение. paencre (с точностью до напряжения по мехи, возникающего при переходе элег мента в режим хранения) сумме весовых коэффициентов всех младших i-l разрядов и эталонного, а после окончания импульса синхронизации на аналоговом запоминающем элементе i-ro разряда устанавливается такое напря.жение, что весовой коэффициент этого разряда становится равным , , . При этом выбором коэффициента cfR близким к единице и при использовани вычитающего усилителя с достаточно большим коэффициентом передачи по на пряжению Кд суще ственно уменьшается величина погрешности, вносимой анало говым запоминающим элементом при переходе в режим хранения. По сравнени с известным устройством погрешность KIO уменьшается в Формула изобретения Цифроаналоговый преобразователь с автоматической коррекцией нелинейности , содержащий цепной делитель то ка, генератор эталонного тока, И управляемых генераторов, тока, И + 1 переключателей тока, и аналоговых запоминающих элементов, регистр сдвига первую группу из и и вторую группу изМ+1 элементов ИЛИ, инвертирующий усилитель, дополнительный аналоговый запоминающий элемен-, И-fl элементов ЗАПРЕТ, элементов И и блок управ ления, VI информационных выходов которого соединены с первыми входами первой группы элементов ИЛИ, вторые входы которых подключены к выходам глементов ЗАПРЕТ и управляющим входам аналоговых запоминающих устройст третьи входы Ц-1 элементов ИЛИ пербой группы, соответствующих менее значащим разрядам устройства, соединены с выходами И-1 элементов И, первые входы и элементов И и элементов ЗАПРЕТ подключены к входу синхронизации регистра сдвига и к выходу синхронизации блока управлени Ёыходы элементов ИЛИ первой группы соединены с управляющими входами Vi переключателей тока, аналоговые входы которых подключены к выходам управляемых генераторов тока, первые выходы переключателей тока соединены с разрядными входами цепного делителя тока, вторые выходы переключателей тока подключены к общей шине, выход и-гй элемента И соединен с управляющим входом (и+l)-го переключателя тока, аналоговый вход которого подключен к выходу генератора эталонного тока,первый выход(и +1)-го переключателя тока соединен с входом менее значащего разряда цепного делителя, второй выход( переключателя тока подключен к общей шине, выход инвертирующего усилителя соединен с информационным входом дополнительного аналогового запоминающего элемента и с информационными входами других аналоговых запоминающих элементов. выходы которых подключены к входам управляемых генераторов тока, выход коррекции блока управления соединен с информационным входом регистра сдвига, выходы которого подключены к первым входам элементов ИЛИ второй группы и к вторым входам элементов ЗАПРЕТ, выходы элементов ИЛИ второй группы соединены с вторыми входами элементов И и вторыми входами предыдущих элементов ИЛИ второй группы, первый и второй входы.(и + U-ro элемента ИЛИ второй группы, соответствующего наиболее значащему разряду, объединены между собой,отличающий с я тем, что, с целью повышения точности коррекции нелинейности, в него введены входной и промежуточный аналоговые запоминающие элементы, вычитающий усилитель, входной резистор, резистор обратной связи, дополнительный элемент И и блок задержки, вход которого соединен с выходом синхронизации блока управления и первым входом дополнительного элемента И, первый выход блока задержки подключен к управляющему входу входного аналогового Запоминающего элемента, второй выход блока задержки соединен с вторым входом дополнительного элемента И, выход которого подключен к управляющему входу промежуточного аналогового запоминающего элемента, третий выход блока задерж| и соединен с управляющим входом дополнительного аналогового запоминающего элемента, выход которого через резистор обратной связи подключен к входу инвертирующего усилителя и первому выводу входного резистора, выход цепного делителя тока соединен с неинвертирующим входом вычитающего усилителя и с информационным входом вход ногО аналогового запоминающего элемента, выход которого подключен к инвертирующему входу вычитающего усилителя, выход вычитающего усилителя соединен с информационным входом промежуточного аналогового запоминающего элемента, выход которого подключен ко второму выводу входного резистора. Источники информации, принятые во внимание при экспертизе 1.Смолов Б.В, и др. Микроэлектронные щифроаналоговые и аналогоцифровые преобразователи информации. Л., Энергия, 1976, с, 196, |рис. 7-85. 2.Авторское свидетельство СССР № 8095«9, кл. Н 03 К 13/02, 16.01.79 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразовательС АВТОМАТичЕСКОй КОРРЕКциЕй НЕли-НЕйНОСТи | 1979 |

|

SU809549A1 |

| Цифро-аналоговый преобразователь с автоматической коррекцией нелинейности | 1980 |

|

SU930651A2 |

| Цифроаналоговый преобразователь | 1980 |

|

SU942258A1 |

| Цифроаналоговый преобразователь | 1979 |

|

SU809547A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1448292A1 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ БИОЛОГИЧЕСКОЙ АКТИВНОСТИ МОЗГА | 1993 |

|

RU2076625C1 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| Устройство для формирования последовательностей импульсов | 1989 |

|

SU1653140A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

Фиг. 2

Авторы

Даты

1982-08-15—Публикация

1980-07-02—Подача