1

Изобретение относится к измерительной технике и может быть применено при измерении неповторяющихся

интервалов времени с высокой точностью.

Известно устройство, содержащее в каждом канале многоразрядный счетчик и блок суммирования 1 .

Недостатком этого устройства является его сложность и наличие избыточной информации.

Наиболее близким к предлагаемому изобретению является устройство, содержащее один многоразрядный счетчик, дополнительный счетчик, линию задержки, вентили и двухразрядные счетчики 2.

Недостатками этого устройства являются низкие надежность и котрол.ь измерений.

Цель изобретения - повышение надежности и улучшение контроля измерений .

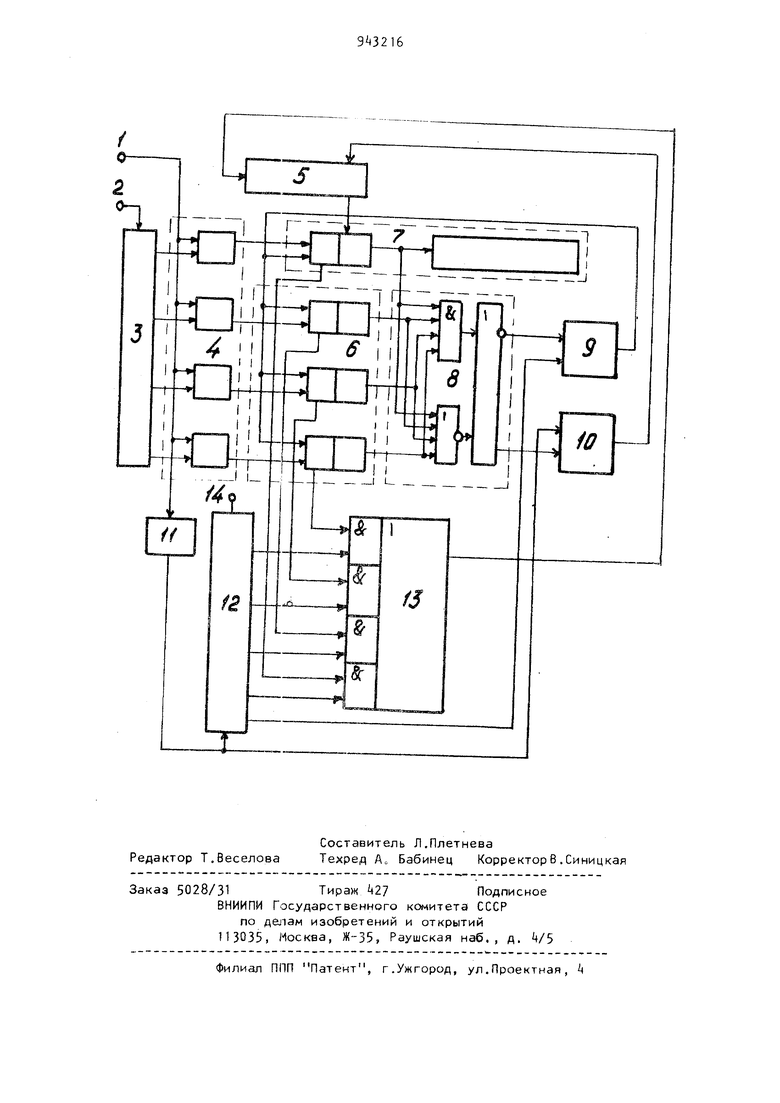

Указанная цель достигается тем, что в устройство, содержащее линию задержки, блок вентилей, основной счетчик, блок двухразрядных счетчиков и дополнительный счетчик, шина тактовых импульсов подключена к входу линий задержки, отводы которой соединены с входами вентилей, выходы которого соединены с входом младшего разряда основного счетчика и входами младших разрядов блока двухраз;рядных счетчиков соответственно, управляющие входы блока вентилей сов динены с шиной входного сигнала, вы,5 ход старшего разряда дополнительного счетчика подключен к входу второго разряда основного счетчика, введены два элемента И, блок логической эквивалентности, формирователь, допол20нительная линия задержки и элемент И-ИЛИ, причем входная шина через формирователь подключена к перво му входу первого элемента И и к вхо3ду дополнительной линии з держки, первый отвод которой с пер BbiM входом второго элемента И, а все последующие отводы сое:динены с первой группой входов элемента И-ИЛ вторая группа входов котор-ого подкл чена к выходам младших разрядов основного счетчика и блока двухразряд ных счетчиков, выход элемента И-ИЛИ подключен к входу младшегс разряда дополнительного счетчика, выходы вторых разрядов основного счетчика и блока двухразрядных счетчиков под ключены к входам блока логической эквивалентности, прямой которого соединен с вторым входом перво го элемента И, а инверсный выход со вторым входом второго элемента И выход первого элемента И соединен с входом старшего разряда дополнительного счетчика, а выход второго элемента И соединен с входами младших разрядов основного счетчик.а и блока двухразрядных счетчиков. На чертеже приведена функциональнал схема устройства. Схема содержит шину 1 входную, шину 2 такто.а1х импульсов, линию 3 задержки, Олок А вентилей, дополнительный С:етчик 5 блок 6 двухразрядных чиков, основной счетчик 7 блок 8 лс/ической экв1.&аяе тности, состоящий; например, из элt-мe iтoв И, ИЛИ-НЕ и ИЛИ, элементы 9 и 1C И, фор мирователь 11, дополнительную линию задержки, элемент 13 И-ИЛИ и 1 4 сигнала окончания измерение, Для определенности число каналов выбрано р а в н ь1 м ч е г ы р е м . Устройство работает следующим образом. В исходном состоянии а счетчиках блока 6 и счетчике 7 устан дален код минус единица, счетчик 5 обнулен. Измеряемый интервал времени в виде прямоугольного импульса напряжения поступает по шине и открывает вен тили блока , при этом тактовые импульсы, подаваемые по шине 2, начинают проходить с отводов линии задержки 3 на входы счетчиков блока 6 и счетчика 7- Окончание входного им пульса сопровождается запиранием вентилей блока k и выработкой форми рователем И одиночного импульса, поступающего на линию 12 задержки и на вход элемента 10 И. В случае эквивалентности вторых разрядов 64 блок 8 открывает элемент 10 И и импульс формирователя i1 проходит на Вход старшего разряда счетчика 5. В случае неэквивалентности вторых разрядов открывается элемент 9 И и импул ьс .формирователя 11 прсзходит на вход старшего разряда счетчика 5- 6 случае неэквивалентности вторых разрядов открывается элемент 9 И и одиночный импульс с первого (зтвода линии 12.задержки поступает на входы младших разрядов счетчиков блока 6 и счетчика 7, при этом эквивалентность вторых разрядов должна быть восстановлена. Единичные состояния младших разрядов счетчиков блока 6 и счетчика 7 преобразуются линией 12 задержки и элементом 13 И-ИЛИ в последовательность орректир Ющих импульсов, которые подаются на вход счетчика 5, образуя младшие разряды результата. Отсутствие эквивале.нтности вторых разрядов в момент появления сигнала на шине k свидетельствует о недостоверности результата. Предлагаемое устройство при подготовке условий выработки корректирующего кода реализует лишь одно логическое выражение: i , ч- В„ + в, + ,4-- о + Ь| + . . . + В., В. , состо.яния ;-го, 2-го (N- i } --го разряда соответственно ос н ов но г о -: ч е т ч и к а, -состояние второго разряд а д в у X р -з з р .ч д ного счетчика. -состояние вторО о разряда осно.еного счетчика.. Устройство содержит два N-Bxcxqoвых элемента И и один двухвходовый, соответствует цене по Квайну .;:N + 2 (N- общее число каналоЕз) , Известное устройство, выполняюшее а каждом канале, за исключением основного , две операции установления эквивалентности и одну операцию Если-Tof может быть оценено по Квайну как 1 .(N-1) . Таким образом, предлагаемое устройство имеет в несколько раз более простую логическую схему. Кроме того, конечное состояние вторых разрядов позволяет обнаруживать сбой в кана59лах, в результате которых образуются три различные числа импульсов в кана лах, при отсутстЕзии сбоев числа импульсов в каналах не отличаются друг от друга более чем на единицу. При эквивалентности вторых разрядах и отличии чисел не более чем на единицу, эквивалентны все старшие разряды а сумма этих чисел может быть получена путем умножения содержания разрядов от старшего до второго включительно на число каналов с добавлением единиц, содержащихся в младших разрядах всех каналов. При числе каналов, равном 2, k, 8 ...., операция умножения сводится к соответственному сдвигу всех разрядов влево. Если после окончания счета вторые разряды взаимно неэквивалентны, то добавление по одному импульсу в каждый канал восстанавливает эквивалентност вторых разрядов, если и после подачи импульсов эквивалентность не восстанавливается, то это говорит о наличии сбоя и о недостоверности результата. Чтобы добавление в каждый кана по одному импульсу не нарушало общего числа импульсов, во всех каналах предварительно записывают код Минус единица(единица во всех разрядах), которое после проведения измерения компенсируют либо подачей одного импульса в старший разряд дополнительного счетчика, либо по одному импуль су в каждый младший разряд при попыт ке восстановления эквивалентности вт рых разрядов. Независимость каналов оценки эквивалентности и выработки корректи-, рующих импульсов позволяет легко KOH ролировать работу этих узлов, а прос тота логической схемы создает высоку надежность. Таким образом, применение данного устройства позволяет повысить надежность работы и осуществлять контроль работы устройства- при каждом измерении. Формула изобретения Измеритель одиночных интервалов времени, содержащий линию задержки, блок вентилей, основной счетчик. блок двухразряднь1Х счетчиков и дополнительный счетчик, шина тактовых импульсов подключена к входу линии задержки, отводы которой соединены с входами блока вентилей, выходы которого соединены с входом младшего разряда основного счетчика и входами младших разрядов блока двухразрядных счетчиков соответственно, управ ляющие входы блока вентилей соединены с шиной входного сигнала, выход старшего разряда дополнительного счетчика подключен к входу второго разряда основного счетчика, отличающийся тем, что, с целью повышения надежности и улучшения контроля измерений, в него введены два элемента И, блок логической эквивалентности, формирователь, дополнительная линия задержки и элемент И-ИЛИ, причем входная шина через формирователь подключена к первому дходу первого элемента И и к входу дополнительной линии задержки, первый отвод которой соединен с первым входом второго элемента И, а все последующие отводы соединены с первой группой входов элемента И-ИЛИ, вторая группа входов которого подключена к выходам младших разрядов основного счетчика и блока двухразрядных счетчиков, выход элемента И-ИЛИ Г1с;;зключеп к входу шедшего разряда допгхчиител ьного сче чик-з, выходы вторых разрядов основного счетчика и блока двухразрядных счет чиков подключены к входам блока логической эквивалентности, прямой выход которого соединен с вторым входом первого элемента И, а инверсный выход - с вторым входом второго элемента И, выход первого элемента И соединен с входом старшего разряда, дополнительного счетчика, а выход второго элемента И соединен с входами младших разрядов основного счетчика и блока двухразрядных счетчиков . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 17235, кл. G F W/Ok, 1959. 2.Авторское свидетельство СССР № 390501, кл. G 0 F , 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель одиночных интервалов времени | 1982 |

|

SU1132278A1 |

| Измеритель временных параметров случайных импульсных потоков | 1988 |

|

SU1575135A1 |

| Моментный вентильный электродвигатель | 1988 |

|

SU1751836A1 |

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ В ЦИФРОВОЙ КОД | 1973 |

|

SU391587A1 |

| Многоканальный преобразователь напряжения в код | 1982 |

|

SU1109900A1 |

| Цифровой управляемый делитель частоты следования импульсов | 1980 |

|

SU869054A1 |

| Устройство для задержки импульсов | 1981 |

|

SU993455A1 |

| Многоканальный измеритель временных характеристик последовательности дискретных сигналов | 1987 |

|

SU1442971A1 |

| Многоканальный генератор импульсов | 1977 |

|

SU670067A1 |

Авторы

Даты

1982-07-15—Публикация

1980-12-11—Подача