Изобретение относится к электротехнике и может быть использовано в прецизионных синхронных следящих системах.

Цель изобретения - повышение стабильности момента по углу поворота и улучшение динамических характеристик.

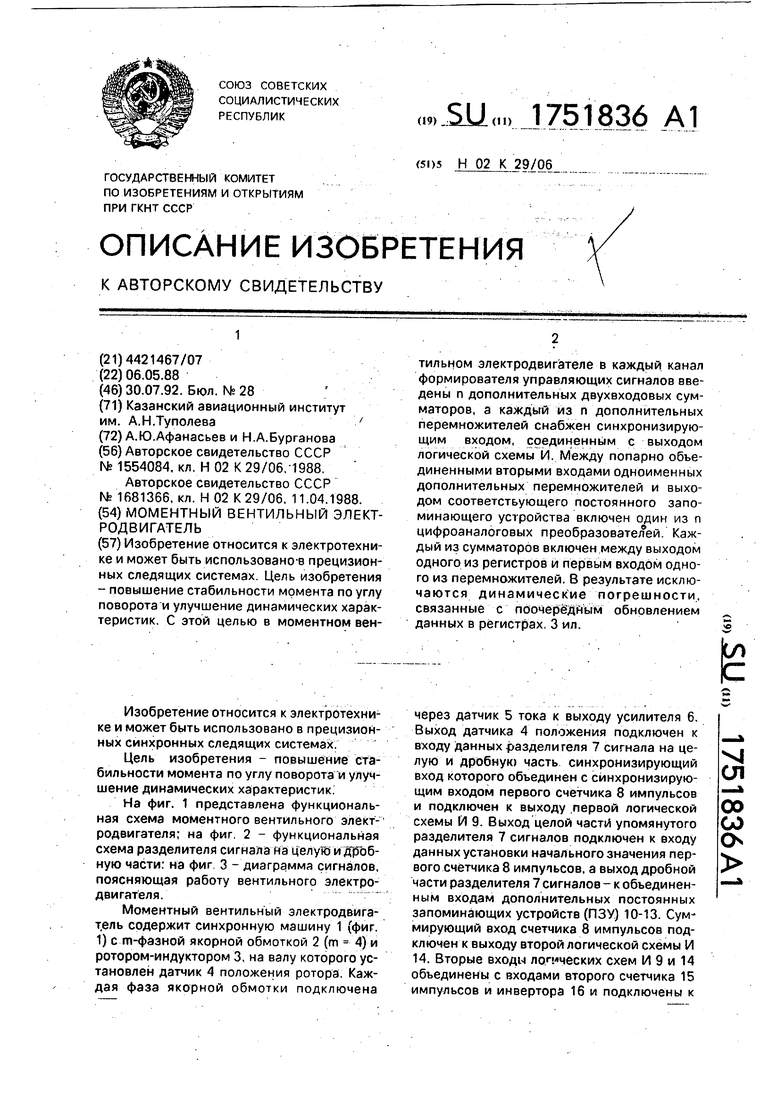

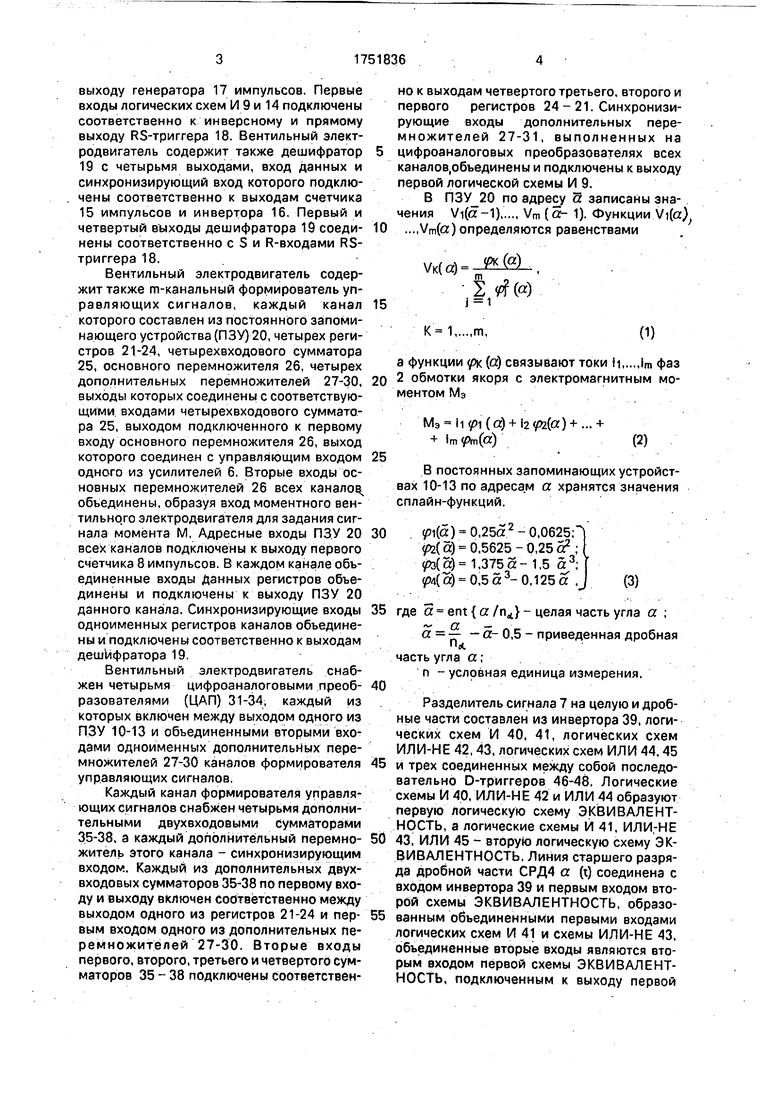

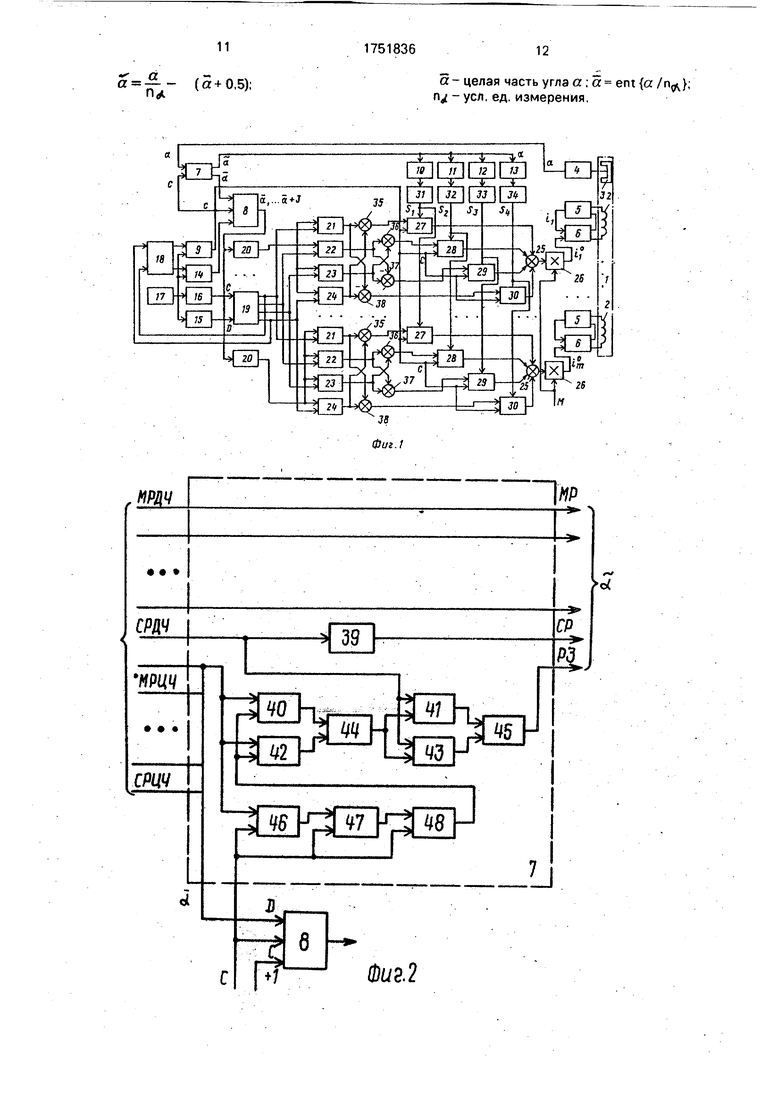

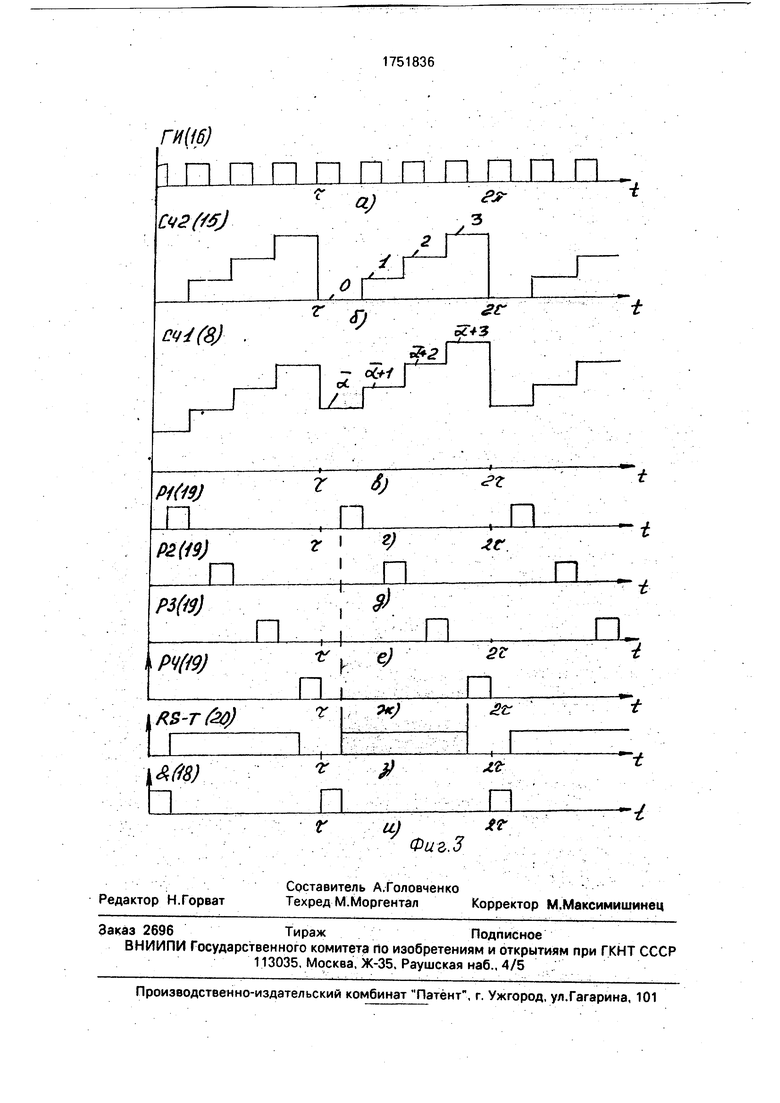

На фиг. 1 представлена функциональная схема моментного вентильного электродвигателя; на фиг. 2 - функциональная схема разделителя сигнала на целую и дробную части: на фиг 3 - диаграмма сигналов, поясняющая работу вентильного электродвигателя.

Моментный вентильный электродвигатель содержит синхронную машину 1 (фиг. 1) с m-фазной якорной обмоткой 2 (т 4) и ротором-индуктором 3, на валу которого установлен датчик 4 положения ротора. Каждая фаза якорной обмотки подключена

через датчик 5 тока к выходу усилителя 6, Выход датчика 4 положения подключен к входу данных разделителя 7 сигнала на целую и дробную часть синхронизирующий вход которого объединен с синхронизирующим входом первого счетчика 8 импульсов и подключен к выходу первой логической схемы И 9. Выход целой части упомянутого разделителя 7 сигналов подключен к входу данных установки начального значения первого счетчика 8 импульсов, а выход дробной части разделителя 7 сигналов - к объединен- ным входам дополнительных постоянных запоминающих устройств (ПЗУ) 10-13. Суммирующий вход счетчика 8 импульсов подключен к выходу второй логической схемы И 14. Вторые входы логических схем И 9 и 14 объединены с входами второго счетчика 15 импульсов и инвертора 16 и подключены к

VI

сл

CD Сл) О

выходу генератора 17 импульсов. Первые входы логических схем И 9 и 14 подключены соответственно к инверсному и прямому выходу RS-триггера 18. Вентильный электродвигатель содержит также дешифратор 19 с четырьмя выходами, вход данных и синхронизирующий вход которого подключены соответственно к выходам счетчика 15 импульсов и инвертора 16. Первый и четвертый выходы дешифратора 19 соеди- йены соответственно с S и R-входами RS- триггера 18.

Вентильный электродвигатель содержит также m-канальный формирователь управляющих сигналов, каждый канал которого составлен из постоянного запоминающего устройства (ПЗУ) 20, четырех регистров 21-24, четырехвходового сумматора 25, основного перемножителя 26, четырех дополнительных перемножителей 27-30, выходы которых соединены с соответствующими входами четырехвходового сумматора 25, выходом подключенного к первому входу основного перемножителя 26, выход которого соединен с управляющим входом одного из усилителей 6. Вторые входы основных перемножителей 26 всех каналов объединены, образуя вход моментного вентильного электродвигателя для задания сигнала момента М, Адресные входы ПЗУ 20 всех каналов подключены к выходу первого счетчика 8 импульсов. В каждом канале объединенные входы Данных регистров объединены и подключены к выходу ПЗУ 20 данного канала. Синхронизирующие входы одноименных регистров каналов объединены и подключены соответственно к выходам дешифратора 19.

Вентильный электродвигатель снабжен четырьмя цифроаналоговыми преоб- разователями (ЦАП) 31-34, каждый из которых включен между выходом одного из ПЗУ 10-13 и объединенными вторыми входами одноименных дополнительных перемножителей 27-30 каналов формирователя управляющих сигналов.

Каждый канал формирователя управляющих сигналов снабжен четырьмя дополнительными двухвходовыми сумматорами 35-38, а каждый дополнительный перемно- житель этого канала - синхронизирующим входом. Каждый из дополнительных двух- входовых сумматоров 35-38 по первому входу и выходу включен соответственно между выходом одного из регистров 21-24 и пер- вым входом одного из дополнительных перемножителей 27-30. Вторые входы первого, второго, третьего и четвертого сумматоров 35 - 38 подключены соответственно к выходам четвертого третьего, второго и первого регистров 24 - 21. Синхронизирующие входы дополнительных перемножителей 27-31, выполненных на цифроаналоговых преобразователях всех каналов,объединены и подключены к выходу первой логической схемы И 9.

В ПЗУ 20 по адресу и записаны значения Vi(a-1)Vm (a- 1). Функции Vi(a

...,Vm(a) определяются равенствами

Ук(Ф

УК(«)

m

2 rf(«) j i

К 1m,

(1)

а функции рк (а) связывают токи fi,.,.,im фаз 2 обмотки якоря с электромагнитным моментом Мэ

Мэ И р («) + ia рг(а) + ... + + (а)(2)

В постоянных запоминающих устройствах 10-13 по адресам а хранятся значения сплайн-функций.

0,25а2- 0,0625;

pi(«)

pi{ а) 0,5625 - 0,25 а2,,;

рз( а) 1,375(.

р4(а) 0,5 а3-0,125 а ,

где а em {а /ПА} - целая часть угла а ;

СС -

а - - а- 0,5 - приведенная дробная

пл часть угла а ;

п - условная единица измерения,

Разделитель сигнала 7 на целую и дробные части составлен из инвертора 39, логических схем И 40, 41, логических схем ИЛИ-НЕ 42,43, логических схем ИЛИ 44,45 и трех соединенных между собой последовательно D-триггеров 46-48. Логические схемы И 40, ИЛИ-НЕ 42 и ИЛИ 44 образуют первую логическую схему ЭКВИВАЛЕНТНОСТЬ, а логические схемы И 41, ИЛИ-НЕ 43, ИЛИ 45 - вторую логическую схему ЭКВИВАЛЕНТНОСТЬ. Линия старшего разряда дробной части СРД4 a (t) соединена с входом инвертора 39 и первым входом второй схемы ЭКВИВАЛЕНТНОСТЬ, образованным объединенными первыми входами логических схем И 41 и схемы ИЛИ-НЕ 43. объединенные вторые входы являются вторым входом первой схемы ЭКВИВАЛЕНТНОСТЬ, подключенным к выходу первой

схемы ЭКВИВАЛЕНТНОСТЬ, который образован выходом логической схемы ИЛИ 44.

Шина младшего разряда МРЦ4 целой части а (т) соединена со входами схемы И 40, схемы ИЛИ-НЕ 42, образующих первый вход первой схемы ЭКВИВАЛЕНТНОСТЬ, и со входом данных D-триггера 46. Вход синхронизации разделителя 7 образован входами синхронизации D-триггеров 46, 48 и инверсным входом синхронизации D-триггера 47. Выход D-триггера 46 подключен ко входу данных D-триггера 48, выход которого подключен ко входу данных D-триггера 48. Его выход подключен ко вторым входам схемы И 40 и схемы ИЛИ-НЕ 42, образующих второй вход первой схемы ЭКВИВАЛЕНТ- НОСТЬ. Выход инвертора 39 образует шину старшего разряда выхода дробной части а, шины остальных ее разрядов совпадают с соответствующими линиями разрядов дробной части a(t), а выход схемы ИЛИ 45 явля- ется шиной разряда знака дробной части а Шины МРЦ4и СРЦ4 образуют шины выхода целой части a(t) разделителя 7 сигнала,

Электродвигатель работает следующим образом.

Датчик 4 угла вырабатывает сигнал, пропорциональный углу а поворота ротора- индуктора 3. Этот сигнал поступает на разделитель 7 сигнала на целую а и дробную а. части. Сигнал а в цифровой форме по- ступает на адресные входы ПЗУ 10-13. На их выходах вырабатываются цифровые коды, соответствующие значениям сплайн-функций:

р ,25 а2-0,0625, р2 0,5625 - 0,25 а2- ,375а- 1,5 И3;

sv 3

,5 а -0,125а. J

5 1015 20

25

30

35

40

рого поступают импульсы поочередно Р1(19), Р2(19), Р3(19), Р4(19) на входы данных .ззгистров 21-24 (фиг. 4, г-ж).

Импульс Р4(19) с четвертого выхода дешифратора 19 устанавливает RS-триггер 18 в состояние 0 (фиг. 4 з). С его инверсного выхода поступает единичный сигнал RS- Т(20) на вход логической схемы И 9, и во время очередного импульса генератора 16 импульсов она вырабатывает синхронизирующий импульс & (18) (фиг. 4 и). Этот импульс приходит на синхронизирующие входы разделителя 7 сигнала, счетчика 8 и цифроаналоговых преобразователей 27-30. В разделителе 7 фиксируется младший разряд целой части а, в счетчик 8 записывается целая часть а, во входные регистры ЦАП 27-30 записываются выходные сигналы сумматоров 35-38.

Импульс с первого выхода дешифратора 19 устанавливает RC-триггер 18 в состояние 1 (фиг. 4 з). С его прямого выхода поступает единичный сигнал на вход логической схемы И 14 и три очередных импульса генератора 16 проходят на суммирующий вход счетчика 8. На его выходе вырабатываются цифровые коды а ,а + 1, а + 2,а + 3, поступающие на адресные входы ПЗУ 20. На их выходах получаются цифровые коды VK(«-I), VK(a), VK(5 + 1). VK(a+2). ,.. ,m, которые записываются, соответственно в регистры 21-24, Эти коды приходят на сумматоры 35-38, на выходах которых вырабатываются цифровые сигналы.

VK( а -1) + VK( а + 2). V« (а) + Vk(a + 1), VK( a + 1) - VK(a). VK(a + 2) - VK(« - 1).

Они поступают на цифровые входы ЦАП 27-30, на выходах которых получаются аналоговые сигналы

| название | год | авторы | номер документа |

|---|---|---|---|

| Моментный вентильный электродвигатель | 1988 |

|

SU1751837A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Устройство для перемещения магнитной ленты | 1990 |

|

SU1697113A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

| СИСТЕМА ДЛЯ ИДЕНТИФИКАЦИИ ОБЪЕКТОВ | 2003 |

|

RU2276796C2 |

| Адаптивное устройство компенсации эхосигнала | 1988 |

|

SU1577076A1 |

| Устройство для селекции изображений объектов | 1986 |

|

SU1464183A1 |

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1255984A2 |

Изобретение относится к электротехнике и может быть использовано В прецизионных следящих системах. Цель изобретения - повышение стабильности момента по углу поворота и улучшение динамических характеристик. С этой целью в моментном вентильном электродвигателе в каждый канал формирователя управляющих сигналов введены п дополнительных двухвходовых сумматоров, а каждый из п дополнительных перемножителей снабжен синхронизирующим входом, соединенным с выходом логической схемы И. Между попарно объединенными вторыми входами одноименных дополнительных перемножителей и выходом соответствующего постоянного запоминающего устройства включен один из п цифроаналоговых преобразователей. Каждый из сумматоров включен между выходом одного из регистров и первым входом одного из перемножителей. В результате исключаются динамические погрешности, связанные с поочерёдным обновлением данных в регистрах, 3 ил. v w fe

Эти коды преобразуются цифроанало- говыми преобразователями 31 -34 в аналоговые сигналы, поступающие на электроды опорных напряжений цифроаналоговых преобразователей 27-30. Целая часть а по- ступает на вход данных установки начального значения счетчика 8 импульсов.

Генератор 16 импульсов вырабатывает тактирующие прямоугольные импульсы ГИ 16 высокой частоты (100-1000 кГц) (фиг. 4 а). Эти импульсы поступают на вход двоичного счетчика 15, два младших разряда его выхода определяют двухразрядное число Сг2(15), (фиг. 4 б). Этот сигнал приходит на вход данных дешифратора 19 Инвертированные импульсы с выхода инвертора 16 поступают на вход синхронизации дешифратора 19, с первых четырех выходов кото

pi(a)(VK(a -1) + Ук(а + 2)), (5)(VK{a) + VK(a +1)), (5)(Ук(а + 1)-VK(tf )), p4(5)(VK(a +2)-Vx(a -1)

Эти сигналы приходят на сумматоры 25, на выходах которых получаются сигналы, аппроксимирующие функции VK(«) К 1,„.,т. Они домножаются перемножителями 26 на сигнал, пропорциональный требуемому электромагнитному моменту М. На их выходах формируются оптимальные значения ik° токов фаз якорной обмотки 2, поступающие на входы усилителей 6 мощности. Они питают фазы обмотки 2 токами ik к° с помощью датчиков 5 тока.

IK ik° M -VK(a). . (5)

Синхронная машина 1 развивает электромагнитный момент Мэ М при минимальных потерях в якорной обмотке.

Разделитель 7 сигнала работает следующим образом.

При поступлении синхронизирующего импульса младший разряд целой части а МРЦ4 записывается в D-триггер 46, а бит, хранившийся в D-триггере 47, записывается в D-триггер 48, По обратному фронту синхронизирующего импульса бит из D-триггера 46 записывается в D-триггер 47, Логические схемы И 40, ИЛИ-НЕ 42, и ИЛИ 44 образуют схему ЭКВИВАЛЕНТНОСТЬ, на выходе которой получается единица при одинаковых входных сигналах и ноль при разных входных сигналах. Текущее значение МРЦ4 сравнивается со значением МРЦ4, зафиксированным на такт ранее. Результат сравнения поступает на вторую схему ЭКВИВАЛЕНТНОСТЬ, состоящую из логических схем И 41, ИЛИ-НЕ 43 и ИЛИ 45, где сравнивается со старшим разрядом дробной части СРД4 цифрового кода а . Выход схемы ИЛИ 45 является разрядом знака РЗ дробной части а, а ее старший разряд СР получается инвертированием старшего разряда дробной части а СРД4.

С помощью кубических сплайн-функ- ций, зависящих от приведенных дробных частей а, определяют аппроксимацию функции (5) следующие выражения:

(a-1),Vi (5),Vi (a + 1),Vi(),a)

im°iM -F(Vm(a-1), Vm(«), Vm(a +1), Vm( а+2),а ),

где F( ) определяется равенством: F(V-i, V0. Vi, V2, a) (0.25 a2- - 0.0625KV-1 + V2) + (0,5625 - 0,25 a2 )(VoH

+ Vi) + (1,375 a - 1,5 & XVi - Vo) +

+ (0,53-0,125 aXV2-V-i). Выражения (1), (5) получаются в результате решения методом множителя Лагранжа задачи на условный экстремум: найти токи ii,,,.,m, создающие требуемый электромагнитный момент М при минимальных потерях в обмотке якоря:

И2 + ... + .mln, (a)-f-... + im fm(a);

М.

(6)

Функция Лагранжа и условия ее стационарности имеют вид:

V i2 + ... + U2+ (a) +

+ ... + Im (т(а)-М

2ii+ (a)-0,j

2im+ A0fo(a)-0 J Из равенств (6) - (8) получаем

h°

M ffi (a)

f

(d) + . .. +(a)

im

(d)

W 2(a) +... + f&(d)

Формирование дробной части угла поворота ротора, приведенной к середине интервала дискретности по целой части, и использование соответствующих сплайн- функций, записанных в ПЗУ второй группы, позволяет выделить основную, медленно меняющуюся в пределах интервала дискретности составляющую оптимального значения фазного тока, благодаря чему уменьшаются динамические погрешности, связанные с неидентичностью временных задержек перемножителей.

Введение задержки на один период работы импульсной части электродвигателя при передаче целой части угла а поворота ротора на выделение дробной части а, а также применение перемножающих ЦАП с входными регистрами позволяют накапливать в группах по четыре регистра данные, соответствующие новой целой части а и, переписывать их одновременно во входные регистры ЦАП, подавая соответствующее значение дробной части а на адресные входы ПЗУ 10-13, При этом исключаются динамические погрешности, связанные с поочередным обновлением данных в регистрах.

Таким образом, благодаря введению m сумматоров, выполнению разделителя сигнала на целую и дробную части из инвертора, двух схем эквивалентности и трех D-триггеров получен моментный вентильный электродвигатель с высокой стабильностью момента по углу поворота ротора и с высокими динамическими характеристиками.

Формула изобретения Моментный вентильный электродвигатель, содержащий синхронную машину с гп-фазной якорной обмоткой и ротором-индуктором, на валу которого установлен датчик положения ротора, m усилителей, m датчиков тока, каждый из которых включен между выходом одного из усилителей и соответствующей фазой якорной обмотки, выход каждого датчика тока подключен к информационному входу одного из усилителей, разделитель сигнала на целую часть и дробную часть, вход данных которого соединен с выходом датчика положения ротора, синхронизирующий вход объединен с синхронизирующим входом первого счетчика импульсов и подключен к выходу первой логической схемы И, а выход целой части соединен - с входом данных установки начального значения первого счетчика импульсов, суммирующий вход которого подключен к выходу второй логической схемы И, первые входы логических схем И подключены соответственно к инверсному и прямому выходам RS-триггера, вторые входы логических схем 1/1 объединены с входами инвертора и второго счетчика импульсов и подключены к выходу генератора импульсов, дешифратор с четырьмя выходами, вход данных и синхронизирующий вход которого подключены к выходам второго счетчика и инвертора, а первый и четвертый выходы - к S и R-входам RS-триггера, т-ка- нальный формирователь управляющих сигналов, каждый канал которого составлен из постоянного запоминающего устройства, четырех регистров, четырехвходового сумматора, основного перемножителя и четырех дополнительных перемножителей, выходы которых подключены к входам четырехвходового сумматора, выходом соединенного с первым входом основного перемножителя, выход которого подключен к управляющему входу соответствующего усилителя, адресные входы постоянных запоминающих устройств каналов подключены к выходу первого счетчика импульсов, в каждом канале объединенные входы данных регистров соединены с выходом постоянного запоминающего устройства данного канала, а синхронизирующие входы одноименных регистров каналов объединены и подключены соответственно к выходам дешифратора, вторые входы одноименных дополнительных перемножителей каналов объединены четыре дополнительных постоянных запоминающих устройств, объединенные входы которых соединены с выходом дробной части разделителя сигнала на целую и дробную части, отличающийся тем, что, с целью повышения стабильности момента по углу поворота и улучшения динамических характеристик, введены четыре цифроаналоговых преобразователя, каждый из которых включен между выходом одного из дополнительных постоянных запоминающих устройств и объединенными вторыми входами соответствующих одноименных дополнительных перемножителей каналов формирователя управляющего сигнала, каждый канал которого снабжен четырьмя дополнительными двухвходовыми сумматорами, а каждый дополнительный перемножитель этого канала - синхронизирующим входом, при этом каждый из дополнительных двухвходовых сумматоров в канале по первому входу и выходу включен между выходом соответствующего

регистра и первым входом одного из дополнительных перемножителей этого канала, вторые входы первого, второго, третьего и четвертого дополнительных двухвходовых сумматоров соединены с выходами четвертого, третьего, второго и первого регистров - соответственно, синхронизирующие входы дополнительных перемножителей каналов объединены и подключены к выходу первой логической схемы И, разделитель сигнала

на целую и дробную части составлен из инвертора, двух логических схем ЭКВИВАЛЕНТНОСТЬ, трех последовательно соединенных D-триггеров, информационный вход первого D-триггера и первый вход

первой схемы ЭКВИВАЛЕНТНОСТЬ объединены, образуя шину младшего разряда двоичного кода угла поворота ротора выхода целой части упомянутого разделителя сигнала, вход инвертора, являющийся шиной старшего разряда двоичного кода угла поворота ротора входа данных разделителя сигнала, объединен с первым входом второй схемы ЭКВИВАЛЕНТНОСТЬ, второй вход которой соединен с выходом первой схемы

ЭКВИВАЛЕНТНОСТЬ, вторым входом подключенной к выходу третьего D-триггера, прямой синхронизирующий вход которого объединен с прямыми синхронизирующими входами первого и второго D-триггеров, образуя синхронизирующий вход разделителя сигнала на целую и дробную части, шина выхода дробной части которого образована линиями разрядов дробной части входа данных и выходами инвертора и вторрй схемы

ЭКВИВАЛЕНТНОСТЬ, а каждый из дополнительных постоянных запоминающих устройств выполнен с возможностью записи функций вида

р1 0,25 а2- 0,0625;

pi 0,5625 -0,25 а 2; ,375а-1,5а3: ,5 и3--0.125 а;

где а - приведенная дробная часть угла а поворота;

а

«.Ј- (а.0,5);

а- целая часть угла а; а ent (а - усл. ед. измерения,

ГИЦ6)

| Моментный вентильный электродвигатель | 1987 |

|

SU1554084A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Моментный вентильный электродвигатель | 1988 |

|

SU1681366A1 |

| кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-07-30—Публикация

1988-05-06—Подача