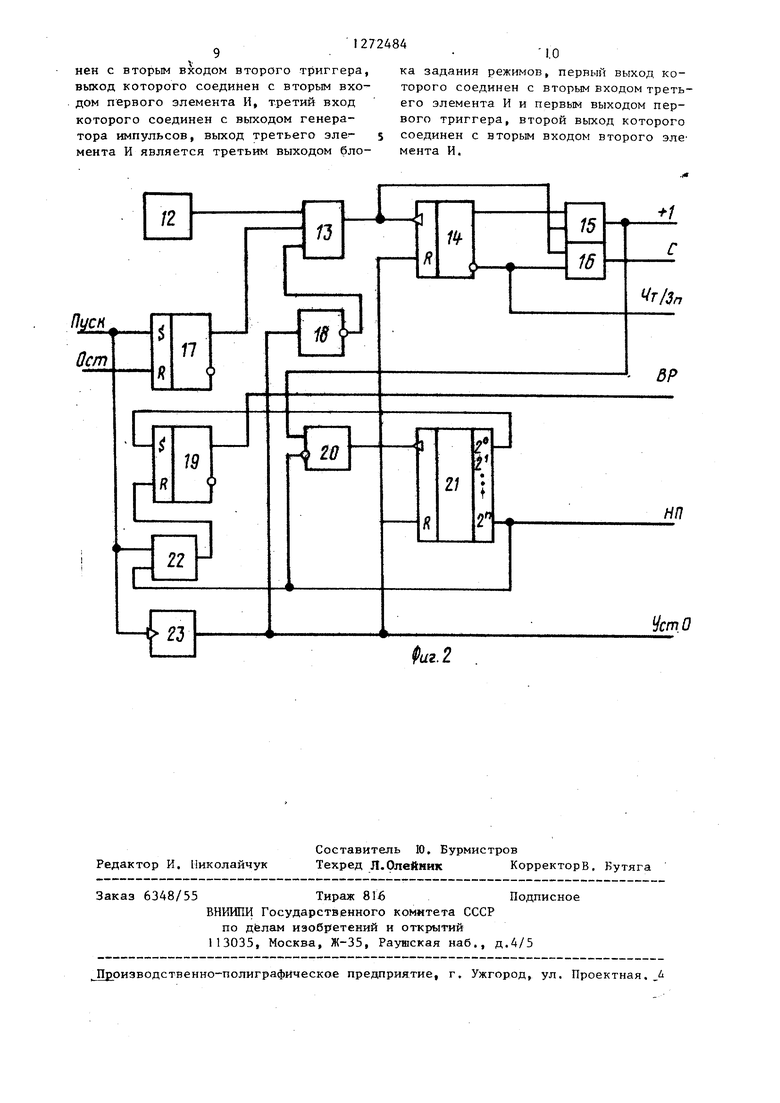

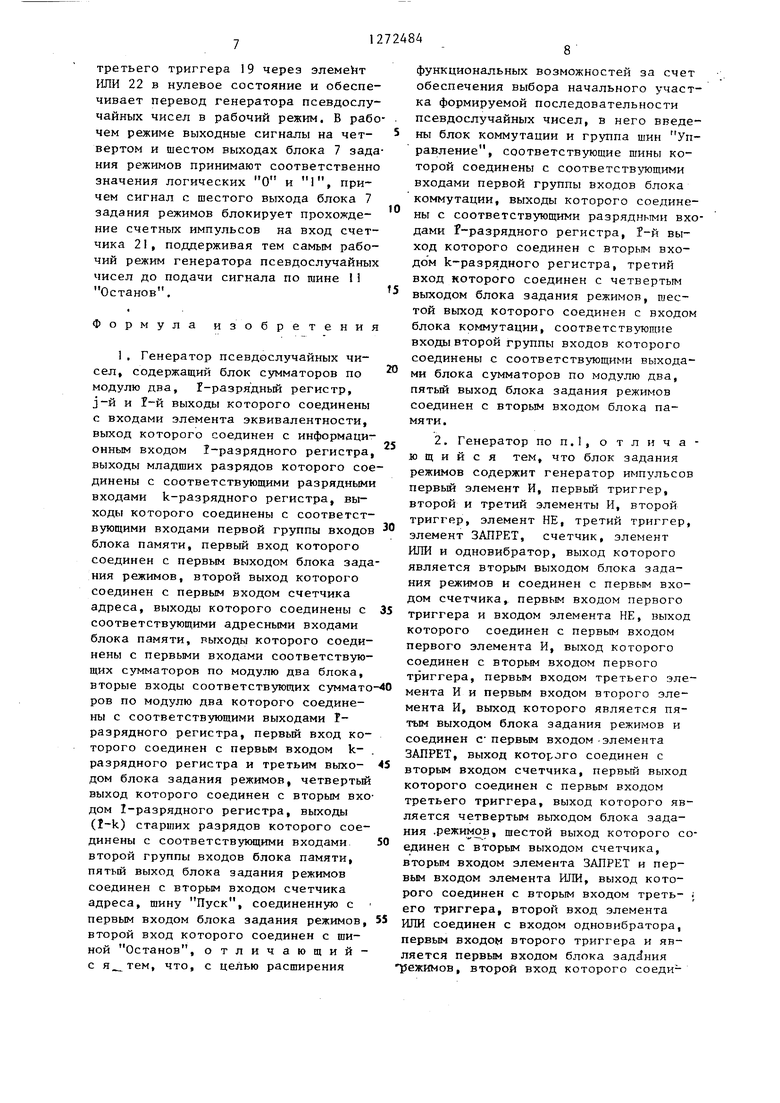

Изобретение относится к импульсной технике. Целью изобретения является расширение функциональных возможностей генератора за счет обеспечения выбора начального участка формируемой последовательности псевдослучайных чисел.. I На фиг.1 представлена структурная схема генератора псевдослучайных чисел; на фиг,2 - схема примера реализации блока задания режимов. Генератор псевдослучайных чисел (фиг.1) содержит блок 1 сумматора по модулю два, блок 2 коммутации, 1разрядный регистр 3, 3-й и 1-й выходы которого соединены с входами злемента 4 эквивалентности, k-разрядный регистр 5, выходы которого соединены с соответствующими входами первой группы входов блока 6 памяти, первый вход которого соединен с первым выхо дом блока 7 задания режимов, второй выход которого соединен с первым вхо дом счетчика 8 адреса, группу 9 шин /Управление, шину 10 Пуск, шину I Останов. Выход элемента 4 эквивалентности соединен с информационным входом {-разрядного регистра 3, выхо ;ды к младших разрядов которого соеди нены с соответствующими разрядными входами k-разрядного регистра 5. Выходы счетчика 8 адреса соединены с соответствующими адресными входами блока 6 памяти, выходы которого соединены с первыми входами соответству ющих сумматоров по модулю два блока 1, вторые входы соответствующих сумматоров по модулю два которого соеди нены с соответствующими выходами tразрядного регистра 3, первый вход которого соединен с первым входом kразрядного регистра 5 и третьим выхо дом блока 7 задания режимов, четвер тый выход которого соединен с вторым входом Р-разрядного регистра 3, вы ходы (-k) старших разрядов которого соединены с соответствующими входами второй группы входов блока 6 памяти. Пятый выход блока 7 задания режимов соединен с вторым входом счетчика 8 адреса. Шина 10 Пуск соединена с первым входом блока 7 задания режимов, второй вход которого соединен с шиной 11 Останов. Соответствующие шины группы 9 шин Управление соединены с соответствующими входами первой группы вход-.тв блока 2 коммутации, выходы кото,рого соединены с соответствующими разрядными входами -разрядного регистра 3, Е-й выход оторого соединен с вторым входом kразрядного регистра 5, третий вход которого соединен с четвертым выхоом блока 7 задания режимов, шестой выход которого соединен с входом блока 2 коммутации, соответствующие входы второй группы входов которого соединены с соответствующими выходами блока 1 сумматоров по модулю два. Пятый выход блока 7 задания режимов соединен с вторым входом блока 6 памяти. Блок 7 задания режимов (фиг.2) содержит генератор 12 импульсов, .первый элемент И 13, первый триггер 14, второй 1.5 и третий 16 элементы И, второй триггер 17, элемент НЕ 18, третий триггер 19, элемент ЗАПРЕТ 20, счетчик 21, элемент ИЛИ 22, одновибратор 23, выход которого является вторым выходом блока 7 задания режимов и соединен с первым входом счетчика |21, первым входом первого триггера 14 и входом элемента НЕ 18, выход которого соединен с первым входом первого элемента И 13, выход которого соединен с вторым входом первого триггера 14, первым входом третьего элемента И 16 и первым входом второго элемента И 15, выход которого является пятым выходом блока 7 задания режимов и соединен с первым входом элемента ЗАПРЕТ 20, выход которого соединен с вторым входом счетчика 21, первый выход которого соединен с первым входом третьего триггера 19, выход которого является четвертым выходом блока 7 задания режимов, шестой выход которого соединен с вторым выходом счетчика 21, вторым входом элемента ЗАПРЕТ 20 и первым входом элемента ИЛИ 22, выход которого соединен с вторым входом третьего триггера 19. Второй вход элемента ИЛИ 22 соединен с входом одновибратора 23, первым входом второго триггера 17 и является первым входом блока 7 задания режимов, второй вход которого соединен с вторым входом второго триггера 17, выход которого соединен с вторым входом первого элемента И 13, третий вход которого соединен с выходом генератора I2 импульсов . Выход третьего элемента И 13 является третьим выходом блока 7 задания режимов, первый выход которого соединен с вторым входом третьего элемента И 16 и первым выходом первого триггера 14, второй выход которого соединен с вторым входом второго элемента И 15, Генератор псевдослучайных чисел работает следующим образом. В начальном режиме записи исходного числа, соответствующего начальному участку формируемой последовател ности псевдослучайных чисел,и формиро вания псевдослучайных чисел блок 7 зад ния режимов формирует на своем втором выходе сигнал установки нуля,который устанавливает в исходное состояние сче чик 8 адреса. На шестом выходе блока 7 задания режимов в это время присут ствует уровень логического О, кото рый обеспечивает передачу на выход блока 2 коммутации сигналов с шин Управление группы 9 шин. Начиная с первого такта работы блок 7 задания режимов вырабатывает последовательности из трех, импульсов по своим пер вому, третьему и пятому выходам, которые поступают соответственно на первый вход (Чтение/Запись) блока 6 памяти, первые входы (синхронизации) f-разрядного 3 и k-разрядного 5 регистров, на второй (счетный) вход счетчика 8 адреса и второй вход (Запрет обращения) блока 6 памяти. Управление режимом работы 1-разр дного 3 и k-разрядного 5 регистров осуществляется по их второму и треть ему входам соответственно, на которые подается сигнал с четвертого выхода (Выбор режима) блока 7 задани режимов, причем при значении этого сигнала, равном логическому О, 1разрядный 3 и k-разрядный 5 регистры работают в режиме эаписи информации параллельным кодом со .своих разрядных входов, а при значении сигнала, равном логической 1 - в режиме сдвига записанной информации в сторо ну старших разрядов. I В первом такте работы генератора псевдослучайных чисел в начальном режиме значение сигнала Выбор режима равно логическому О, поэтому при поступлении импульса синхронизации с третьего выхода блока 7 задания режимов на первые входы Г-разрядного 3 и k-разрядного 5 регистров в них заносится информация с шин группы 9 щин Управление и с младших разрядов -разрядного регистра 3 соответственно. При изменении сигнала на входе Чтение/Запись блока 6 памяти из состояния логической 1 в состояние логического О (режим записи) содержимое (E-k) старших разрядов -разрядного регистра 3 и всех разрядов k-разрядного регистра 5 записывается в первую ячейку (начало массива) блока 6 памяти. После этого сигналом с шестого выхода блока 7 заДания режимов содержимое счетчика 8 адреса увеличивается на единицу и первый такт работы генератора псевдослучайных чисел заканчивается. При этом Значение сигнала управления режимами работЬ Г-разрядного 3 и k-раз- рядного 5 регистров на четвертом выходе блока 7 задания режимов становится равным логической I, при котором J-раэрядный 3 и k-разрядный 5 регистры образуют (I+k)-разрядный регистр сдвига с элементом 4 эквивалентности в цепи обратной связи. При поступлении на этот регистр в каждом последующем такте импульса синхронизации с третьего выхода блока 7 задания режимов происходит сдвиг информации на один разряд и занесение в первьй- разряд этого регистра (в -1разрядный регистр 3) псевдослучайного двоичного символа с выхода элемента 4 эквивалентности. В каждом такте работы генератора псевдослучайных чисел сдвинутая на один разряд псевдослучайная информация из 1-разрядного 3 и k-разрядного 5 регистров по логическому уровню сигнала Чтение/Запись записывается в следующую, определяемую содержимым счетчика 8 адреса, ячейку блока 6 памяти, после чего содержимое счетчика 8 адреса увеличивается на единицу. Процесс записи исходного массива в блок 6 памяти продолжается до изменения сигнала на четвертом выходе блока 7 задания режимов с уровнем логической I на уровень логического О, что определяет момент перехода генератора псевдослучайных чисел в рабочий режим. Минимально необходимое количество тактов работы генератора псевдослуайных чисел в начальном режиме опеделяется величиной q + k, где qисло ячеек блока 6 памяти. Дополнительные k тактов работы необходимы ля записи в первые k ячеек блока 6 амяти фиксированных (определенных) псевдослучайных чисел вместо, случайных, переписанных из k-раэрядного регистра 5 в первые k тактов. После завершения работы генератора псевдослучайных чисел в начальном режиме 6hoK 6 памяти оказьшается занесенным псевдослучайными числами, ,представлявшими. собой 1-разрядные отрезки псевдослучайной последовательирсти максимальной длины (при соответствии номеров j и I разрядов 1-разрядного регистра 3 показателям степени примитивного характеристического номинала) .При этом записанная в блок 6 памяти информация полностью определяется входным словом, поданным на шины группы 9 шин Управление, Рабочий режим генератора псевдослучайных чисел определяется нулевым логическим уровнем на четвертом и единичным логическим уровнем на шестом выходах блока 7 задания режимов, который в рабочем режиме вырабатывает последовательности из трех управляющих сигналов на первом, третьем и пятом своих выходах. По сигналу логической 1 на первом выходе (Чтение/ Запись) блока 7 задания режимов происходит выборка содержимого i-й ячейжи блока 6 памяти, которое поступает на соответствующие входы блока 1 сумматоров по модулю два, На другие вхо ды блока 1 сумматоров по модулю два поступает число, хранящееся в 1-разрядном регистре 3, В результате на выходах блока 1 сумматоров по модулю два образуется поразрядная сумма по модулю два входных чисел, которая по сигналу синхронизации с третьего выхода блока 7 задания режимов записывается в 1-разрядный регистр 3 и по. является на выходах генератора псев дослучайных чисел. По этому же сигна лу синхронизации первые k разрядов прежнего числа переписываются из разрядного регистра 3 в k-разрядный регистр 5, Во второй половине каждого такта информации (по сигналу на входе Чтение/Запись блока 6 памяти) , присутствующая на входных шинах блока 6 памяти, записывается в ту же i-ю ячейку. Такт работы генератора заканчивается увеличением содержимог счетчика 8 адреса на единицу по сигналу с пятого выхода блока 7 задания

режимов, который используется также для запрета обращения к блоку 6 памяти на время изменения содержимого

увеличивается на единицу.

Переключение старщего разряда счетчика 21 в единицу вызьгоает сброс четчика 8 адреса. По достижении с 5держимым счетчика 8 адреса числа q-1 происходит его обнуление. Далее работа генератора псевдослучайных чисел происходит аналогично. Блок 7 задания режимов работает следующим образом. По сигналу на шине 10 Пуск генератора псевдослучайных чисел устанавливаются в единичное и нулевое состояние соответственно второй 17 и третий 19 триггеры, запускается одновибратор 23, формирующий выходной сигнал установки нуля на втором выходе блока 7 задания режимов. Этот сигнал устанавливает в исходное состояние первый триггер 14 и счетчик 21, состояние старшего разряда которого является выходным сигналом на шестом выходе блока 7 задания режимов. По окончании сигнала установки нуля на вход первого триггера 14 поступают через первый элемент И 13 импульсы с генератора 12 импульсов. Сигнал с первого выхода триггера 14 является сигналом Чтение/Запись с первого выхода блока 7 задания режимов. В первом такте работы блока 7 задания режимов сигнал на его четвертом выходе равен нулю, а на третьем и пятом выходах (выходы третьего 16 и второго 15 элементов И соответственно) последовательно формируются сигналы синхронизации увеличения содержимого счетчика 8 адреса (запрет обращения к блоку 6 памяти), В конце первого такта.по сигналу с второго элемента И 15, воздействующего через элемент ЗАПРЕТ 20 на второй (счетчньй) вход счетчика 21, последний устанавливается в состояние,. при котором сигнал с его первого выхода устанавливает в единичное состояние третий триггер 19, т.е. формирует единичный сигнал на четвертом выходе блока 7 задания режимов. t . . Во втором и последующих тактах работы состояние сигналов на .четвертом и шестом выходах логические 1 и О соответственно блока 7 задания режимов не изменяется, а на его первом, третьем и пятом вьтходах формируются последовательности управляющих и 1пульсов. При этом по окончании каждого такта содержимое счетчика 21 третьего триггера 19 через элемент ИЛИ 22 в нулевое состояние и обеспе чивает перевод генератора псевдослу чайных чисел в рабочий режим. В раб чем режиме выходные сигналы на четвертом и шестом выходах блока 7 зад ния режимов принимают соответственн значения логических О и 1, причем сигнал с шестого выхода блока 7 задания режимов блокирует прохождение счетных импульсов на вход счет чика 21, поддерживая тем самым рабо чий режим генератора псевдослучайны чисел до подачи сигнала по шине Ii Останов, Формула изобретени 1, Генератор псевдослучайных чи„сел, содержащий блок сумматоров по модулю два, Г-разрядный регистр, j-й и Г-й выходы которого соединены с входами элемента эквивалентности, выход которого соединен с информационным входом 1-разрядного регистра выходы младших разрядов которого сое динены с соответствующими разрядными входами k-разрядного регистра, выходы которого соединены с соответствующими входами первой группы входов блока памяти, первый вход которого соединен с первым выходом блока зада ния режимов, второй выход которого соединен с первым входом счетчика адреса, выходы которого соединены с соответствующими адресными входами блока памяти, выходы которого соединены с первыми входами соответствующих сумматоров по модулю два блока, вторые входы соответствующих суммато ров по модулю два которого соединены с соответствующими выходами Гразрядного регистра, первый вход которого соединен с первым входом kразрядного регистра и третьим выходом блока задания режимов, четвертый выход которого соединен с вторым вхо дом 1-разрядного регистра, выходы (I-k) старших разрядов которого соединены с соответствующими входами второй группы входов блока памяти, пятый выход блока задания режимов соединен с вторым входом счетчика адреса, щину Пуск, соединенную с первым входом блока задания режимов, второй вход которого соединен с шиной Останов, отличающийс , что, с целью расширения функциональных возможностей за счет обеспечения выбора начального участка формируемой последовательности псевдослучайных чисел, в него введены блок коммутации и группа шин Управление, соответствующие шины которой соединены с соответствующими входами первой группы входов блока коммутации, выходы которого соединены с соответствующими разрядными входами Г-разрядного регистра, Г-й выход которого соединен с вторым входом k-разрядного регистра, третий вход которого соединен с четвертым выходом блока задания режимов, шестой выход которого соединен с входом блока коммутации, соответствующие входы второй группы входов которого соединены с соответствующими выходами блока сумматоров по модулю два, пятый выход блока задания режимов соединен с вторым входом блока памяти. 2. Генератор поп.1,отличаю щ и и с я тем, что блок задания режимов содержит генератор импульсов первый элемент И, первый триггер, второй и третий элементы И, второй триггер, элемент НЕ, третий триггер, элемент ЗАПРЕТ, счетчик, элемент ИЛИ и одновибратор, выход которого является вторым выходом блока задания режимов и соединен с первым входом счетчика, первым входом первого триггера и входом элемента НЕ, выход которого соединен с первым входом первого элемента И, выход которого соединен с вторым входом первого триггера, первым входом третьего элемента И и первым входом второго элемента И, выход которого является пятым выходом блока задания режимов и соединен с- первым входом -элемента ЗАПРЕТ, выход которого соединен с вторым входом счетчика, первый выход которого соединен с первым входом третьего триггера, выход которого является четвертым выходом блока задания .режимо в, шестой выход которого соединен с вторым выходом счетчика, вторым входом элемента ЗАПРЕТ и первым входом элемента ИЛИ, выход которого соединен с вторым входом треть- ; его триггера, второй вход элемента ИЛИ соединен с входом одновибратора, первьм входом второго триггера и явяется первым входом блока задания ежимов, второй вход которого соединен с вторым входом второго триггера, выход которого соединен с вторым входом первого элемента И, третий вход которого соединен с выходом генератора импульсов, выход третьего элемента И является третьим выходом блока задания режимов, первый выход которого соединен с вторым входом третьего элемента И и первым выходом первого триггера, второй выход которого соединен с вторым входом второго элемента И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Генератор псевдослучайных чисел | 1980 |

|

SU935951A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Генератор псевдослучайных чисел | 1990 |

|

SU1805465A1 |

| Генератор псевдослучайных чисел | 1976 |

|

SU693408A1 |

Изобретение относится к импульсной технике. Цель изобретения - расширение функциональных возможностей достигается за счет обеспечения выбора начального участка формируемой последовательности псевдослучайных чисел. Для этого в генератор псевдослучайных чисел дополнительно введены блок 2 коммутации и группа 9 шин Управление. Кроме того, генератор содержит блок 1 сумматоров по модулю два, f-разрядный регистр 3, элемент 4 эквивалентности, К-разрядньм регистр 5, блок 6 памяти, блок 7 задания режимов, счетчик 8 адреса, шины: 10 Пуск, 11 Останов. Возможность установки начального состояния генератора обеспечивает генерацию двух различных начальных участков SS последовательности и, как следствие (Л этого, возможность отбора генерируемых последовательностей по степени приближения выборочных статистических характеристик к гипотетическим. 1 з.п.ф-лы, 2 ил. ГчЭ го СХ) l4

| Генератор псевдослучайных чисел | 1976 |

|

SU693408A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-23—Публикация

1985-05-23—Подача