Изобретение относится к электросвязи.

Известно устройство, включающее в себя последовательно соединенные входной блок, коммутатор, первый цифроаналоговый преобразователь, аналого-цифровой преобразователь, первый блок памяти, вычитатель, вторым входом соединенный с выходом аналого-цифрового преобразователя, сумматор, второй блок памяти, выходом соединенный с вторым входом сумматора, а также второй цифроаналоговый преобразователь, формирователь адреса и генератор.

Задачей изобретения является повышение помехоустойчивости принимаемых сообщений.

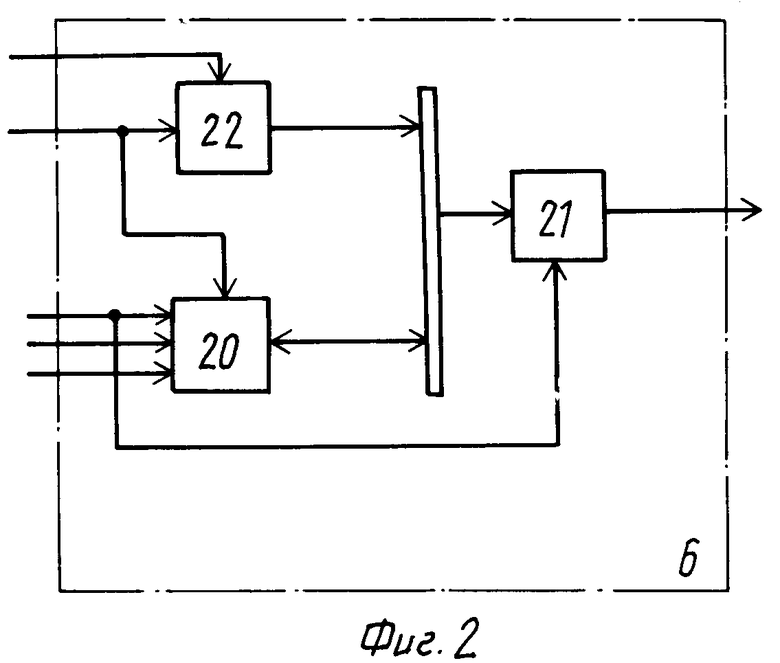

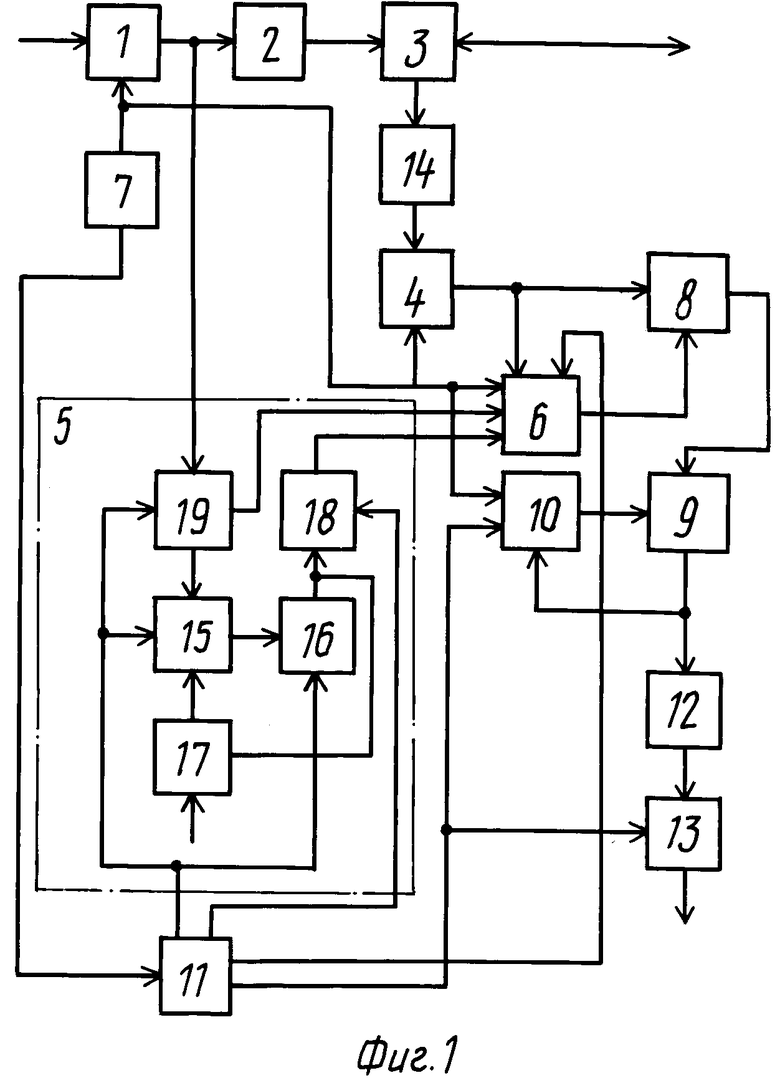

На фиг. 1 изображена структурная электрическая схема, на фиг. 2 схема первого блока памяти.

Устройство содержит входной блок 1, блок 2 преобразования уровня, дифференциальную систему 3, аналого-цифровой преобразователь 4 (ЦАП), блок 5 адресации, первый блок 6 памяти, генератор 7, блок 8 вычитания, сумматор 9, второй блок 10 памяти, блок 11 управления, пороговый блок 12, триггер 13, корректор 14.

Блок адресации содержит оперативное запоминающее устройство 15, параллельный регистр 16, сумматор 17, счетчик 18 с предварительной записью, последовательный регистр 19.

Первый блок памяти содержит оперативное запоминающее устройство 20, параллельный регистр 21, ключ 22.

Устройство работает следующим образом.

Можно выделить четыре одновременно протекающих процесса, которые в свою очередь, связаны между собой.

Первый процесс это формирование передаваемого сигнала. Данная операция осуществляется каскадно соединенными входным 1 блоком, блоком 2 преобразования уровня и дифференциальной системой 3, пропускающими сигналы собственной передачи в направлении пропускания.

Второй процесс это формирование адреса для нормальной работы устройства. Данная операция осуществляется с помощью блока 5 адресации, где составными частями входят последовательный регистр 14, оперативное запоминающее устройство 15, параллельный регистр 16, сумматор 17 и счетчик с предварительной записью 18.

Третий процесс это компенсация сигналов собственного передатчика в тракте приема. Он осуществляется с помощью дифсистемы 3, пропускающей сигналы с линии связи и ослабляющей сигналы своего передатчика, корректора 14, аналого-цифрового преобразователя 4, блока памяти 6 и блока 8.

Наконец, четвертый процесс заключается в восстановлении формы принимаемого сигнала. Он осуществляется с помощью сумматора 9, второго блока памяти 10, порогового блока 12 и триггера 13.

Всеми перечисленными выше процессами управляет блок 11 управления совместно с генератором 7.

Теперь рассмотрим более подробно перечисленные выше процессы.

Итак, первый процесс, как было сказано ранее, необходим для формирования и одновременной привязки к тактовой частоте обработки сигнала, подлежащего передаче. Входной сигнал поступает на вход входного 1 блока, представляющего по существу обычный Д триггеp. На тактовый вход входного блока 1 поступает тактовая синхрочастота с выхода генератора 7. Сигнал на выходе входного блока 1 повторяет входной сигнал, однако появление его строго синхронизировано с тактовой частотой. Далее передаваемый сигнал поступает в блок 2 преобразования уровня. Для двухуровневого сигнала блок 2 преобразования уровня представляет компаратор, на второй вход которого подано пороговое значение. При формировании на выходе входного блока 1 логической единицы на выходе блока 2 преобразования уровня будет напряжение +U. Если на выходе входного блока 1 сформирован логический нуль, то выходной сигнал блока 2 преобразования уровня будет равен -U. Далее передаваемый сигнал поступает на вход линии связи через дифсистему 3 и одновременно из-за неидеальности параметров дифсистемы 3 в тракт приема. На этом первый процесс заканчивается.

Второй и третий процессы протекают взаимосвязанно. Рассмотрим их более подробно. Итак, на выходе дифсистемы 3 наблюдает сумму двух сигналов: принимаемого от станции Б и собственного, протекающего в тракт приема. Суммарный сигнал поступает на вход корректора 14, корректирующего амплитудно-частотные и фазо-частотные искажения линии связи (в дальнейшем АЧИ и ФЧИ). Корректор 14 устраняет АЧИ и ФЧИ у принимаемого сигнала. Для собственного передаваемого сигнала корректор 14 искажает форму паразитного сигнала, однако из-за линейного характера работы корректора 14 это не отразится на дальнейшей работе компенсации передаваемого сигнала. Для компенсации сигналов собственного передатчика в тракте приема использован закон относительности. Согласно этому закону, если знать порядок следования передаваемых символов, то помеху от сигналов собственного передатчика в тракте приема можно скомпенсировать, вычитая ее на соседних тактовых интервалах. Пусть на выходе входного блока 1 производится передача сигналов в виде S (K1Δt), S2 (K2 Δt). Sn (Kn Δt). Здесь и далее К Δt означает дискретный момент времени. От передаваемых сигналов на выходе АЦПЧ наблюдаем помеху равную

П1 (К1Δt) S1 (K1Δt) * gдс (K Δt) * *Lкор (К Δt) (1)

П2 (К2 Δt)= S2 (K2 Δt) * gдс (K Δt) * Lкор (K Δt)

Пn (Kn Δt) Sn (KnΔt) * gдс (КΔt) * Lкор (K Δt) Здесь gдс (К Δt) импульсная реакция дифсистемы 3 в тракте непропускания сигналов,

Lкор (КΔt) импульсная реакция корректора 14.

Из-за линейного характера импульсной реакции дифсистемы 3 и корректора 14 можно сказать, что передаваемому сигналу S1 (K1Δt) соответствует помеха П1 (K1Δt). Аналогично сигналу S2 (K2Δt) соответствует помеха П2 (K2Δt) и т. д. Следует сказать, что параметры дифсистемы 3 и корректора 14 могут изменяться во времени из-за изменения параметров линии связи. Это приведет к тому, что величина отсчетов помех Пi (KΔt) изменится. Однако, согласно закону относительности величина этих изменений на соседних тактовых интервалах будет мала. В самом деле, пусть мы передает сигнал S1 в моменты времени К1 Δt и К10 Δ t. В первом случае на выходе АЦПЧ будет помеха, равная П1 (К1 Δt), а во втором случае П1 (К10Δ t) П1 (K1 Δt) + σ1. Величина σ1 как раз обусловлена нестабильностью линии связи. Аналогично, если в очередной К20Δt вновь передается сигнал S1, то на выходе АЦП 4 будет помеха, равная П1 (К20 Δt) П1 (K10 Δt) + σ 2 и т.д.

Тогда согласно закону относительности компенсация сигналов собственного передатчика в тракте приема будет заключаться в вычитании сигналов на соседних тактовых интервалах. Для этих целей служит блок памяти 6 и блок 8. Итак, пусть на выходе АЦП 4 на i-том тактовом интервале при передаче (к примеру) наблюдаем сигнал, равный

Li (Ki Δt) П1 (Ki Δt) + yi (Ki Δt) (2) Здесь yi (Ki Δt) отсчет принимаемого сигнала.

Согласно ранее сказанному с помощью блока адресации 5 мы должны в блоке памяти 6 отыскать ту ячейку памяти, где ранее была записана помеха П1. Пусть такая ячейка найдена, где хранится сигнал, равный

Lm (Km Δt) П1 (Km Δt) + ym (Km Δt) (3) Тогда на выходе блока 8 будем иметь сигнал, равный

Mi (Ki Δt) Li (Ki Δt) Lm (Km Δt)yi (Ki Δt) tm (Km Δt) (4) Как видно из (4), здесь отсутствует величина помехи от собственного передатчика.

Покажем, как указывается нужная ячейка памяти для блока памяти 6 из блока адресации 5.

Для выполнения этой задачи выходной сигнал входного блока 1 поступает в блок адресации 5 на вход последовательного регистра 19. При этом последовательность нулей и единиц, которая передается в сторону станции Б одновременно задерживается в последовательном регистре 19. Таким образом, выходной сигнал последовательного регистра 19 представляет собой совокупность нулей и единиц, которые передаются в настоящий момент времени и на предыдущих тактах передачи. Операция задерживания передаваемого сигнала в последовательном регистре 19 по существу это формирование сигналов S1, S2. Sn для управления блоком 6 памяти, так как каждой последовательности нулей и единиц соответствует своя помеха от своего передатчика на входе приемника. Если обозначить через N число разрядов на выходе последовательного регистра 19, а через М число адресных разрядов блока памяти 6, то М > N. Оставшиеся К разрядов (К М-N) формируются с помощью оперативного запоминающего блока 15, параллельного регистра 16, сумматора 17 и счетчика с предварительной записью 18. Покажем, как это осуществляется.

Пусть передаваемый сигнал, хранимый в последовательном регистре 19 имеет вид 10001011 (N 8) в момент времени t1. В следующий момент времени t2 в последовательном регистре 19 вся информация сдвигается на один шаг вправо, при этом младший разряд теряется. Если передавался, к примеру, логический нуль, то на выходе последовательного регистра 19 будет сигнал, равный 01000101. Для управления работой оперативного запоминающего блока 15 используются кодовые комбинации, сдвинутые на один разряд влево относительно комбинаций, поступающих на вход блока памяти 6. Итак, в момент t1 в сторону блока памяти 6 поступает сигнал 10001011, а на адресные входы ОЗУ 15 поступает кодовая комбинация 01000101. Такая последовательность действий подготавливает к работе ОЗУ 15 при появлении очередной кодовой комбинации. Разрядность ОЗУ 15, параллельного регистра 16, сумматора 17 одинакова и равна К разрядам.

Пусть в первый момент времени t1 ОЗУ 15 было обнулено. Тогда с появлением в момент t1 кодовые комбинации 01000101 из ОЗУ 15 с этим адресом считывается нуль и записывается по сигналу с выхода блока управления 11 в параллельный регистр 16. Далее сигнал с выхода параллельного регистра 16 складывается в сумматоре 17 с единицей и записывается в ОЗУ 15 по тому же адресу 01000101. С началом временного интервала t2 сигнал из параллельного регистра 16 записывается в счетчик 18, который под действием тактовых импульсов начинает изменять свое состояние с установленного ранее состояния. К примеру, в момент времени t2 в счетчик 18 записался 0. После этого состояние счетчика изменяется следующим образом: 0,1,2.15. Если же в счетчик 18 предварительно записали "1", то состояние счетчика 18 будет таким: 1,2,3.15,0.

В случае появления на каком-то очередном t1 тактовом интервале на адресном входе ОЗУ 15 кодовой комбинации 01000101, из ОЗУ 15 считается единица, запишется в параллельный регистр 16, а в ОЗУ 15 запишется число "2" и т.д. Таким образом, с помощью ОЗУ 15, параллельного регистра 16 и сумматора 17 на различные кодовые комбинации производится увеличение содержимого ОЗУ 15 на единицу. По достижении в ОЗУ 15 состояния IIIl, в ОЗУ 15 запишется "0" (IIII + 0001 0000, перенос отбрасывается). Такой порядок работы позволяет адаптироваться под параметры линии связи. Итак, в момент времени t1 на адресные входы блока памяти 6 поступают кодовые комбинации 010001010000, 010001010001, 010001011111 в момент времени t2 на адресные входы блока памяти 6 поступают кодовые комбинации в виде 010001010001, 010001010010, 010001010000.

Как видно из данного описания, N старших разрядов на временных интервалах ti -ti+1 неизменны, а оставшиеся "К" разрядов изменяются. Так как старшие разряды неизменны, то и помеха Пi на выходе АЦП 4 также будет примерно одинаковой. Из первого блока памяти 6 по первому сформированному из блока адресации 5 адресу вначале считывается содержимое соответствующей ячейки памяти.

В ячейку с очередным номером записываете новое значение помехи плюс принимаемый отсчет сигнала. И далее из оставшихся ячеек информация только считывается. Тогда на выходе блока памяти 6 появляются в первый момент времени П1 (K1Δt) + y1 (K1 Δt), во второй момент нуль (запись информации), в третий П1 (K3 Δt) + +y3 (K3 Δt). в шестнадцатый П1 (К16 Δt) + y16 (K16 + Δt). При таком обращении к блоку памяти 6 первые члены у перечисленной выше последовательности одинаковые, а вторые члены случайны. Таким образом, на выходе вычитателя 8 будет сигнал в виде

yi (Ki Δt) t1 (K1 Δt); yi (Ki Δt) y3 (K3Δ t);

yi (Ki Δt) y16 (K16 Δt) (5)

При считывании информации ключ 22 закрыт, сигнал с выходов ОЗУ 15 через общую шину поступает на входы параллельного регистра 21. Запись сигнала в параллельный регистр 21 производится по сигналу с выхода блока управления. В случае записи информации в ОЗУ 20 открывается ключ 22 и через общую шину сигнал записи проходит на входы/выходы ОЗУ 20. Режимы работы ключа 22. ОЗУ 20 и выходного регистра 21 строго синхронны и управляются сигналами с выхода блока управления и блока адресации. На этом второй и третий этапы заканчиваются.

Четвертый этап призван восстановить форму принимаемых сигналов. Так как устройство предназначено для разделения двухуровневых сигналов, в последовательно (5), если yi (Ki Δt) положительная величина [yi (Ki Δt) > 0] то и вся последовательность имеет либо положительную величину, либо нулевое значение, когда слагаемые одинаковые по величине и знаку. С помощью сумматора 9, второго блока памяти 10 производится суммирование всех составляющих с выхода вычитателя 8.

Выходной сигнал сумматора 9 описывается выражением

Q [yi(KiΔt)-yj(KjΔt)]

[yi(KiΔt)-yj(KjΔt)]

Таким образом, если отсчеты принимаемого сигнала yi не имеют постоянной составляющей, то знак величины Q однозначно характеризует знак принимаемого сигнала. Сложнее обстоит дело, если каждый отсчет принимаемого сигнала имеет постоянную составляющую. Тогда выходной сигнал сумматора 9 сравнивается с пороговым значением в пороговом блоке 12. Величина порога в пороговом устройстве выбирается из соотношения

Р 2к˙С Здесь С величина постоянной составляющей принимаемого сигнала

Р значение порога

к- количество разрядов счетчика 18

(к М N)

Тогда, если Q > P, то в триггер приема 13 записывается логическая единица. Если же Q < P, то в триггер приема 13 записывается нуль.

Таким образом, выходной сигнал триггера приема 13 однозначно характеризует знак принимаемого сигнала и выдается потребителю сообщений.

Устройство является адаптивным. Изменение параметров линии связи приводит к изменению образцов помехи, которые записываются в блоке памяти 6. Таким образом, через несколько тактов передачи из-за изменений образцов помех Пi от сигналов собственного передатчика компенсация их будет такой же.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1992 |

|

RU2038702C1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1989 |

|

SU1809739A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| УСТРОЙСТВО ДЛЯ ФОРМОВАНИЯ ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1992 |

|

RU2039414C1 |

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| УСТРОЙСТВО ДЛЯ ПОРОГОВОГО ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ | 1993 |

|

RU2081513C1 |

| Приемник многочастотных сигналов | 1990 |

|

SU1838894A3 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

Использование: электросвязь. Сущность изобретения: устройство содержит входной блок 1, блок преобразования уровня 2, дифференциальную систему 3, АЦП 4, блок адресации 5, блоки памяти 6, 10, генератор 7, блок вычисления 8, сумматор 9, блок управления 11, пороговый блок 12, триггер 13, корректор 14. 2 з.п. ф-лы, 2 ил.

| Устройство для разделения направлений передачи в дуплексных системах связи | 1983 |

|

SU1133675A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-07-09—Публикация

1993-01-15—Подача