второго элемента и подключен к третьему выходу первого счетчика адреса, выход - к ,входу первого элемента НЕ, а второй вход выходу второго элемента НЕ, выход первого элемента НЕ соединен с первым третьего элемента И, второй вход которого подключен к четвертому выходу счетчика импульсов, а выход - к управляющему входу второгс триггера,первые входы четвертого и пятого элементов И соединены соответственно с шестым и седьмым

выходами блока управления, выходы четвертого и пятого элементов И подключены к вторым входам элементов И первой и второй групп соответственно, вторые входы четвертого и пятого элементов И подключены к входу первого элемента НЕ и третьим входам мультиплексоров и являются управляющим входом устройства, второй выход третьего счетчика адреса соединен с третьим входом блока индикации и является третьим адресным входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для контроля блоков полупроводниковой памяти | 1979 |

|

SU875469A2 |

| Оперативное запоминающее устрой-CTBO C САМОКОНТРОлЕМ | 1979 |

|

SU809402A1 |

| Устройство для контроля полупроводниковой памяти | 1981 |

|

SU968856A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ .ПОЛУПРОВОДНИКОВОЙ ОПЕРАТИВНОЙ ПАМЯТИ, содержащее блок управления., счетчики адреса, триггеры, дешифратор, счетчик импульсов, группы элементов И, сумматоры по модулю два, блок, сравнения и блок индикации, причем одни из выходов первого счетчика адреса подключены соответственно к входу первого триггера, к одним из входов дешифратора и первым входам элементов И первой и второй групп, выходы которых соединены соответственноС одними из входов первого и второго сумматоров по модулю два, другие входы которых подключены к одним из выходов второго счетчика адреса, рЫход первого триггера подключен к первому входу блока управления и входу установки в единицу второго триггера, первый выход которого соединен с другим входом дешифратора, первый и второй выходы которого подключены соотвественно к второму входу блока управления и к входу счетчика адреса, другой выход которого соединен с входом счетчика импульсов, первый выход; которого подключен к третьему входу блока управления, выход .третьего триггера соединен с первым входом блока индикации и четвертым входом блока управления, первый выход которого подключен к входу первого счетчика адреса, входы сброса первого и второго счетчиков адреса, первого, второго и третьего триггеров и счетчика импульсов соединены с вторым выходом блока управления, третий выход которого подключен к управляющему входу блока сравнения , выходы которого соединены соответственно с вторым входом блока индикации и первым входом четвертого триггера, второй вход и выход которого подключены соответственно к четвертому выходу и пятому входу блока управления, пятый выход которого и вход блока сравнения являются соответственно контрольными выходом и входом устройства, первым и вторым адресными выходами которо(Л го являются выходы первого и второго сумматоров по модулю два соответственно, отличающеесятем, что, с целью повышения надежности устройства за счет одновременного контроля группы микросхем па- , мяти, в него введены мультиплексоры, третий счетчик адреса, элементы И, элементы НЕ и элемент ТШИ, СП причем первый вход первого импульса подключен к второму выходу импульсов , второй вход - к выходу элеменСП та ИЛИ, а выход - к входу третьего 00 счетчика адреса, вход сброса которого соединен с вторым выходом блоо: ка управления, а первый выход - с первым входом второго мультиплексора, второй вход и выход которого подключены соответственно к третьему выходу счетчика ИМПУЛЬСОВ и к входу третьего триггера,первый и второй входы первого элемента И соединены соответственно с вторым В1 1ходом второго триггера и с первым выходом блока управления, а выход подключен к первому входу элемента ИЛИ, второй вход которого соединен с вторлм выходом дешифратора, первый вход

1

Иэобретение относится к вычислительной технике и может быть ис польэовано в устройствах для контроля полупроводниковых ОЗУ.

Известны устройства для контрол полупроводниковой оперативной памяти ,

Одно из известных устройств содержит счетчик адреса, схемы сравнения и счетный триггер, а второе счетчик адреса, счетчик циклов, элементы импликации.и элемент И fl

Недостаток устройства заключается в низком быстродействии.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля полупроводниковой оперативной памяти, содержащее блок управления, три счетчика, три триггера, программируемый делитель частоты, дешифратор, два блока вентилей, два сумматора по модулю два, компаратор ошибок и блок индикации C2J.

Недостатками прототипа являются низкая надежность вследствие невозможности проверки ОЗУ на уровне системы ввиду отсутствия адресации к отдельным группам микросхем памяти, а также невозможность его использования в качестве сервисного оборудования для микро-ЭВМ.

Цель изобретения - повышение надежности устройства за счет одновременного контроля группы микросхем памяти, а также применение устройства для контроля микро-ЭВМ.

Поставленная цель достигается тем, что в устройство для контроля полупроводниковой оперативной памят содержащее блок управления, счетчики адреса, триггеры, дешифратор, .счетчик импульсов, группы злемен-тов И, сумматоры по модулю два, бло сравнения иблок индикации, причем одни из выходов первого счетчика

адреса подключены соответственно к входу первого триггера, к одним из входов дешифратора и первым входам элементов И первой и второй групп, выходы которых соединеньа соответственно с одними иэ входов первого и второго сумматоров по модулю два, другие входы которых подключены к одним из выходов второ0 го счетчика адреса, выход первого триггера подключен к первому входу блока управления и входу установки в единицу второго триггера, первый выход которого соединен с другим

5 входом дешифратора, первый и второй выходы которого подключены соответственно к второму входу блока управления и входу счетчика адреса, другой выход которого соединен с входом счетчика импульсов, первый вы ход которого подключен к третьему входу блока управления, вы-ход третьего триггера соединен с первым входом блока индикации и четвертым входом блока управления, первый

5 выход которого подключен к входу первого счетчика адреса, входы сброса первого и второго счетчиков адреса, первого, второго и третьего триггеров и счетчика импульсов сое0 динены с вторым выходом блока управления, третий выход которого подключен к управляющему входу блока сравнения, выходы которого соединены соответственно, с вторым входом

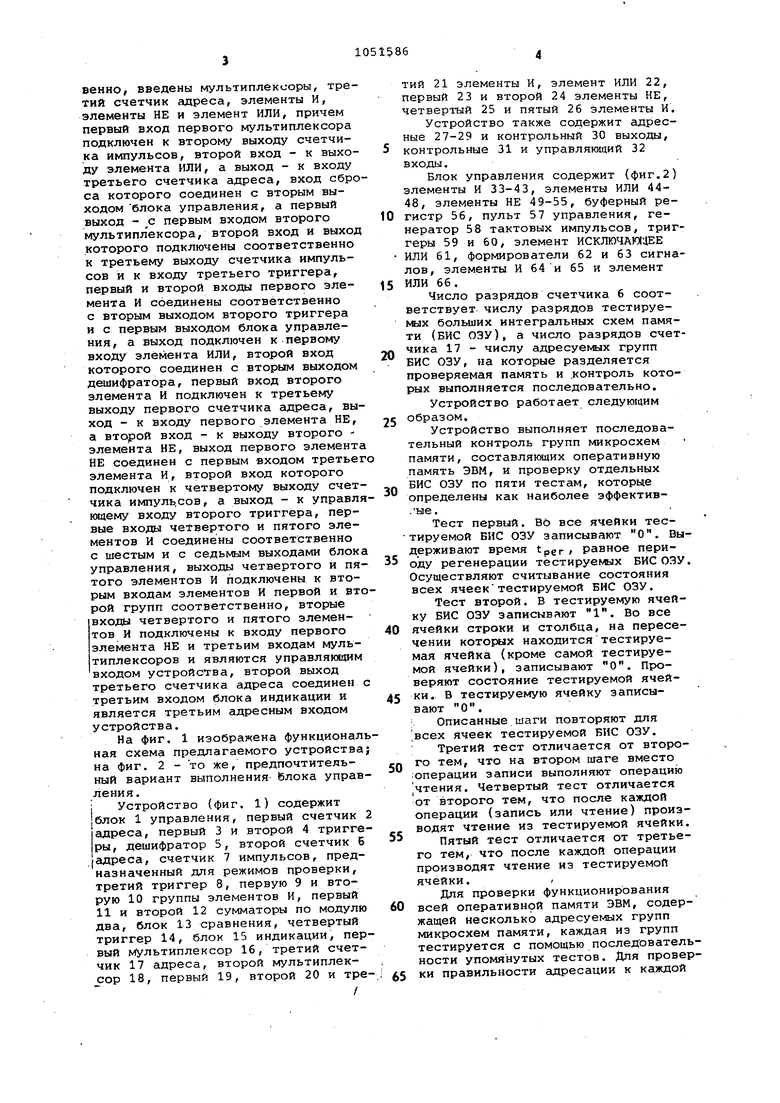

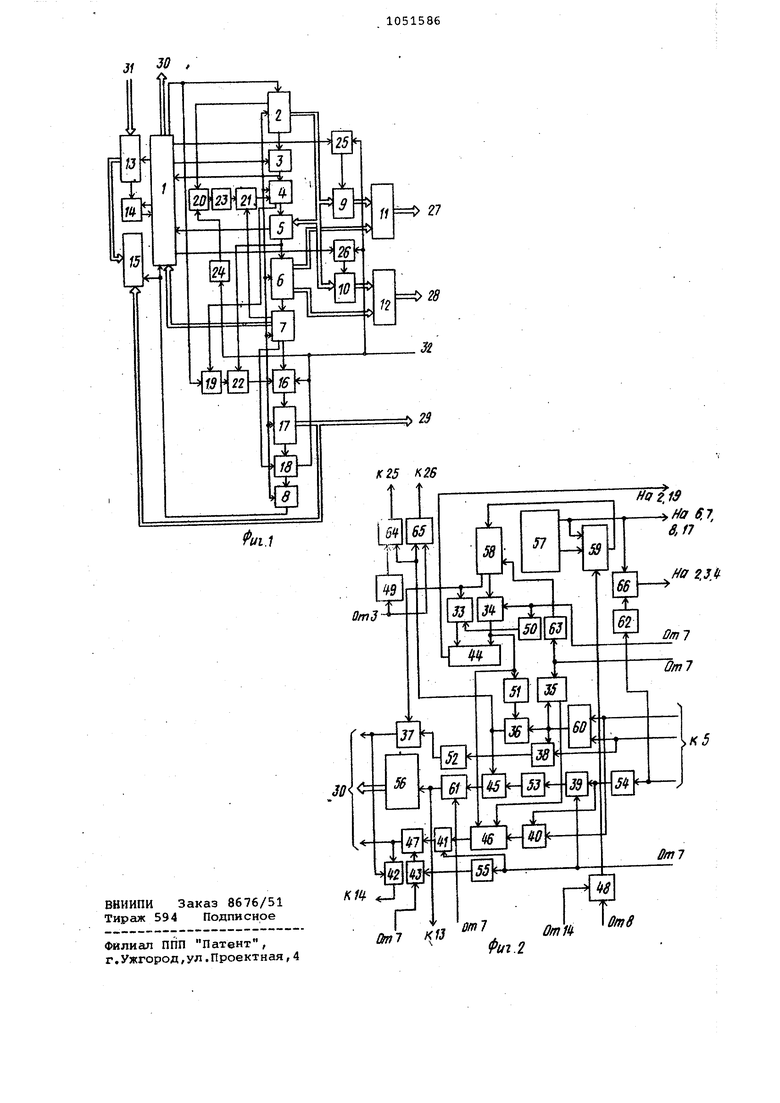

5 блока индикации и с первым входом четвертого триггера, второй вход и выход которого подключены соответственно к четвертому выход и к пятому входу блока управления, пятый выл ход которого и вход блока сравнения являются соответственно контрольдшми выходом и входом устройства, .,, первым и вторым адресными выходами которого являются выходы первого и второго сумматоров по модулю два соответственнО; введены мультиплексоры, третий счетчик адреса, элементы И, элементы НЕ и элемент ИЛИ, причем первый вход первого мультиплексора подключен к второму выходу счетчика импульсов, второй вход - к выходу элемента ИЛИ, а выход - к входу третьего счетчика адреса, вход сбро са которого соединен с вторым выходом блока управления, а первый выход - с первым входом второго мультиплексора, второй вход и выход которого подключены соответственно к третьему выходу счетчика импульсов и к входу третьего триггера, первый и второй входа первого элемента И соединены соответственно с вторым выходом второго триггера и с первым выходом блока управления, а выход подключен к первому входу элемента ИЛИ, второй вход которого соединен с вторым выходом дешифратора, первый вход второго элемента И подключен к третьему выходу первого счетчика адреса, вы ход - к входу первого элемента НЕ, а второй вход - к выходу второго элемента НЕ, выход первого элемент НЕ соединен с первым входом третье элемента И, второй вход которого подключен к четвертому выходу счет чика импуль.сов, а выход - к управл ющему входу второго триггера, первые входы четвертого и пятого элементов И соединены соответственно с шестым и с седьмым выходами блок управления, выходы четвертого и пя того элементов И подключены к вторым входам элементов И первой и вт рой групп соответственно, вторые входы четвертого и пятого элементов И подключены к входу первого элемента НЕ и третьим входам мультиплексоров и являются управляющим входом устройства, второй выход третьего счетчика адреса соединен третьим входом блока индикации и является третьим адресным входом устройства. На фиг. 1 изображена функционал ная схема предлагаемого устройства на фиг. 2 - то же, предпочтительный вариант выполнения- блока управ ления. Устройство (фиг. 1) содержит блок 1 управления, первый счетчик адреса, первый 3 и второй 4 тригге ры, дешифратор 5, второй счетчик Б адреса, счетчик 7 импульсов, предназначенный для режимов проверки, третий триггер 8, первую 9 и вторую 10 группы элементов И, первый 11 и второй 12 сумматоры по модулю два, блок 13 сравнения, четвертый триггер 14, блок 15 индикации, пер вый ь льтиплексор 16, третий счетчик 17 адреса, второй мультиплексор 18, первый 19, второй 20 и тре тий 21 элементы И, элемент ИЛИ 22, первый 23 и второй 24 элементы НЕ, четвертый 25 и пятый 26 элементы И. Устройство также содержит адресные 27-29 и контрольный 30 выходы, контрольные 31 и управляющий 32 входы. Блок управления содержит (фиг.2) элементы И 33-43, элементы ИЛИ 4448, элементы НЕ 49-55, буферный регистр 56, пульт 57 управления, генератор 58 тактовых импульсов, триггеры 59 и 60, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 61, формирователи 62 и 63 сигналов, элементы И 64и 65 и элемент ИЛИ 66. Число разрядов счетчика 6 соответствует числу разрядов тестируекых больших интегральных схем памяти (БИС ОЗУ), а число разрядов счетчика 17 - числу адресуекых групп БИС ОЗУ, на которые разделяется проверяемая память и .контроль которых выполняется последовательно. Устройство работает следующим образом. Устройство выполняет последовательный контроль групп микросхем памяти, составляющих оперативную память ЭВМ, и проверку отдельных БИС ОЗУ по пяти тестам, которые определены как наиболее эффективные. Тест первый. Во все ячейки тестируемой БИС ОЗУ записывают О. Выдерживают время tper, равное периоду регенерации тестируемых БИС ОЗУ. Осуществляют считывание состояния всех ячеек тестируемой БИС ОЗУ. Тест второй. В тестируемую ячейку БИС ОЗУ записывают 1. Во все ячейки строки и столбца, на пересечении которых находится тестируемая ячейка (кроме самой тестируемой ячейки), записывают О. Проверяют состояние тестируемой ячейки. В тестируемую ячейку записывают О. ; Описанные.шаги повторяют для всех ячеек тестируемой БИС ОЗУ. Третий тест отличается от второго тем, что на втором Шаге вместо :операции записи выполняют операцию чтения. Четвертый тест отличается от второго тем, что после каждой операции (запись или чтение) производят чтение из тестируемой ячейки. Пятый тест отличается от третьего тем, что после каждой операции производят чтение из тестируемой ячейки. , Для проверки функционирования всей оперативной памяти ЭВМ, содержащей несколько адресуег-1ых групп микросхем памяти, каждая из групп тестируется с помощью последовательности упомянутых тестов. Для проверки правильности адресации к каждой

группе проводят также дополнительный тест. В выбранную ячейку выбранной группы записывают 1 в те же ячейки остальных групп записывают О, проверяют состояние выбранной ячейки выбранной группы, в ту же ячейку той же группы записывают О,

Первый - четвертый шаги выполн яют для всех групп микросхем па%яти и повторяются с инверсными данными.

Счетчик б (фиг. 1) предназначен для установки кода адреса тестируемой ячейки. Счетчик 2 предназначен для установки кода адреса строки или столбца. Код адреса ячейки строки или столбца, на пересечении которых находится тестируемая ячейка, формируется путем суммирования части кода адреса строки или столбЦа со счетчиком 6 с кодом, установленным на счетчике 2. Ори-этом с выхода сумматора 11 снимается код адреса строки (на адресный выход 27) а с выхода сумматора 12 - код адреса столбца (на адресный выход 28). При нулевом состоянии счетчика 2 обращение осуществляется по адресу тестируемой ячейки. Счетчик 17 предназначен для установки кода адреса группы микросхем. БЛОК 1 вырабатывает тактовые импульсы, под действием которых счетчик 2 последовательно изменяет свое состояние. При переходе счетчика 2 из состояния Все единицы в состояние Все нули триггер 3 изменяет свое состояние, обеспечивая последовательное обращение сначала к ячейкам строки тестируемой БИС ОЗУ, затем к ячейкам столбца путем разрешения передачи на входы сумматоров 11 и 12 кода со счетчика 2 или через блок 10, или через блок 9.

Чтобы исключить обращение к тестируемой ячейке, блок запрещает обращения к проверяемой памяти при обнаружении дешифратором 5 нулевого состояния счетчика 2 при единичном состоянии триггера 3. При изменении состояния триггера 3 из 1 в О триггер 4 устанавливается в 1. При этом передача кода со счетчика 2 через блоки 9 и 10 запрещается, и на выходы 27 и 28 со счетчика передается код адреса тестируемой ячейки. Дешифратор 5 дешифрирует состояние первых двух разрядов счетчика 2. при еостояиии 00 блок 1 вырабатывает операцию чтения состояния тестируемой ячейки памяти, при состоянии 01 - операции записи в тестируемую ячейку. При обнаружении дешифратором 5 состояния 10 счетчика 2 блок 1 сбрасывает счетчик 2, триггеры 3 и 4, и сигнал с дешифратора 5 увеличивает на единицу состояние

счетчика 6. Процесс повторяется до N-ro состояния счетчика 6, после которого изменяется состояние счетчика 7.

Счетчик 7 обеспечивает перевод блока 1 на соответствующий режим работы. В состоянии ХХОО счетчика 7 (X - безразличное состояние) устройство вырабатывает установочную последовательность. При этом логический О с нулевого разряда с счетчика 7 (четвертый выход счетчика 7) вызывает появление О на выходе элемента И 21, который поддерживает триггер 4 состоянии 1. Этим обеспечивается последовательная запись требуемого кода во все ячейки проверяемой БИС ОЗУ. В состоянии ХХ01 устройство вырабатывает последовательность операций чтения из все ячеек проверяемой микросхемы (операцию определяет младший разряд счетчика 7), При переходе счетчика 7 из состояния ХХОО. в состояние, ХХ01 блок 1 задерживает работу устройства на время, равное периоду регенерации тестируемых микросхем памяти. В состоянии 0X10 выполняется второ тест, в состоянии 0X11 - третий, в состоянии 1X10 - четвертый, в состоянии 1X11 - пятый. В состоянии IXXX в отличие от состояния ОХХХ 7 на вход счетчика 2 из блока 1 поступает каждый второй (четный) тактовый импульс. При этом на каж,пый четный тактовый импульс осуществляется чтение состояния тестируемой ячейки, после которого из1у|еняется состояние счетчика 2. Этим обеспечивается формирование четвертого и пятого тестов. В состоянии ХОХХ тесты проводятся на фоне нулей, а в состоянии Х1ХХ - на фоне единиц.

Устройство осуществляет контроль одновременно группы микросхем памяти Управляющие сигналы на входы тестируемых микросхем с выхода 30 выдает блок 1. Информация, снимаемая с выходов проверяемых микросхем на вход 31 устройстга, при считывании сравнивается блоком 13 с требуемой и результат сравнения фиксируется триггером 14. При фиксации ошибки работа устройства прекращается, и блок 15 индицирует номер неисправной микросхемы памяти.

Наличие счетчика 17 и двух мульти плексоров 16 и 18 обеспечивает возможность осуществлять контроль всей оперативной памяти 3BMj которая содержит адресуемые группы микросхем памяти. Число состояний счетчика 17 соответствует числу групп микросхем памяти. Для последовательной прозерки всех групп микросхем памяти (первый режим) на входе 32 устанавливается логическая 1 и мультиплексоры 16 и 18 устанавливаются на передачу сигналов с выхода счетчика 7 и счетчика 17 соответственно. При этом после проверки каждой группы микросхем (при переходе счетчика 7 из состояния 1111 в состояние 0000) счетчик 17 изменяет свое состояние, обеспечивая адресацию к новой группе микросхем. Блок 15 индицирует-номер тестируемой группы. При отсутствии неисправностей при переходе счетчика 17 в нулевое состояние триггер 8 переключается в 1, фиксируя конец проверки. Состояние триггера 8 индицируется.

Для полного контроля всей оперативной пa lяти ЭВМ, кроме проверки каждой группы, вырабатывается дополнительный тест. Для перевода устройства в этот режим работы (второй режим) на входе 32 устанавливается О, вследствие чего мультиплексоры 16 и 18 устанавливаются на передачу сигналов с-выхода блока 1 и с выхода второго разряда счетчика 7 соответственно, и передача кодов через блоки 9 и 10 запрещается. В этом случае счетчик 17 работает синхронно со счетчиком 2 и обеспечивает в каждом такте обращение к ячейкам микросхем различных групп. На выходы 27 и 28 при этом передается код со счетчика 6.

Работа блока 1 в этом режиме не отличается от его работы в первом. Выработка установочной последоввтельности не запрещается. Дополнительный тест отличается от второго теста лишь изменением порядка адресации. При формировании дополнительного теста работа элемента И 20 не запрещена, и на вход установки 1 триггера 4 передается сигнал с выхода счетчика 2, информирующий об обнаружении состояния счетчика 2, соответствующего проверяемой группе микросхем. При нулевом состоянии счетчика 2 осуществляется обращение к ячейке памяти (адipec которой установлен на счетчике 6 группы, адрес которой установлен на счетчике 17. Затем осуществляется параллельное изменение состояний, счетчиков 17 и 2, обеспечивая обращение к той же ячейке остальных групп (второй шаг теста).

При обнаружении дешифратором 5 соответствующего номеру группы состояния счетчика 2 триггер 4 устанавливается в 1, дешифратор 5 де-. шифрирует состояние первых двух разрядов счетчика 2 и устройство последовательно выполняет третий и четвертый шаги теста. При этом О с инверсного выхода триггера 4 запрещает передачу импульсов с выхода блока 1 через элемент И 19, и состояние счетчика 17 не изменяется. С

выхода счетчика 17 снимается адрес группы микросхем (после выполнения второго шага теста счетчик 17 возвращается в свое состояние, поскольку число групп микросхем, проверяемого ОЗУ, кратно степени двум).

После этого сигнал с выхода дешифратора 5 изменяет состояние счетчика б и через элемент ИЛИ 22 - состояние счетчика 17, обеспечивая адресацию к следукнцей группе. Процесс повторяется для всех групп. При переходе второго разряда счетчика 7 из состояния 1 в состояние

О триггер 8 переходит в состояние 1, информируя о конце проверки,

Йульт 57 (фиг. 2) предназначен для установки требуемого режима работы устройства, установки в исходное состояние и запуска устройства. Генератор 58 синхронизирует работу устройства. Регистр 56 предназначен для согласования нагрузочной способности. С выхода регистра 56 снимаются записываемые данные, с выхода элемента И 37 - сигнал синхронизации работы контролируемого ОЗУ, а с выхода элемента ИЛИ 47 - код записи-чтения.

Таким образом, устройство выполняет контроль оперативной памяти не только на уровне отдельных БИС ОЗУ, но и на уровне групп БИС (т.е. на уровне cиcтe - ы), что повышает надежность устройства.

Предлагаемое устройство может быть использовано (в отличие от прототипа) также в качестве сервисного оборудования для профилакти- ,

ческого контроля ОЗУ ЭВМ непосредственно в процессе ее эксплуатации и при их наладке на стадии производства.

Технико-экономическое преимущестВО предлагаемого устройства заключается в его более высокой надежности по сравнению с прототипом.

J/ P

Ul.1

ffa 6.1 8,П

на 2,3,11

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля накопителя информации оперативного запоминающего устройства | 1976 |

|

SU622174A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке I 3299327/18-24, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-10-30—Публикация

1982-07-05—Подача