Изобретение относится к вычисли.тельной технике и может быть использовано в устройствах автоматики и измерительной техники.

Известно аналоговое запоминанидее устройство,содержащее накопитель информации ,сумматор,вычитатель,фиксаторы уровня и аналоговый ключ 1.

Однако Известное устройство не позволяет быстро считать информацию с накопителя, поскольку для считывания требуется несколько циклов обращения к накопителю.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее два накопителя информации, один для грубого приближения, другой - для точного, сумматор и вычитатель, причем вход уменьшаемого вычитателя соединен с источником входного сигнала, вход вычитаемого - с выходом накопителя грубого -приближения, а выход вычитателя - с накопителем точного приближения, выходы накопителей присоединены к сумматору, выход которого является выходом устройства, а вход накопителя грубого приближения соединен с источ- НИКОМ входного сигнала 2.

Однако известное устройство, обладая высоким быстродействием при записи и при считывании, не обеспечивает точности при хранении информации, поскольку ошибка, возникающая при хранении информации (из-за медленного изменения состояния носителя информации, из-за изменения внешних условий и т.д.), определяется накопителем грубого приближения и не корректируется.

Целью изобретения является повышение точности устройства.

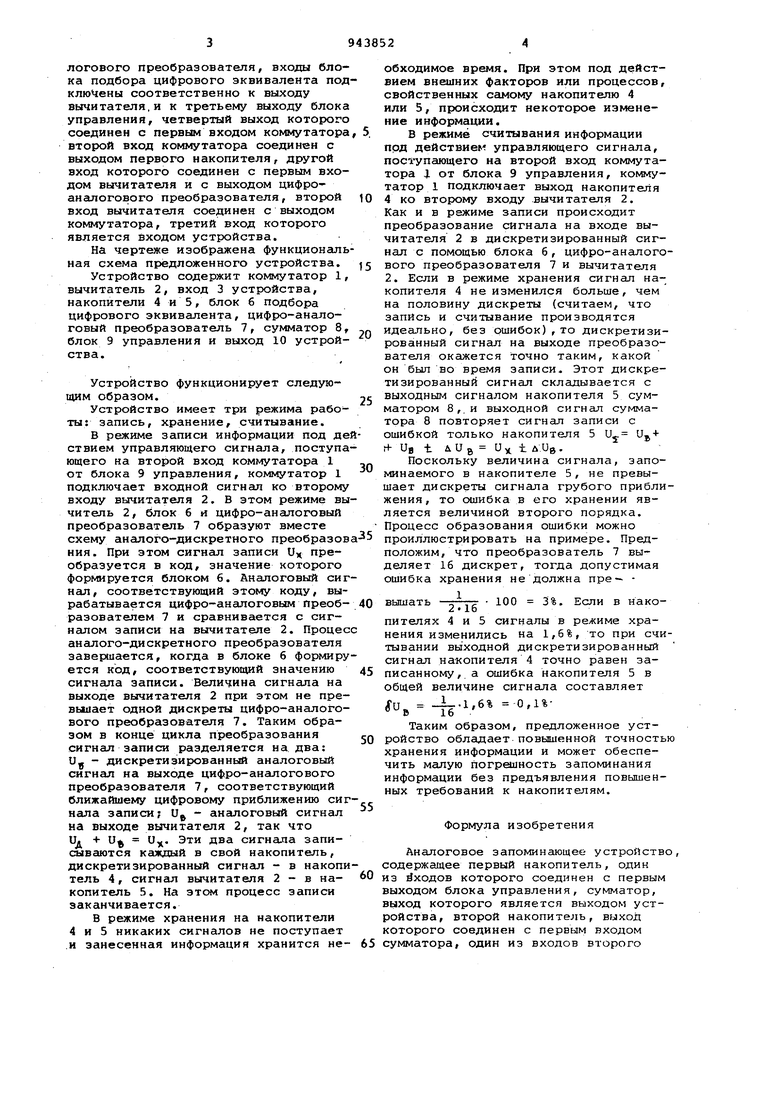

Поставленная;, цель достигается тем, чтоустройство, содержгицее перваЛ накопитель, один из входов которого соединен с первым выходом блока управления, сумматор, выход которого является выходом устройства, второй накопитель, выход которого соединен с первым входом сумматора, один из входов второго накопителя соединен . со вторым выходом блока управления, и вычитатель, выход которого соединен с другим входом второго накопителя , введены коммутатор цифро-аналоговый преобразователь и блок подбо;ра цифрового зквнвалента, выход которого соединен со входом цифро-аналогового преобразователя, входы блока подбора цифрового эквивалента под соответственно к выходу В1лчитателя, и к третьему выходу блока управления, четвертый выход которого соединен с первым входом коммутатора второй вход коммутатора соединен с выходом первого накопителя, другой вход которого соединен с первым входом вычитателя и с выходом цифроаналогового преобразователя, второй вход вычитателя соединен с выходом коммутатора, третий вход которого является йходом устройства. На чертеже изображена функциональ ная схема предложенного устройства. Устройство содержит коммутатор 1, вычитатель 2, вход 3 устройства, накопители 4 и 5, блок б подбора цифрового эквивалента, цифро-аналоговый преобразователь 7, сумматор 8, блок 9 управления и выход 10 устройства. Устройство функционирует следующим образом. Устройство имеет три режима работы; запись, хранение, считывание. В режиме записи информации под де ствием управляющего сигнала, поступа ющего на второй вход коммутатора 1 от блока 9 управления, коммутатор 1 подключает входной сигнал ко второму входу вычитателя 2. В этом режиме вы читель 2, блок 6 и цифро-аналоговый преобразователь 7 образуют вместе схему аналого-дискретного преобразов ния. При этом сигнал записи U преобразуется в код, значение которого формируется блоком 6. Аналоговый сиг нал, соответствующий этому коду, вырабатывается цифро-аналоговым преобразователем 7 и сравнивается с сигналом записи на вычитателе 2. Процес аналого-дискретного преобразователя завершается, когда в блоке 6 формиру ется код, соответствующий значению сигнала записи. Величина сигнала на выходе вычитателя 2 при этом не превьшает одной дискреты цифро-аналогового преобразователя 7. Таким образом в конце цикла преобразования сигнал записи разделяется на два: Од - дискретизированный аналоговый сигнал на выходе цифро-аналогового преобразователя 7, соответствующий ближайшему цифровому приближению сиг нала записи; и - аналоговый сигнал на выходе вычитателя 2, так что и. + и и. Эти два сигнала записываются Кс1ждый в свой накопитель, дискретизированный сигнал - в накопи тель 4, сигнал вычитателя 2 - в накопитель 5. На этом процесс записи заканчивается. В режиме хранения на накопители 4 и 5 никаких сигналов не поступает и занесенная информация хранится необходимое время. При этом под действием внешних факторов или процессов, свойственных самому накопителю 4 или 5, происходит некоторое изменение информации. В режиме считывания информации под действием управляющего сигнала, поступающего на второй вход коммутатора J. от блока 9 управления, коммутатор 1 подключает выход накопителя 4 ко второму входу вычитателя 2. Как и в режиме записи происходит преобразование сигнала на входе вычитателя 2 в дискретизированный сигнал с помощью блока б, цифро-аналогового преобразователя 7 и вычитателя 2. Если в режиме хранения сигнал накопителя 4 не изменился больше, чем на половину дискреты (считаем, что запись и считывание производятся идеально, без ошибок),то дискретизированный сигнал на выходе преобразователя окажется точно таким, какой он был во время записи. Этот дискретизированный сигнал складывается с выходным сигналом накопителя 5 сумматором 8,.и выходной сигнал сумматора 8 повторяет сигнал записи с ошибкой только накопителя 5 Us: t д UB . Поскольку величина сигнала, запоминаемого в накопителе 5, не превышает дискреты сигнала грубого приближения, то ошибка в его хранении является величиной второго порядка. Процесс образования ошибки можно проиллюстрировать на примере. Предположим, что преобразователь 7 выделяет 16 дискрет, тогда допустимая ошибка хранения не должна пре- вышать 100 3%. Если в нако ID пителях 4 и 5 сигналы в режиме хранения изменились на 1,6%, то при считывании выходной дискретизированный сигнал накопителя 4 точно равен записанному, а ошибка накопителя 5 в общей величине сигнала составляет 1,6% 0,1%Таким образом, предложенное устройство обладает повышенной точностью хранения информации и может обеспечить малую погрешность запоминания информации без предъявления повышенных требований к накопителям. Формула изобретения Аналоговое запоминающее устройство, содержащее первый накопитель, один из йходов которого соединен с первым выходом блока управления, сумматор, выход которого является выходом устройства, второй накопитель, выход которого соединен с первым входом сумматора, один из входов второго

накопителя соединен со вторым выходом блока управления, и вычитатапь, выход которого соединен с другим входом вторюго накопителя, отличающееся тем, что, с целью повышения точности устройства, в него введены коммутатор, цифро-аналоговый преобразователь и блок подбора цифрового эквивалента, выход которого соединен со входом цифро-аналогового преобразователя, входы блока подбора. цифрового эквивалента подключены соответственно к выходу вьгчитателя и к третьему выходу блока управления, четвертый выход которого соединен с первым входом коммутатора, второй вход коммутгггора соединен с выходом

первого накопителя, другой вход которого соединен с первым входом вычитателя и с выходом цифро-аналогового преобразователя, второй вход вычитателя соединен с выходом коммутатора, третий вход которого является входом устройства.

гИсточники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР по заявке № 2837183/24,

кл. G 11 С 27/00, 01.11.79.

2.Реализация многозначных структур автоматики. Под ред. М.А. Ракова

I I

Киев, Наукова думка

1976, С.229230 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1981 |

|

SU1003147A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1038967A2 |

| Система автоматического регулирования | 1983 |

|

SU1083158A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство для коррекции временных искажений | 1985 |

|

SU1270797A1 |

| Программируемый генератор импульсов | 1984 |

|

SU1248029A1 |

| КОМПЛЕКС МНОГОКАНАЛЬНОЙ ЭКСПРЕСС ДИАГНОСТИКИ | 1997 |

|

RU2152073C1 |

| Устройство для регулирования расхода | 1986 |

|

SU1377832A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| СПОСОБ СКРЕМБЛИРОВАНИЯ АНАЛОГОВОГО СИГНАЛА И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1997 |

|

RU2123764C1 |

h

W

Авторы

Даты

1982-07-15—Публикация

1980-12-22—Подача