4,. первый регистр 5, блок 6 управления, второй регистр 7, D-триггер 8, вычислитель 9 поправок, цифровой сумматор 10, источник 11 опорного напряжения, датчик 12 преобразуемого кода, переключатель 13. Цель изобретения достигается путем введения D-тригге- ра 8, цифрового сумматора 10, переключателя 13, при этом коррекция выполняется путем модификации кода, по1

Изобретение относится к информационно-измерительной технике и может найти применение в системах сбора и обработки измерительной информации, системах автоматизированного управления, гибридных вычислительных комплексах.

Цель изобретения - упрощение устройства и повьшение быстродействия.

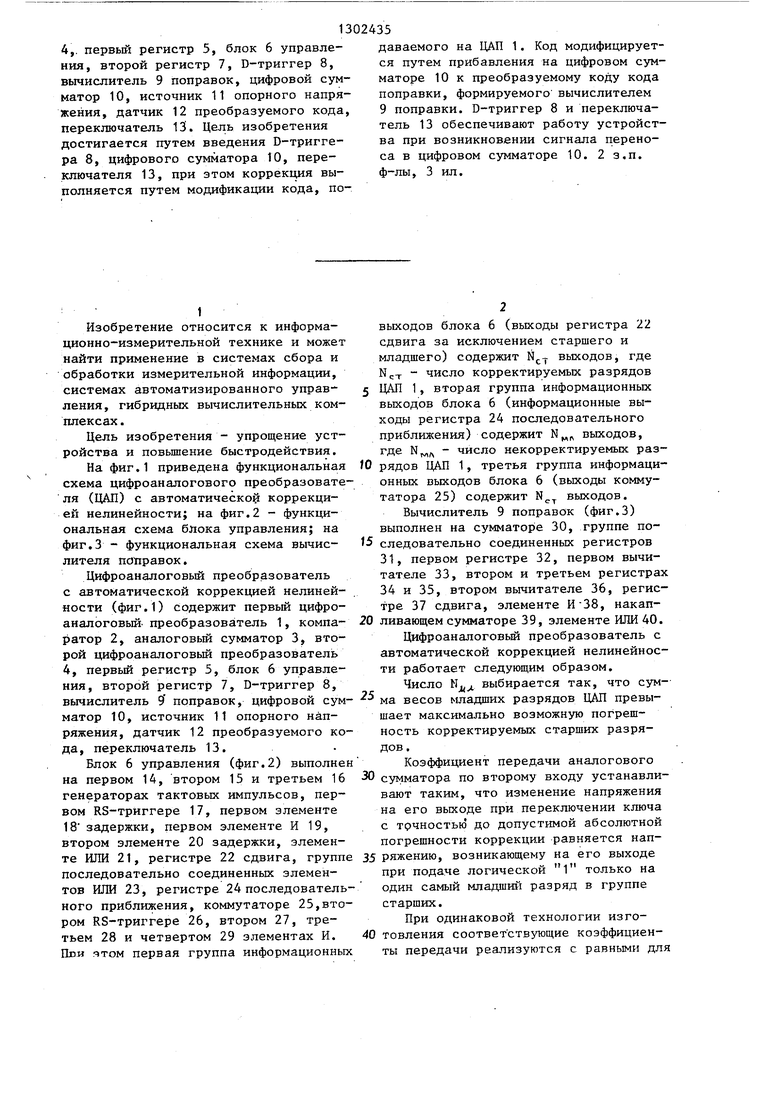

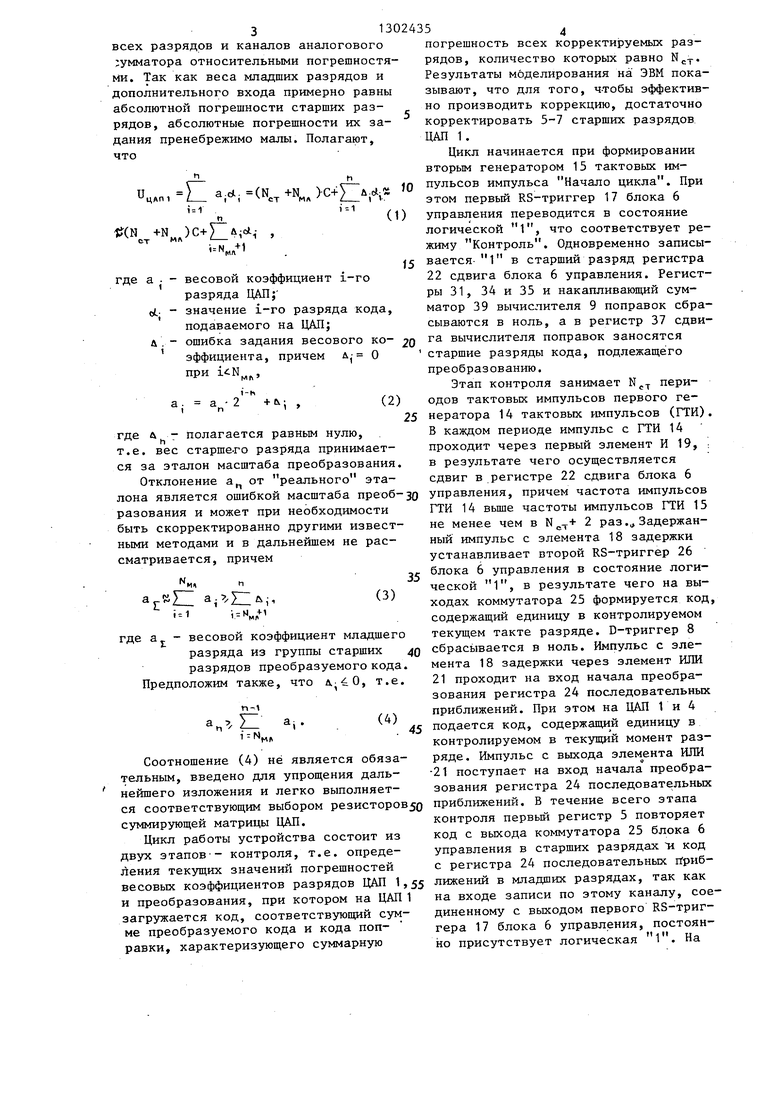

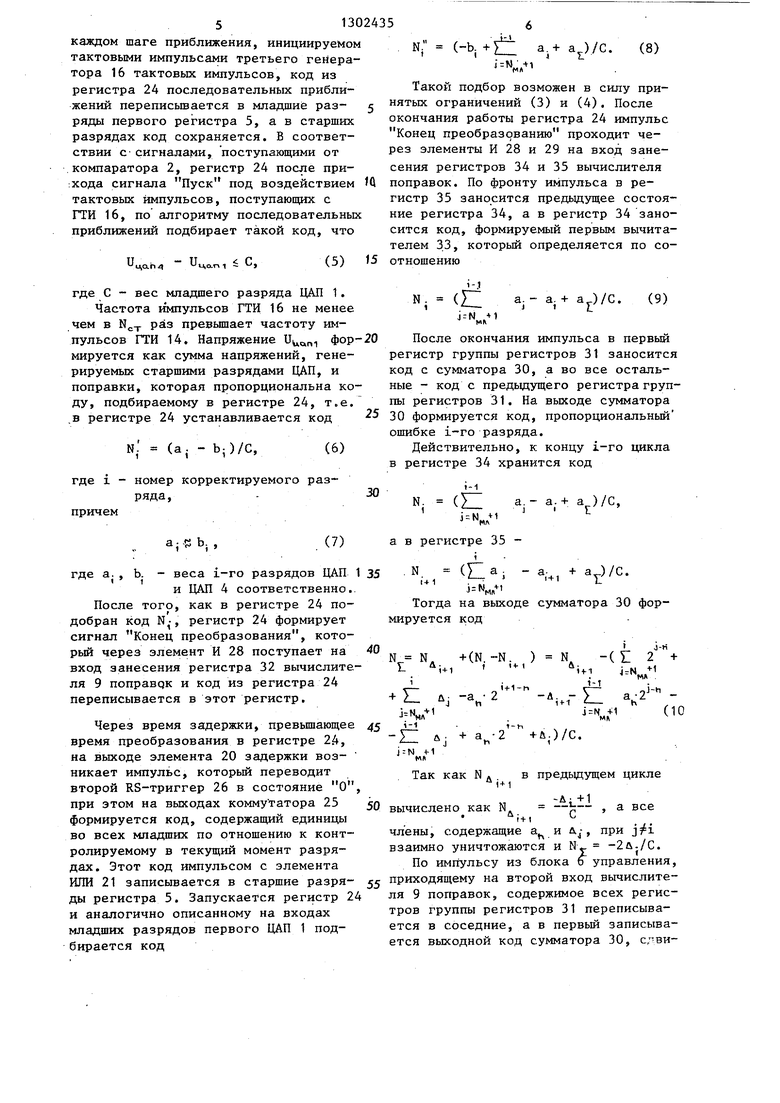

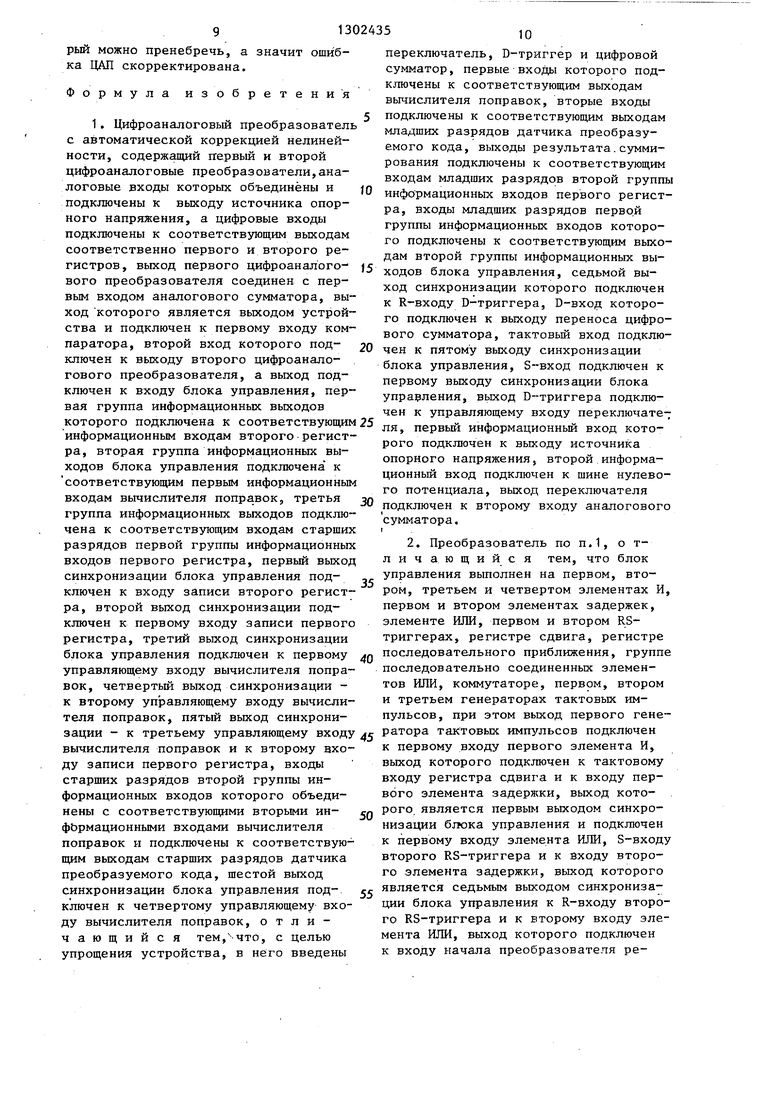

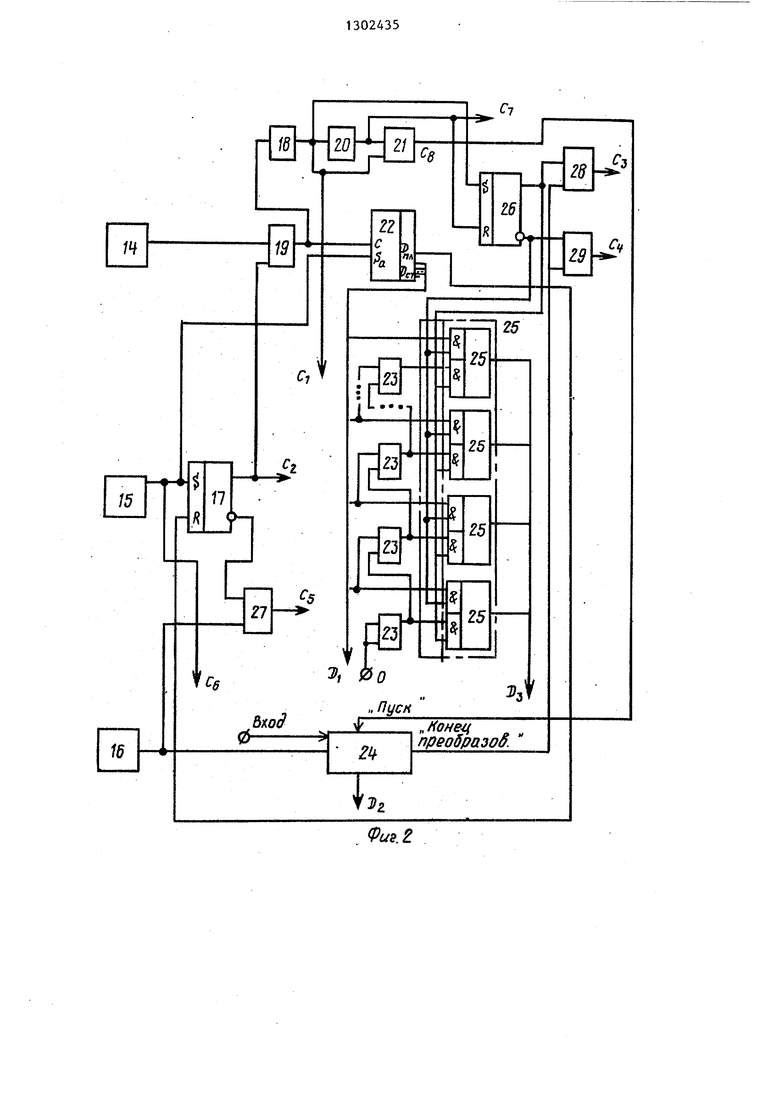

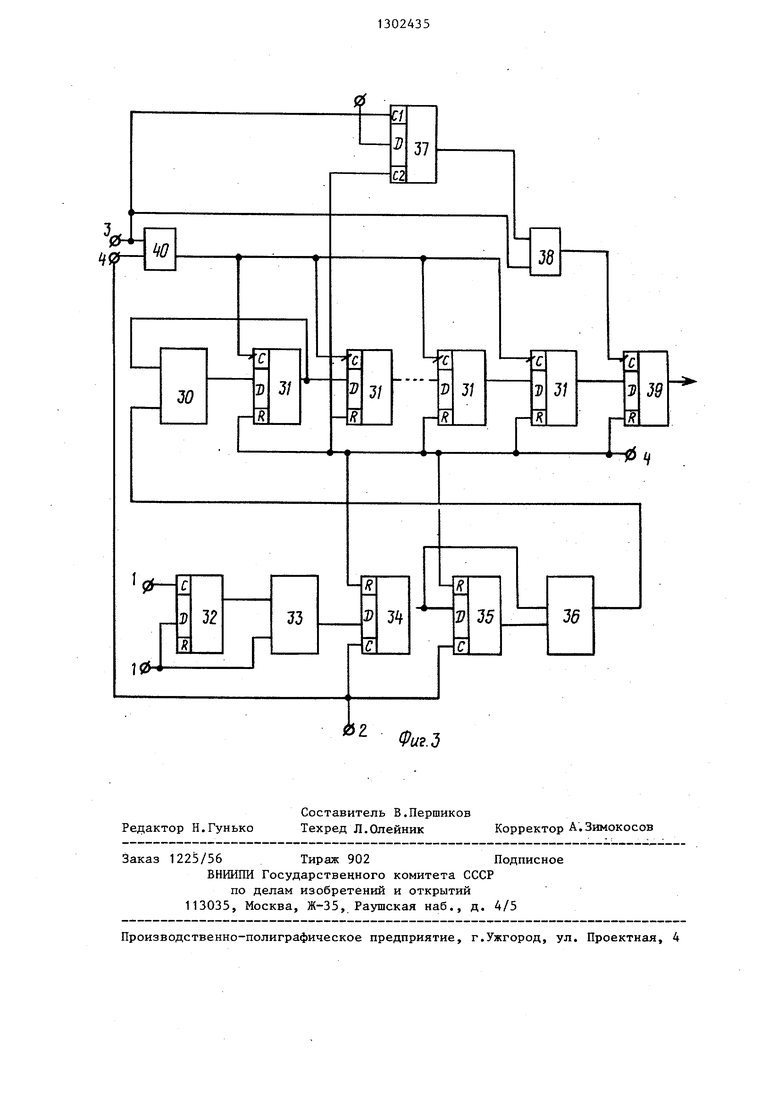

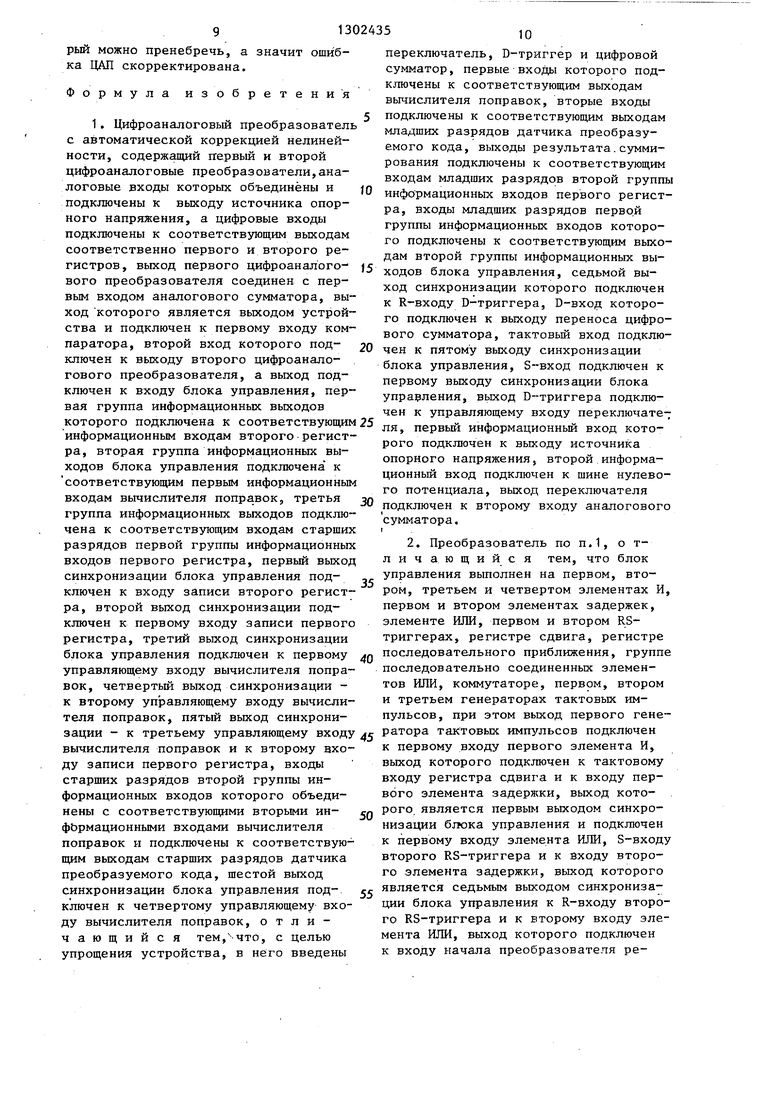

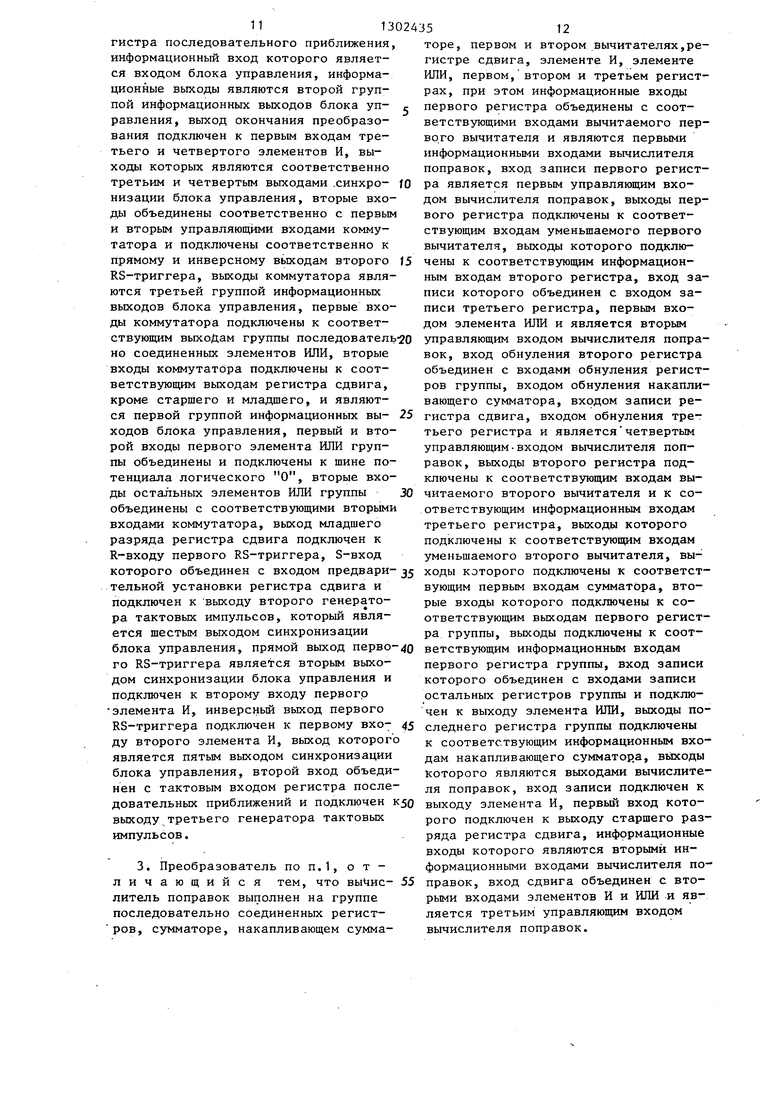

На фиг.1 приведена функциональная схема цифроаналогового преобразователя (ДАН) с автоматической коррекцией нелинейности; на фиг.2 - функциональная схема блока управления; на фиг.З - функциональная схема вычислителя поправок.

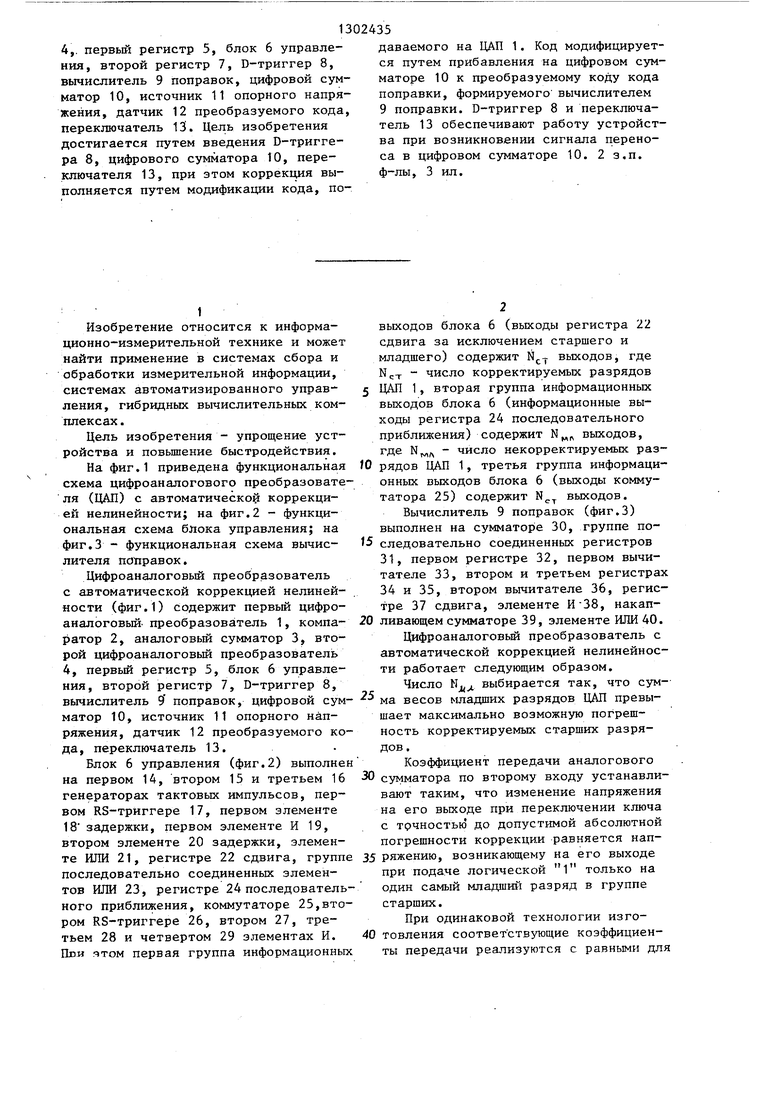

Цифроаналоговый преобразователь с автоматической коррекцией нелинейности (фиг.1) содержит первый цифро- аналоговый преобразователь 1, компаратор 2, аналоговый сумматор 3, второй Цифроаналоговый преобразователь 4, первый регистр 5, блок 6 управления, второй регистр 7, D-триггер 8, вычислитель 9 поправок, цифровой сумматор 10, источник 11 опорного напряжения, датчик 12 преобразуемого кода, переключатель 13.

Блок 6 управления (фиг.2) выполнен на первом 14, втором 15 и третьем 16 генераторах тактовых импульсов, первом RS-триггере 17, первом элементе 18 задержки, первом элементе И 19, втором элементе 20 задержки, элементе ИЛИ 21, регистре 22 сдвига, группе последовательно соединенньк элементов ИЛИ 23, регистре 24 последовательного приближения, коммутаторе 25,втором RS-триггере 26, втором 27, третьем 28 и четвертом 29 элементах И. Пни чтом первая группа информационных

даваемого на ЦАП 1. Код модифицируется путем прибавления на цифровом сумматоре 10 к преобразуемому коду кода поправки, формируемого вычислителем 9 поправки. D-триггер 8 и переключатель 13 обеспечивают работу устройства при возникновении сигнала переноса в цифровом сумматоре 10. 2 з,п. ф-лы, 3 ил.

выходов блока 6 (выходы регистра 22 сдвига за исключением старшего и младшего) содержит . выходов, где NC-T - число корректируемых разрядов

ДАЛ 1, вторая группа информационных выходов блока 6 (информационные выходы регистра 24 последовательного приближения) содержит N выходов, где N - число некорректируемых разрядов ЦАП 1, третья группа информационных выходов блока 6 (выходы коммутатора 25) содержит N выходов.

Вычислитель 9 поправок (фиг.З) выполнен на сумматоре 30, группе последовательно соединенных регистров 31, первом регистре 32, первом вычи- тателе 33, втором и третьем регистрах 34 и 35, втором вычитателе 36, регистре 37 сдвига, элементе И-38, накапливающем сумматоре 39, элементе ИЛИ 40. Цифроаналоговый преобразователь с автоматической коррекцией нелинейности работает следующим образом.

Число выбирается так, что сумма весов младших разрядов ЦАП превышает максимально возможную погрешность корректируемых старших разрядов.

Коэффициент передачи аналогового

сумматора по второму входу устанавливают таким, что изменение напряжения на его выходе при переключении ключа с трчностью до допустимой абсолютной погрешности коррекции равняется напряжению, возникающему на его выходе при подаче логической 1 только на один самый мла;даий разряд в группе старших.

При одинаковой технологии изготовления соответствующие коэффициенты передачи реализуются с равными для

всех разрядов и каналов аналогового сумматора относительными погрешностями. Так как веса младших разрядов и дополнительного входа примерно равны абсолютной погрешности старших разрядов, абсолютные погрешности их задания пренебрежимо малы. Полагают, что

и

ЦАП 1

) a,cA,( i ii- ,

1J-(N +N )

де а ; - весовой коэффициент i-го разряда ЦАП;

значение i-ro разряда кода, подаваемого на ЦАП; ошибка задания весового коэффициента, причем при ,

1

ol:

Л . ,-

О

а

+ ь

где т.е

чполагается равным нулю, вес старше-го разряда принимается за эталон масштаба преобразования,

этаОтклонение а от

реального

25 нератора 14 тактовых импульсов (ГТИ). В каждом периоде импульс с ГТИ 14 проходит через первый элемент И 19, ; в результате чего осуществляется сдвиг в регистре 22 сдвига блока 6

гти

лона является ошибкой масштаба преоб-зо управления, причем частота импульсов разования и может при необходимости быть скорректированно другими известными методами и в дальнейшем не рассматривается, причем

14 вьш1е частоты импульсов ГТИ 15 не менее чем в ,-+ 2 раз. Задержанный импульс с элемента 18 задержки устанавливает второй RS-триггер 26 блока 6 управления в состояние логической 1, в результате чего на выходах коммутатора 25 формируется код, содержащий единицу в контролируемом текущем такте разряде. D-триггер 8 сбрасывается в ноль. Импульс с элемента 18 задержки через элемент ИЛИ 21 проходит на вход начала преобразования регистра 24 последовательных приближений. При этом на ЦАП 1 и 4 45 подается код, содержащими единицу в контролируемом в текущий момент разряде. Импульс с выхода элемента ИЛИ 21 поступает на вход начала преобразования регистра 24 последовательных

N

а..

где 3. - весовой коэффициент младшего

разряда из группы старших 40 разрядов преобразуемого кода. Предположим также, что д.40, т.е.

45

п

i N.,

14 вьш1е частоты импульсов ГТИ 15 не менее чем в ,-+ 2 раз. Задержанный импульс с элемента 18 задержки устанавливает второй RS-триггер 26 блока 6 управления в состояние логической 1, в результате чего на выходах коммутатора 25 формируется код содержащий единицу в контролируемом текущем такте разряде. D-триггер 8 сбрасывается в ноль. Импульс с элемента 18 задержки через элемент ИЛИ 21 проходит на вход начала преобразования регистра 24 последовательных приближений. При этом на ЦАП 1 и 4 45 подается код, содержащими единицу в контролируемом в текущий момент разряде. Импульс с выхода элемента ИЛИ 21 поступает на вход начала преобразования регистра 24 последовательных

Соотношение (4) не является обязательным, введено для упрощения дальнейшего изложения и легко выполняется соответствующим выбором резисторов50 приближений. В течение всего этапа суммирующей матрицы ЦАП.контроля первый регистр 5 повторяет

Цикл работы устройства состоит из код с выхода коммутатора 25 блока 6 двух этапов-- контроля, т.е. определения текущих значений погрешностей

управления в старших разрядах и код с регистра 24 последовательных п рибвесовых коэффициентов разрядов ЦАП 1,55 лижений в младших разрядах, так как

и преобразования, при котором на ЦАП 1 загружается код, соответствующий сумме преобразуемого кода и кода поправки, характеризующего суммарную

погрешность всех корректируемых разрядов, количество которых равно N. Результаты моделирования на ЭВМ показывают, что для того, чтобы эффективно производить коррекцию, достаточно корректировать 5-7 старших разрядов ЦАП 1.

Цикл начинается при формировании вторым генератором 15 тактовых имJQ пульсов импульса Начало цикла. При

этом первый RS-триггер 17 блока 6 ) управления переводится в состояние

логической 1, что соответствует режиму Контроль. Одновременно записыJ5 вается- 1 в старший разряд регистра 22 сдвига блока 6 управления. Регистры 31, 34 и 35 и накапливающий сумматор 39 вычислителя 9 поправок сбрасываются в ноль, а в регистр 37 сдви20 га вычислителя поправок заносятся старшие разряды кода, подлежащего преобразованию.

Этап контроля занимает N периодов тактовых импульсов первого ге25 нератора 14 тактовых импульсов (ГТИ). В каждом периоде импульс с ГТИ 14 проходит через первый элемент И 19, ; в результате чего осуществляется сдвиг в регистре 22 сдвига блока 6

гти

зо управления, причем частота импульсов 35

40

14 вьш1е частоты импульсов ГТИ 15 не менее чем в ,-+ 2 раз. Задержанный импульс с элемента 18 задержки устанавливает второй RS-триггер 26 блока 6 управления в состояние логической 1, в результате чего на выходах коммутатора 25 формируется код, содержащий единицу в контролируемом текущем такте разряде. D-триггер 8 сбрасывается в ноль. Импульс с элемента 18 задержки через элемент ИЛИ 21 проходит на вход начала преобразования регистра 24 последовательных приближений. При этом на ЦАП 1 и 4 45 подается код, содержащими единицу в контролируемом в текущий момент разряде. Импульс с выхода элемента ИЛИ 21 поступает на вход начала преобразования регистра 24 последовательных

50 приближений. В течение всего этапа контроля первый регистр 5 повторяет

код с выхода коммутатора 25 блока 6

управления в старших разрядах и код с регистра 24 последовательных п рибна входе записи по этому каналу, соединенному с выходом первого RS-триг- гера 17 блока 6 управления, постоянно присутствует логическая 1 . На

5130243

каждом шаге приближения, инициируемом тактовыми импульсами третьего генератора 16 тактовых импульсов, код из регистра 24 последовательных приближений переписьюается в младшие раз- 5 ряды первого регистра 5, а в старших разрядах код сохраняется. В соответствии С сигналами, поступающими от .компаратора 2, регистр 24 после при- :Хода сигнала Пуск под воздействием С тактовых импульсов, поступаюпщх с ГТИ 16, по алгоритму последовательных приближений подбирает такой код, что

и

u,ah4

S С,

(5) 15

где С - вес младшего разряда ЦАП 1.

Частота импульсов ГТИ 16 не менее чем в раз превышает частоту импульсов ГТИ 14. Напряжение формируется как сумма напряжений, генерируемых старшими разрядами ЦАП, и поправки, которая пропорциональна коду, подбираемому в регистре 24, т.е. ,в регистре 24 устанавливается код

N, (а. - Ь,)/С,

(6)

где 1 - номер корректируемого разряда,

причем

,.

(7)

где а, ,

Ь. - веса i-ro разрядов ЦАП

и ЦАП 4 соответственно.. После того, как в регистре 24 подобран код , регистр 24 формирует сигнал Конец преобразования, который через элемент И 28 поступает на вход занесения регистра 32 вычислителя 9 поправрк и код из регистра 24 переписывается в этот регистр.

Через время задержки, превьш1ающее время преобразования в регистре 24, на выходе элемента 20 задержки воз- никает импульс, который переводит второй RS-триггер 26 в состояние О при этом на выходах комму татора 25 формируется код, содержащий единицы во всех младших по отношению к контролируемому в текущий момент разрядах. Этот код импульсом с элемента ИЛИ 21 записывается в старшие разря- ды регистра 5. Запускается регистр 24 и аналогично описанному на входах младших разрядов первого ЦАП 1 подбирается код

(-Ь. + :

а. + i

а)/С.

(8)

Такой подбор возможен в силу принятых ограничений (3) и (4). После окончания работы регистра 24 импульс Конец преобразованию проходит через элементы И 28 и 29 на вход занесения регистров 34 и 35 вычислителя поправок. По фронту импульса в регистр 35 заносится предыдущее состояние регистра 34, а в регистр 34 заносится код, формируемый первым вычита- телем 3.3, который определяется по соотношению

i-.1

N- (П j + а )/С. (9)

После окончания импульса в первый регистр группы регистров 31 заносится код с сумматора 30, а во все остальные - код с предьщущего регистра группы регистров 31. На выходе сумматора 30 формируется код, пропорциональный ошибке i-ro разряда.

Действительно, к концу i-ro цикла в регистре 34 хранится код

30

N: (П а - а + а )/С,

а в регистре 35

( - а., + aJ/C.

Г

.

на выходе сумматора 30 форкод

N +(N.-N;. . ) N. -( Е + ь. -

(+1

t ч- 1 i + 1-n

14-1

И А, -а,- 2

-1 . 1-н

EI л. + а -2 +Л.)/С.

1-t

NM,

j-h

-.ГС

J.N.I (10

J N 4-1

tM

д в предьщущем цикле

-Д: +1

.„

Так как N

1+1

вычислено как N.

.

члены, содержащие а и , при взаимно уничтожаются и N.. -2uj/C.

По импульсу из блока 6 управления, приходящему на второй вход вычислителя 9 поправок, содержимое всех регистров группы регистров 31 переписывается в соседние, а в первый записывается выходной код сумматора 30, слви71302435

нутый на один разряд в сторону младших разрядов, т.е. содержимое первого регистра группы регистров 31 устанавливается равным

Мд. д./С.

Погрешность старшего разряда автоматически устанавливается равной нулю за счет того, что в начале цикла контроля регистры 32, 34, 35 обнулены. В каждом следующем такте режима контроля аналогичные действия повторяются. Тогда после N тактов, в п-м регистре группы 31 записан О (ошибка старшего разряда), в п-1 - ошибка второго по старшинству разряда, в п-2 - третьего и так далее до последнего регистра цепочки. После NC-, тактов единица продвигается в регистре 22 сдвига блока управления до его младшего разряда. Как только единица продвинута в последний разряд этого регистра, первый RS-триггер 17 блока управления переводится в состояние О и устройство переходит в режим Преобразование. Величина поправки отличается от ее идеального значения на величину кванта младшего разряда, что является погрешностью масштаба и лег- ко корректируется известными методами

Количество элементов ИЛИ в группе элементов ИЛИ 23 и число выходов коммутатора 25 также равно N..

Импульсы с генератора 16 тактовых импульсов проходят через элемент И 27. Остальные узлы блока 6 управления из- за блокировки элемента И 19 приостанавливают свою работу.

В каждом i-M также режима преобразования, длительность которого равна периоду генератора 16 тактовых импульсов, по фронту импульса выполняется прибавление к содержимому на- капливающего сумматора 39 содержимого последнего регистра группы регистров 31, если в старшем разряде регистра ;i7 сдвига имеется 1, и сохранение состояния сумматора, если в старшем разряде регистра 37 сдвига записан О. После чего (в силу того, что все регистры с динамическим входом) состояние каждого предьщущего регистра переписывается в следующий, а в регистре 37 сдвига выполняется сдвиг на один разряд в сторону старших разрядов, с записью О в младший разряд .

8

Содержимое накапливающего сумматора 39 после i-ro такта соответствует соотношению (9), а после N тактов

NO

nctip

()ъ, .

(12)

Информация с накапливающего сумматора 39 подается на вход цифрового сумматора 10, где складывается с N, разрядами преобразуемого кода. На входы регистра 5 по первому каналу поступает N разряд преобразуемого кода, и по импульсу из блока 6 управления коды записьшаются в первый регистр 5 и поступают на первый цифре- аналоговый преобразователь 1. Если

N„4-1

попр - 2 , т.е. на выходе переполнения цифрового сумматора 10, сигнал соответствует логическому О то на первые входы сумматора 10 поступает код

N N,

+ N.

(13)

а на второй вход сумматора 10 подается нулевой потенциал. Тогда

вых , Z: rf, ai+(N,

Са., + .-ьЫ„„„, -С, i-1 1

что с точностью до малых погрешностей младших разрядов ЦАП 1 совпадает с требуемым выходным напряжением.

Если , то в старшем разряде цифрового сумматора 10 возникает перенос, который фиксируется в D-триггере 8, и на вход аналогового сумматора 3 подается через переключатель 13 напряжение источника 11 опорного напряжения

еых Vni - , (15)

(N,,-N, -В)-С а,

. .

где В 2 - значение младшего бита группы старших разрядов преобразуемого кода,

а в соответствии с формулами (15) и (14) а В-С с точностью до ошибки задания веса младших разрядов, который можно пренебречь, а значит ошибка ЦАП скорректирована.

Формула изобретения

1. Цифроаналоговый преобразователь с автоматической коррекцией нелинейности, содержащий первый и второй цифроаналоговые преобразователи,аналоговые входы которых объединены и подключены к выходу источника опорного напряжения, а цифровые входы подключены к соответствующим выходам соответственно первого и второго регистров, выход первого цифроаналого- вого преобразователя соединен с первым входом аналогового сумматора, выход которого является выходом устройства и подключен к первому входу компаратора, второй вход которого под- ключен к выходу второго цифроанало- , гового преобразователя, а выход подключен к входу блока управления, первая группа информационных выходов которого подключена к соответствующим информационным входам второго регистра, вторая группа информационных выходов блока управления подключена к соответствующим первым информационным входам вычислителя поправок, третья группа информационных выходов подключена к соответствующим входам старших разрядов первой группы информационных входов первого регистра, первый выход синхронизации блока управления подключен к входу записи второго регистра, второй выход синхронизации подключен к первому входу записи первого регистра, третий выход синхронизации блока управления подключен к первому управляющему входу вычислителя поправок, четвертый выход синхронизации

2. Преобразователь по п.1, о т- личающийся тем, что блок управления выполнен на первом, втором, третьем и четвертом элементах И первом и втором элементах задержек, элементе ИЛИ, первом и втором RS- триггерах, регистре сдвига, регистре последовательного приближения, группе последовательно соединенных элементов ИЛИ, коммутаторе, первом, втором и третьем генераторах тактовых импульсов, при этом выход первого генек второму управляющему входу вычислителя поправок, пятый выход синхронизации - к третьему управляющему входу лс ратора тактовых импульсов подключен вычислителя поправок и к второму вхо- к первому входу первого элемента И, ду записи первого регистра, входы выход которого подключен к тактовому

старших разрядов второй группы информационных входов которого объединены с соответствующими вторыми ин- фЬрмационными входами вычислителя поправок и подключены к соответствующим выходам старших разрядов датчика преобразуемого кода, шестой выход синхронизации блока управления под- ключен к четвертому управляющему входу вычислителя поправок, отличающийся тем, что, с целью упрощения устройства, в него введены

f 5 о Q

5

переключатель, D-триггер и цифровой сумматор, первые входы которого подключены к соответствующим выходам вычислителя поправок, вторые входы подключены к соответствуюпщм выходам младших разрядов датчика преобразуемого кода, выходы результата.суммирования подключены к соответствующим входам младших разрядов второй группы информационных входов первого регистра, входы младших разрядов первой группы информационных входов которого подключены к соответствзтощим выходам второй группы информационных выходов блока управления, седьмой выход синхронизации которого подключен к R-входу D-триггера, D-вход которого подключен к выходу переноса цифрового сумматора, тактовый вход подключен к пятому выходу синхронизации блока управления, S-вход подключен к первому выходу синхронизации блока управления, выход D-триггера подключен к управляющему входу переключате-; ля, первый информационньй вход которого подключен к выходу источника опорного напряжения, второй информационный вход подключен к шине нулевого потенциала, выход переключателя подключен к второму входу аналогового сумматора,

г

2. Преобразователь по п.1, о т- личающийся тем, что блок управления выполнен на первом, втором, третьем и четвертом элементах И, первом и втором элементах задержек, элементе ИЛИ, первом и втором RS- триггерах, регистре сдвига, регистре последовательного приближения, группе последовательно соединенных элементов ИЛИ, коммутаторе, первом, втором и третьем генераторах тактовых импульсов, при этом выход первого генес ратора тактовых импульсов подключен к первому входу первого элемента И, выход которого подключен к тактовому

входу регистра сдвига и к входу первого элемента задержки, выход которого, является первым выходом синхронизации блока управления и подключен к первому входу элемента ИЛИ, S-входу второго RS-триггера и к входу второго элемента задержки, выход которого является седьмым выходом синхронизации блока управления к R-входу второго RS-триггера и к второму входу элемента ИШ-Е, выход которого подключен к входу начала преобразователя ре1113

гистра последовательного приближения информационный вход которого является входом блока управления, информационные выходы являются второй группой информационных выходов блока уп- равления, выход окончания преобразования подключен к первым входам третьего и четвертого элементов И, выходы которых являются соответственно третьим и четвертым выходами .синхро- низации блока управления, вторые входы объединены соответственно с первы и вторым управляющими входами коммутатора и подключены соответственно к прямому и инверсному выходам второго RS-триггера, выходы коммутатора являются третьей группой информационных выходов блока управления, первые входы коммутатора подключены к соответствующим выходам группы последовател но соединенных элементов ИЛИ, вторые входы коммутатора подключены к соот- ветствую1цим выходам регистра сдвига, кроме старшего и младшего, и являют

ся первой группой информационных вы- 25 гистра сдвига, входом обнуления треходов блока управления, первый и второй входы первого элемента ИЛИ группы объединены и подключены к шине потенциала логического О, вторые входы остальных элементов ИЛИ группы 30 объединены с соответствующими вторыми входами коммутатора, выход младшего разряда регистра сдвига подключен к R-входу первого RS-триггера, S-вход

которого объединен с входом предвари- j ходы которого подключены к соответст- тельной установки регистра сдвига и подключен к выходу второго генератора тактовых импульсов, который является шестым выходом синхронизации блока управления, прямой выход перво-40 ветствующим информационным входам

вующим первым входам сумматора, вторые входы которого подключены к соответствующим выходам первого регистра группы, выходы подключены к соотго RS-триггера является вторым выходом синхронизации блока управления и подключен к второму входу первого элемента И, инверсный выход первого RS-триггера подключен к первому входу второго элемента И, выход которого является пятым выходом синхронизации блока управления, второй вход объединен с тактовым входом регистра последовательных приближений и подключен KfO выходу элемента И, первьй вход кото- выходу третьего генератора тактовых рого подключен к выходу старшего раз- импульсов.. ряда регистра сдвига, информационные

входы которого являются вторыми информационными входами вычислителя по правок, вход сдвига объединен с вторыми входами элементов И и ИЛИ и является третьим управляющим входом вычислителя поправок.

3. Преобразователь по п.1, о т - личающийся тем, что выЧис- 55 литель поправок выполнен на группе последовательно соединенных регистров, сумматоре, накапливающем сумма5

12

торе, первом и втором вычитателях,регистре сдвига, элементе И, элементе ИЛИ, первом, втором и третьем регистрах, при этом информационные входы первого регистра объединены с соответствующими входами вычитаемого первого вычитателя и являются первыми информационными входами вычислителя поправок, вход записи первого регистра является первым управляющим входом вычислителя поправок, выходы первого регистра подключены к соответствующим входам уменьшаемого первого вычитателя, выходы которого подключены к соответствующим информационным входам второго регистра, вход записи которого объединен с входом записи третьего регистра, первым входом элемента ИЛИ и является вторым управляющим входом вычислителя поправок, вход обнуления второго регистра

объединен с входами обнуления регистров группы, входом обнуления накапливающего сумматора, входом записи ретьего регистра и является четвертым управляющим-входом вычислителя поправок, выходы второго регистра подключены к соответствующим входам вычитаемого второго вычитателя и к соответствующим информационным входам третьего регистра, выходы которого подключены к соответствующим входам уменьшаемого второго вычитателя, выходы которого подключены к соответст- ветствующим информационным входам

вующим первым входам сумматора, вторые входы которого подключены к соответствующим выходам первого регистра группы, выходы подключены к соотпервого регистра группы, вход записи которого объединен с входами записи остальных регистров группы и подключен к выходу элемента ИЛИ, выходы по- следнего регистра группы подключены к соответствующим информационным входам накапливающего сумматора, выходы которого являются выходами вычислителя поправок, вход записи подключен к

Фи8.г

Редактор Н.Гунько

Составитель В.Першиков

Техред Л. Олейник Корректор А. Зимокосов

Заказ 1225/56 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

Фи.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1427564A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Аналого-цифровой преобразователь с коррекцией динамической погрешности | 1987 |

|

SU1607076A1 |

| Аналого-цифровой логарифмический преобразователь | 1984 |

|

SU1236511A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1985 |

|

SU1352650A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

Изобретение относится к информационно-измерительной технике и может найти применение в системах сбора и обработки измерительной информации, , системах автоматического управления, гибридных вычислительных комплексах. Цель изобретения - упрощение устройства и повышение быстродействия.Циф- роанапоговый преобразователь (ЦАП) с автоматической коррекцией нелинейности содержит первый ЦАП 1, компаратор 2, аналоговый сумматор 3, второй ЦАП со О ю со СП

| Цифроаналоговый преобразовательС АВТОМАТичЕСКОй КОРРЕКциЕй НЕли-НЕйНОСТи | 1979 |

|

SU809549A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микроэлектронные кодирующие и де кодирующие преобразователи | |||

| / Под | |||

| ред | |||

| В.В.Смолова | |||

| - Л.: Энергия, 1976, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1987-04-07—Публикация

1985-01-30—Подача