(54) УСТРОЙСТВО ДЛЯ ИНДИКАЦИИ СИНХРОНИЗМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр мгновенных значений | 1988 |

|

SU1553920A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Устройство для управления записью и считыванием информации | 1981 |

|

SU1014028A1 |

| Адаптивный регенератор | 1986 |

|

SU1363490A1 |

| Адаптивный эхокомпенсатор | 1989 |

|

SU1665520A1 |

| Устройство для регистрации информации | 1984 |

|

SU1234858A1 |

| Устройство для синхронизации М-последовательности | 1985 |

|

SU1322429A2 |

| Ключевой элемент | 1987 |

|

SU1432762A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| Управляемый формирователь импульсов | 1988 |

|

SU1559397A1 |

1

Изобретение относится к радиотехническим системам и может быгъ испопьзоваио в системах передачи информации с цифровыми видами модуляции.

Известно устройство для индикации синхронизма, содержащее два инвертора и три триггера i.

Однако известное устройство х фактеризуется низкой помехоустойчивостью.

Цель изобретения - повышение помехоустойчивости.

Цель достигается тем, что в устройство для индикации синхронизма, содержащее первый и второй инверторы, первый, второй и третий триггеры, введены четвертый и пятый триггеры, три счетчика накопителя, третий инвертор, повторитель и два элемента И-ИЛИ, причем прямой и инверсный выходы первого триггера, подключены к первому и второму входам первого элемента И-ИЛИ, 1ФЯМОЙ и инверсный выходы которого подключены соответственно к С-входам четвертого и пятого триггеров, при этом

|Р-вход четвертого триггера через повто1ритель подключен к первому и второму входам второго элемента И-ИЛу, к третьему и четвертому входам которого подключены соответственно прямой и инверсный выходы четвертого триггера, R-ВХОД котсрого через первый инвертор подключен к 5 первого триггера, а инверсный выход второго элементе ИИЛИ подключен к Т)-входу пятого тригге10ра, к R-входу которого подключен гфямой выход второго триггера, к С-входу которого подключен выход первого счетчиканакопителя, а инверсный выход второго триггера подключен к R-входу втсрого

15 счетчика-накопителя, выход которого через второй инвертор подключен к 5 входу третьего триггера, к R-входу уоторого через третий инвертор и R-входу

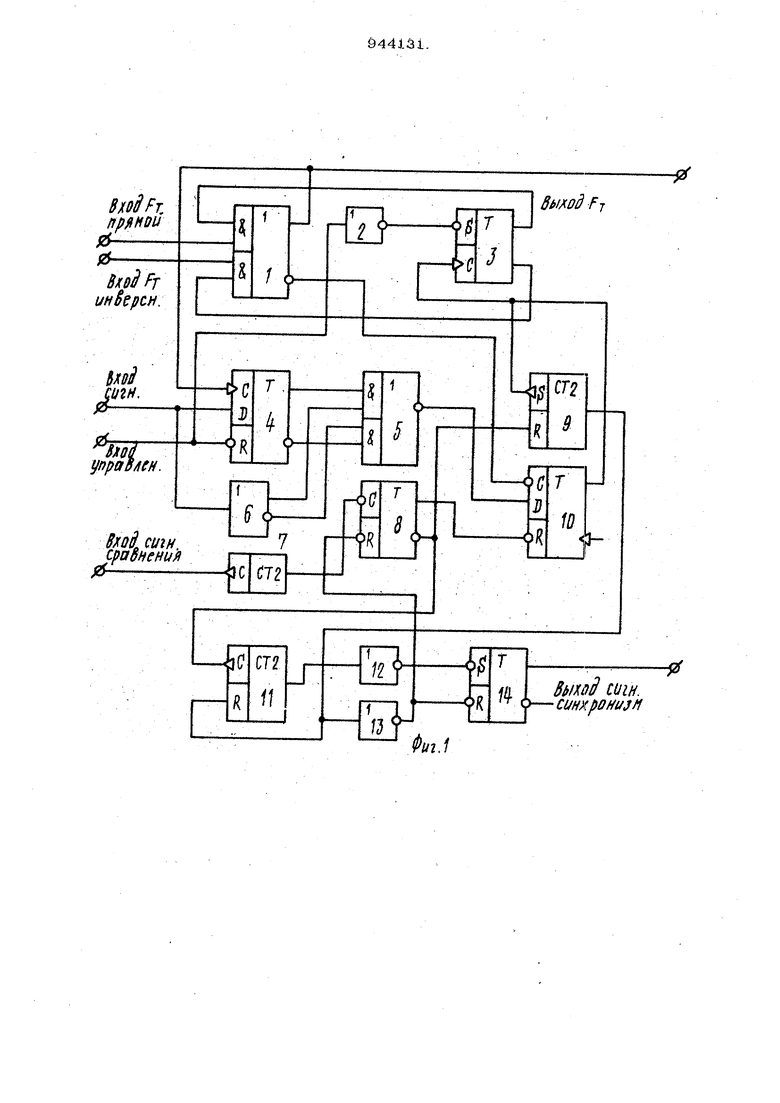

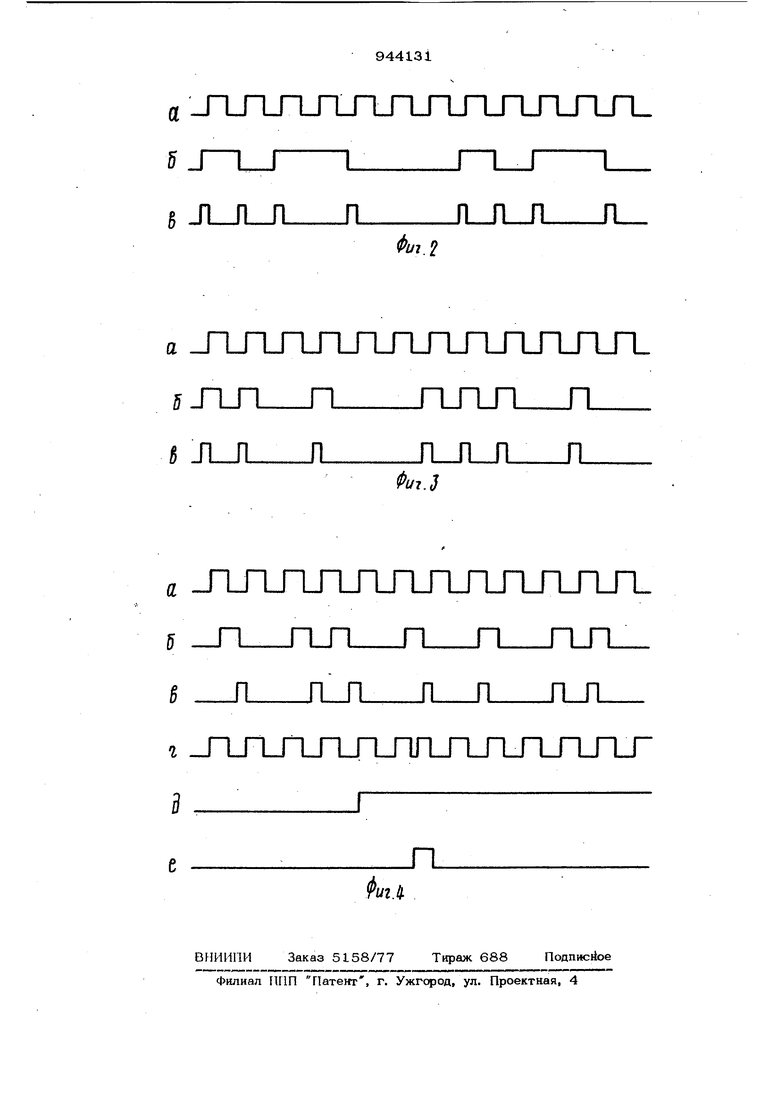

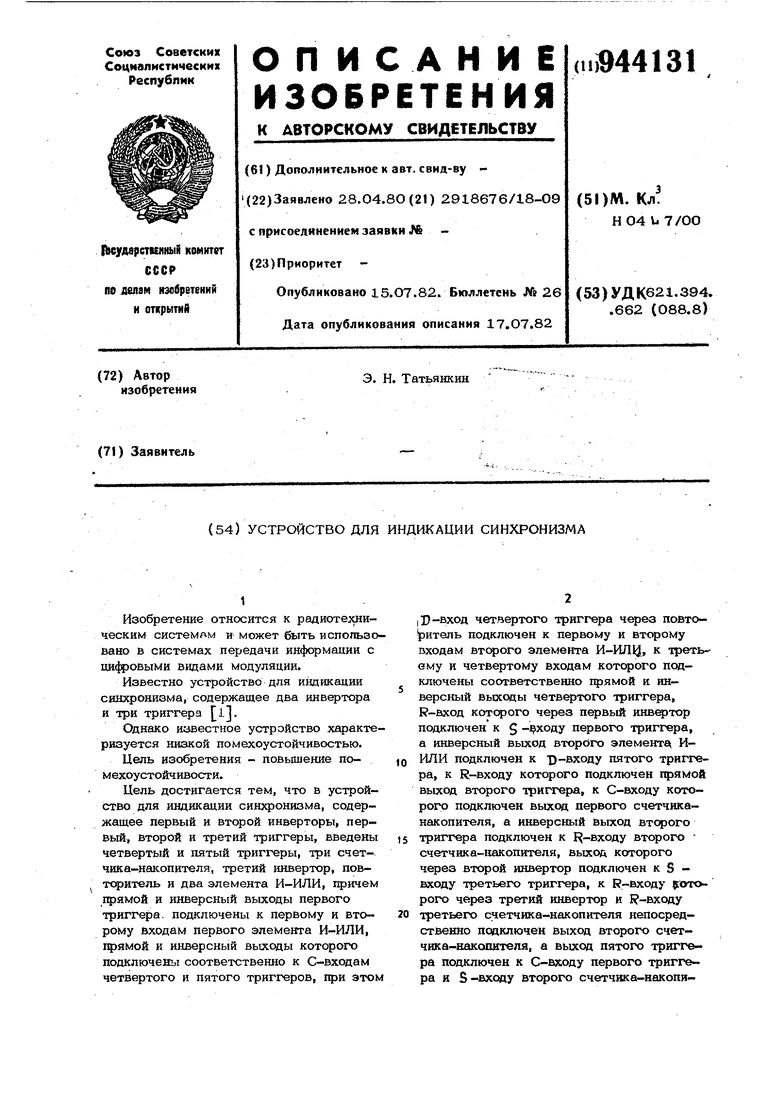

20 третьего счетчика-накопителя непосредственно подключен выход второго счетчика-накошггеля, а выход пятого триггера подключен к С-входу первого триггера и S-входу второго счетчика-накопителя, а выХ.Ьд третьего инвертора подклю чен к Н-вх0ду BTqporo триггера, причем третий и четвертый входы первого элеме та И-ИЛИ, D- и 1 -входы четвертого триггера, С-вход первого счетчика- накопителя являются соответственно прямы , сигнальным входами управле}Шя и сравнения устройства, выходами которого являются С-вхоД тригг а и выход третьего триггера, На фиг. I приведена структурная электрическая схема предложенного устройства; на фиг. 2 --временные диаграммы, отображающие временные соотношения между входными сигналами при различны режимах работы и начальных условиях; на фиг, 3 - то же; на фиг, 4 - то же. Устройство содержит первый элемент И-ИЛИ 1,. инвертор 2, первый триггер 3, четвертый триггер 4, второй элементИ-ИЛИ 5, повтчритель 6, первы счетчик-накопитель 7, втчэрой триггер 8 счетчик-накопитель 9, пятый три гер 1О, третий счетчик-накодитель 11, второй инвертор 12, третий инвертор 13 третий триггер 14. Устройство работает в двух режимах; лрй входном псевдослучайном сигнале вида без воссращения к нулю, при входном псевдослучайном сигнале вида с возвращением к нулю. В первом режиме работы на сигнальный вход устройства поступает сигнал, тфимерный вид которого показан на фиг. фиг, 2 б, В режиме синхронизма входная тактовая частота фиг. 2 а по фазовым соотношениям соответствует фиг. 26, а сигнал на входе сигнала сравнения от фазового детектора соответствует фиг, 2 При работе с сигналом вида без возвращению к нулю на вход управления выбором вида импульсной последовательности поступает логическая -единица, которая разрешает работу второгчэ триггера 4 и через инвертер 2 блокирует работу первого триггера 3, устанавливая на его щэямом выходе логическую единицу. Таким образом, разрешено прохождение 1ш прямой выход первого элемента И-ЙЛИ 1 врямой тактовой частоты. На выходах четвертого триггера 4 присутствует сигнал соответствующий входному по привязанной по фронтам к передним (полож{ггельным) фронтам тактовой часто ТЪ1 а на вь1ходах повторителя 6 входной .сигнал действует без задержки. Фазовые соотношения между сигналом и тактовой час тотой в этом режиме при наличии синхронизма таковы, что за время а« йствия имиу пьса тактовой частоты от переднего фронта До заднего сигнала на информационном входе не меняется, а при отсутствии синхронизма во время тактового импульса может происходить смена информации на входе. Тогда в режимо синхронизма на выходе первого элемента И-ИЛИ 1 на момент появления отрицател ьного периода в прямой тактовой частоте всегда нулевой уровень, а при отсутсл-вии синхронизма может появляться .как нулевой, так и единичный уровень. Следовательно, на Выходе пятого триггера 10 при синхронизме нулевой уровень., а при отсутствий синхронизма формщ)уются импульсы ошибки. Импульсы ошибки поступают на накопитель сигналов ошибки, выполненный на BTqpOM счетчике-накопителе 9 и при заполнении последнего производится установка в начальное состояние накопителя сигналов соответствия режиму сишфонизма, выполненного на третьем сЧетчйке-накопителе 11, а также через третий инвертор 13 - установка третьего триггера 14 в нулевое состояние соответствующее режиму отсу;гствия синхронизма. Кроме того, вь ходной сигнал третьего инвертсч а 13 уста1;1авлиаает в нулевое состояние Итерой триггер 8 и его выходными сигналами устанавливает в нулевое состояние второй счетчик-накопитель 9 и пятый триггер 10. На вход первого счетчика-на|сопнте ля 7 поступают импульсы сигнала сравнения от фазового детектора, а от вькодйого сигнала первого счетчика-накопителя 7 работает второй триггер 8. При этс)м сигнал с выхода второго триггера 8 может быть дополнительно использован в качестве сигнала задающего частот; поиска при работе в составе поисковой системы синхронизации. Этот сигнал производит блок1фовку устройства индикации син: фонизма на время действия нулевог о потенциала на прямом выходе триггера 8, и следовательно емкость первого счетчика-накопителя 7 должна выб1фаться, исходя fsa времени установления переходных Щ)оцессов в поисковой системе, комплектуемой устройством, для индикации сиюфонизма. Если за время действия единичного потенциала на 1ФЯМОМ выходе BTqporo триггера 8 второй счетчик-накопитель 9 сигналов ошибок не успевает заполняться, то при смене знака на выходе этого триггера второй счетчик-накопитель 9 сбрасывается в Нулевое состояние, а в третий счетчик-накопитель 11 записывается единица. Такрм образом, в рюжиме синхронизма третий счетчик накопитель 11 заполняется и через второй инвертор 12 устанавливает третий триггер 14 в единичное состояние, что соответствует наличию на выходе сигнала синхронизма. Емкости счетчиков-накопителей 9 all выбираются по статистическим данным о наличии и распределении ошибок во входном сигнапе, исходя из требований по заданной помехоустойчивости Во втором режиме работы на вход управления выбором вида импульсной по следовательности подан нулевой уровень который блокирует работу четвертого триггера 4, устанавливая на его Е ЗЯМОМ выходе нулевой потенциал и через первый инвертор 2 снимает блокировку с первого триггера 3, управляющего фазировкой выходного сигнала тактовой частоты. В режиме сиюфонкзма при фазировке входньж сигналов в соответствии с фиг. 3. схема работает так же как и в первом режиме, отличие, состоит лишь в том, что заблокирован четвертый ipHr гер 4. Если же при синхронизме фазировка сигналов соответствует фазировке тфиведенной в начале временных диаграмм фиг. 4, после заполнения первого счетчика - накопителя 7 и переключени в единичное состояние второго триггера 8 (фиг. 4д} с 1ФИХОДОМ первого же информационного импульса, на выходе пятого триггера 1О сформирован импуль положительной полярности фиг. 4е, который переключает в противоположное с стояние первый триггер 3 и изменяет тем самым фазировку выходного сигнала тактовой частоты на 18О (фиг. 4г Щ)иводя таким образом в соответствие фазовые соотношения между тактовой частотой и сигналом. При режиме отсутствия синхронизма алгоритмы работы сохраняются как и в первом режиме, с той разницей что происходит поочередное опробывание сигнала с тактовой частотой прямой и инверсной, причем, инверсия происходит каждый раз при фqpм{фoвaнии сигнала ошибки на выходе пятого триггера 10. Технико-экономическая эффективност щэедлагаемого устройства заключается в том, что в отличие от известных, оно позволяет использовать его в составе автоматизированных поисковых систем синхронизации, позволяет определять момент синхронизма при псевдослучайных входных последовательностях как С возвращением, так и без возвращения, к нулю, в том числе гфи поражении входного сигнала помехами. Формула изобретения Устройство для инднкашш сшофовиэма, содержащее первый и второй инверторы, первый, втотой и третий триггеры, отличающееся тем, что, с целью повышений помехоустойчнвостщ введены и пятый триггеры, три счетчика-накопителя, третий инвер- , тор, повторитель и два элемента И-ИЛИ, Щ7ичем щ}ямой и инверсный выходы пер вого триггера, подключены к первому и второму вхсщам первого элемента И-ИЛИ, прямой и инверсный выхопы подключены соответственно к С- ходамчетвертого и пятого TpHTrqpoB, тгря этом D -вход четвертого триггера ч)ез повторитель подключен к первому и второму входам второго элемента И-ИЛИ, к третьему и четвертому входам Korcpoix) подключены еоответствешк прямой и инверсный выходы четвертого TpHTrqpa, R-вход которого через подключен к 5 -входу первого триггера, а инверсный выход второго элемента ИШ1И подключен к D-входу пятого триг гера, к R-Bxoay которого подключен гфямой выход втфого тригг а к С-входу которого додключен выход первого сче-рчнка-накошггеля, а инверсный выход второго триггера подключен к К-входу второго счетчика-накопитеия и С-вкоду третьего счетчика-накопитепя, вькса которого через второй инвертор подключен к 5 -вжоду третьего тригг а, к R-вжаду которого третий ивсвертор и R-BXOду третьего сметчика-накопителя непосредственно подключен выход счетчика-накопителя, а выхсщ пятого триггера подключен к С-входу первого триггера и 5 -входу счетчшсанакопителя, а выход третьего подключен к В-входу трихтера хфичем третий и четвертый входы п вого элемента И-ИЛИ, D- и R-входы чет вертого тригг ш, С-вход первого счетчика-накопителя 5ШПЯЮТСЯ соответственно Щ}ямым, инверсным, сигнальяым аходами управления и сравнения устройства, выходами являются С-вход чет вертого триггера и выход третьего триггера. Источники информации, принятые во внимание 1фи экспертизе 1. Автсрское свидетельство СССР N5 625313, кл. Н O4U 7/ОО, 1976 (хфототип). Sxoifi ZP- 0-- Bxoi FT инёерси. ynpaS/ieH. QuiH. срабнени CUH j}OHUjf1

а JlJTJlJlJlJnjnJlJnj LrLrL g п п п пп п п п а п п J п п

а JTTLTlJlJirLnJlJnJirLrL

5 П П П П П П П « П П П П П п п

1 jnjnjnjTJTJiajTjnj i rLri r

.

Фиг2 ГгЛJlЛJПJnJl ГLГLГL пп П П П пп п п п Фиг.З

Авторы

Даты

1982-07-15—Публикация

1980-04-28—Подача