(54) .ИМПУЛЬСНЫЙ РЕГУЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая система управления | 1984 |

|

SU1234811A1 |

| Устройство для регулирования температуры | 1983 |

|

SU1151932A1 |

| Автоматический регулятор возбуждения для синхронной машины | 1981 |

|

SU1020954A1 |

| Цифровой электропривод | 1983 |

|

SU1102002A1 |

| Многоканальный импульсный регулятор | 1974 |

|

SU565283A1 |

| Многоканальный регулятор температуры | 1991 |

|

SU1783495A1 |

| Многоканальный импульсный регулятор | 1978 |

|

SU767704A2 |

| Устройство для регулирования температуры | 1977 |

|

SU796809A1 |

| Система программного управления электроприводом | 1987 |

|

SU1481708A1 |

| Устройство для стабилизированного питания приемников энергии | 1987 |

|

SU1545290A1 |

Изобретение относится к айтоматике, а именно к устройствам для позиционного регулирования различных технологических параметров, и предназначено для использования в системах регулирования в установках промысловой подготовки нефти.

Известно позиционное регулирующее устройство, содержащее генераторы импульсов, выходы которых подключены к первому входу логического блока, второй вход которого соединен с датчиком сигнала, первый и второй выходы логического блока подключены через первый и второй усилители к первому и второму входам исполнительного механизма. При отклонениях регулируемой величины в пределах заданной зоны регулирования на исполнительный механизм поступают импульсы регулирования от первого генератора, а при отклонениях ее от установленных пределов происходит реверсирование исполнительного механизма и увеличение скорости его перемещения, так как при этом отключается первый и включается второй генератор с большей длительностью импульсов регулирования 1.

Недостатком данного устройства является то, что вне пределов зоны нечувствительности регулирующее вогчдействие, определяемое настройкой второго генератора, остается постоянным независимо от величины возмущения . При большом запасе по регулирукяцему воздействий и больших запаздываниях это может привести к боль10шой амплитуде автоколебаний, а снижение средней скорости отработки сигнала ухудшает способность системы компенсировать возмущение воздействия.

15

Наиболее близким к предлагаемому техническим реиением является Позиционное регулирующее устройство, содержащее логический блок, входы ко20торого подключены к соответствующим входам регулятора, генератор импульсов, первый и второй усилители, выходы которых подключены соответственно к первому и второму выходам уст 25 ройства 2,

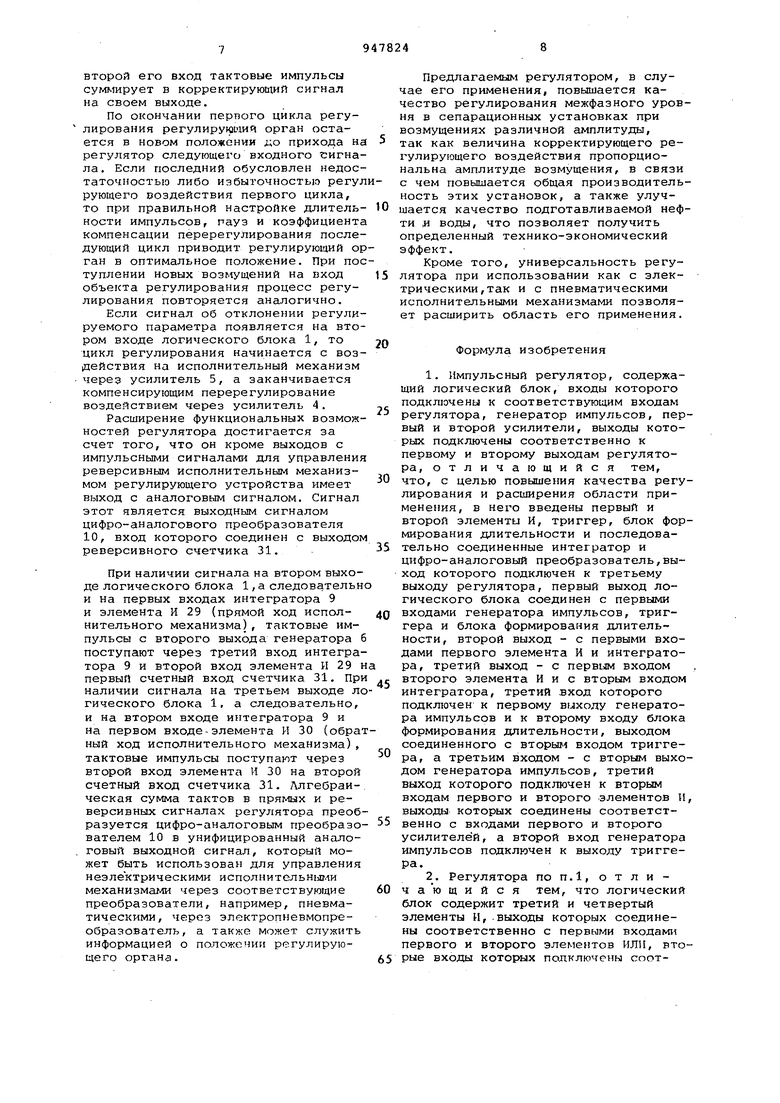

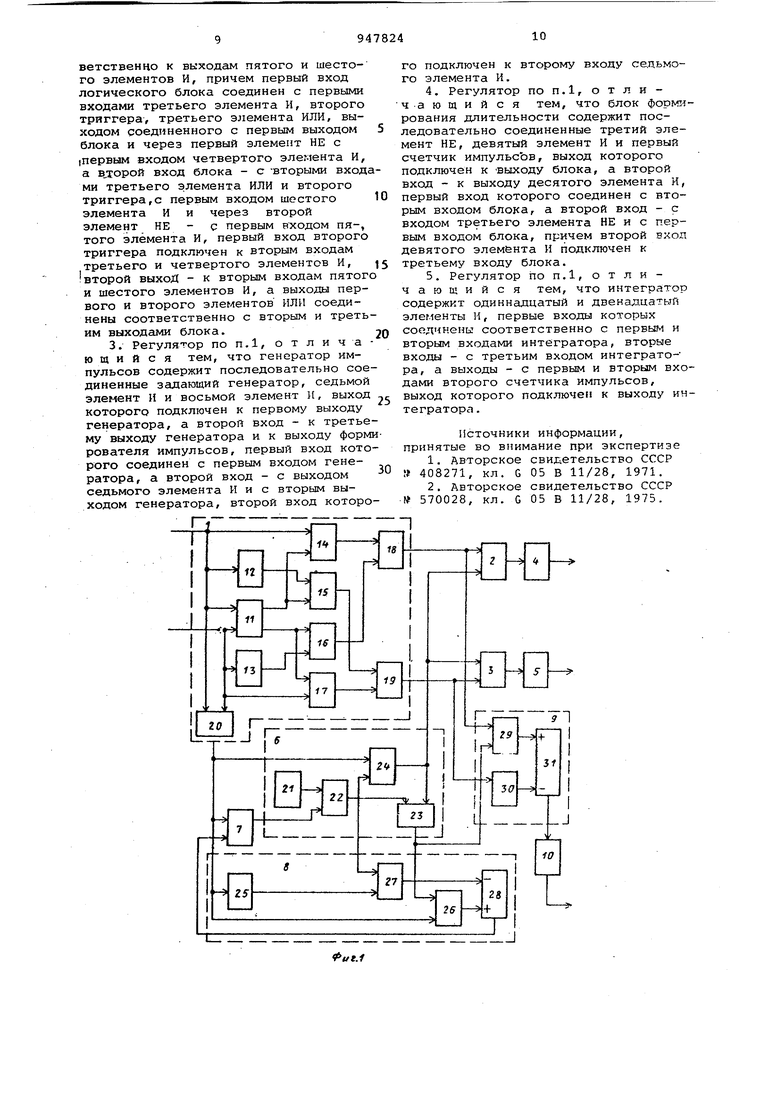

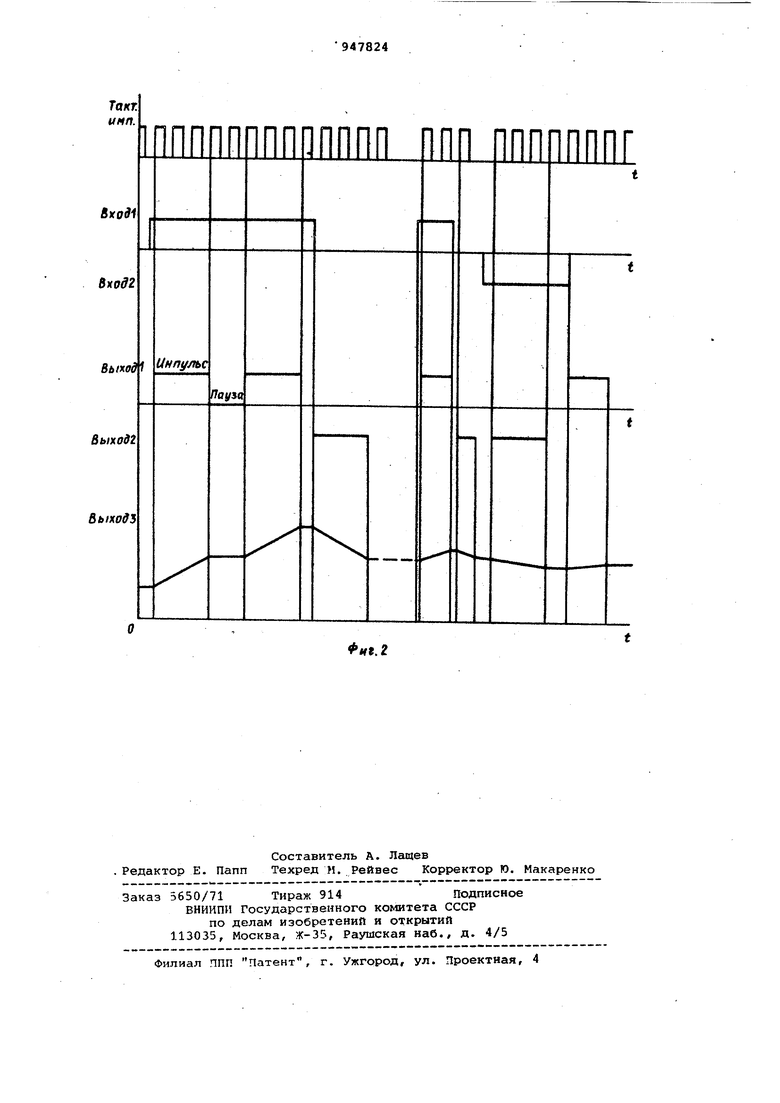

Недостатком известного устройства является низкое качество регулирования при отработке низкочастотных возмущающих воздействий большой ампли30туды, а также отсутствие .возможности управлять исполнительными механизмами аналогового типа. Цель изобретения - повышение качества регулирования и расширение функциональных возможностей регулятора . Указанная цель достигается тем, что в устройство введены первый и вто рой элементы И, триггер, блок форглирования длительности и последовательно соединенные интегратор и цифроаналоговый преобразователь, выход которого подключен к третьему выходу регулятора, первый выход логического блока соединен с первыми входами генератора импульсов, триггера и блока формирования длительности., второй выход - с первыми входами первого элемента И н интегратора, третий выход с первым входом второго элемента И и 0 вторыгл входом интегратора, третий вход которого подключен к первому выходу генератора импульсов и к второ му входу блока формирования длительности , выходом соединенного с вторым входом триггера, а третьим входом вторым выходом генератора импульсов третий выход которого подключен к вто рым входа11 первого и второго элементов И, выходами соединенных соответственно с входами первого и второго усилителей, а второй вход генератора импульсов подключен к выходу триггера. . , При этом логический блок содержит третий и четвертый элементы И, выходы которых соединены соответственно с первыми входами первого и второго элементов ИЛИ, вторые входы которых подключены соответственно к выходам пятого и шестого элементов И, причем первый вход блока соединен с первыми входами третьего элемента И, второго триггера, третьего элемента ИЛИ, выходом соединенного с первым выходом блока и через первый элемент НЕ с ne вым входом четвертого элемента И, а второй вход блока - с вторыми входам третьего элемента ИЛИ и второго триг гера, с первым входом шестого элемен та Н и через второй элемент НЕ - с первым входом пятого элемента Н, пер вый выход второго триггера подключен к вторым входам третьего и четвертог ,элементов И, второй выход - к вторым входам пятого и шестого элементов И, а выходы первого и второго элементов ИЛИ соединены соответственно с вторы и третьим выходами блока. Генератор импульсов содержит последовательно соединенные задающий ге нератор, седьмой элемент И и восьмой элемент И, выход которого подключен к первому выходу генератора, а второ вход - к третьему выходу генератора к выходу формирователя импульсов, пе вый, вход которого соединен с первым входом генератора, а второй вход - с выходом седьмого элемента И и с вторым выходом генератора, второй вход которого подключен к второму входу седьмого элемента И. БЛОК формирования длительности содержит последовательно соединенные третий элемент НЕ, девятый элемент и и первый счетчик иг/тульсов, выход которого подключен к выходу блока, а второй вход - к выходу десятого элемента И, первый вход которого соединен с вторым входом блока, а второй вход - с входом третьего элемента НЕ и с первым входом блока, причем второй вход девятого элемента И подключен к третьему входу блока. Кроме того, интегратор содержит одиннадцатый и двенадцатый элементы И, первый, входы которых соединены соответственно с первьом и вторым входами интегратора, вторые входы - с третьим входом интегратора, а выходы - с первым и вторым входами второго счетчика импульсов, выход Которого подключен к выходу интегратора. Па фиг. 1 приведена блок-схема регулятора; на фиг. 2 - временные диaгpa l и работы регулятора. Блок-схема включает логический блок 1, первый и второй элементы И 2 и 3, первый и второй усилители 4 и 5, генератор 6 импульсов, триггер 7, блок 8 сформирования длительности, интегратф) 9, цифро-аналоговый преобразователь 10, второй триггер 11, первый и второй элементы НЕ 12 и 13, третий, четвертый, пятый и шестой элементы И 14-17, первый,, второй и третий элементы ИЛИ 18-20, задающий генератор 21, седьмой и восьмой элементы И 22 и 23, формирователь 24 импульсов, третий элемент НЕ 25, десятый элемент И 26, девятый элемент И 27, первый счетчик 28 импульсов, одиннадцатый и двенадцатый элементы И 29 и 30, второй счетчик 31. Регулятор работает следующим образом. При достижении peгyлиpye iым параметром одного из крайних значений на один из входов (например на первый) поступает сигнал (фиг. 2). Далее сигнал поступает на вход элемента НЕ 12, первые входы элемента И 14, элемента ИЛИ 20 и триггера 11, устанавливая последний в положение, при котором на первом его выходе присутствует сигнал. Этот сигнал поступает на вторые входы элементов и 14 и 15. При наличии сигналов на обоих входах элемента И 14 появляется сигнал на его выходе к через элемент ИЛИ 18, через второй выход логического блока 1 подается на первый вход элемента И 2. С выхода элеглента ПЛИ 20 сигнал через первыл вьЬсод логического блока 1 поступает на первый вход форми рователя 24 импульсов через первый вход генератора 6 импульсов регулир вания, на первый вход триггера 7, на вход элемента -НЕ 25 и второй вхо элемента И 26 через первый вход бло ка 8 формирования длительности. Иод действием этого сигнала триг гер 7 устанавливается в положение, при котором на его выходе появляется сигнал, который поступает на эле мент Н 22 через второй вход генератора б импульсов. При наличии сигна ла на втором входе элемента И .22 им пульсы, поступающие с задающего генератора 21 на первый вход элемента И 22, поступают на вторые входы фор мирователя 24 импульсов, элемента И 23 и на первый вход элемента И 27 через третий выход генератора 6 импульсов и второй вход блока 8 форми рования длительности. Формирователь 24 импульсов представляет собой пят разрядный двоичный счетчик с задава емым коэффициентом пересчёта, которым определяется длительность перио да импульс-пауза. При поступлении тактовых импульсов на второй вход формирователя 24 на его выходе появляется последовательность импульсов и пауз. Импульс регулирования поступают на второй вход элемента И 2, на первом выходе которого присутствует сигнал с второго выхода -логического блока 1. Импульсы регулирования с выхода эле мента И 2 через усилитель 4 поступают На исполнительный механизм регулирующего органа. Количество импульсов регулирования, т.е. суммарное регулирующее воздействие, .определяется временем Действия сигнала на входе perj/лятора. в результате регулирующего воздействия регулируемый параметр возвращается в пределы зоны регулирования и исчезает сигнал на первых входах логического блока 1, триггера 11, элемента НЕ 12, элемента Н 14 и элемента ИЛИ 20. при этом. исчезает сигнал на первом и втором выходах логического блока 1, На выходе элемента НЕ 12 появляется сигнал, который обеспечивает .прохождение оставшегося неизменным сигнала с первого выхода триггера 11 через элемент И 15. С выхода элемента И 1 сигнал через элемента ИЛИ 19 посту пает через третий выход логического блока il на первый вход элемента И 3 На второй вход элемента И 3 поступает непрерывный сигнал с первого выхода генератора 6 импульсов. Непрерывность его обеспечивается тем, что при снятии сигнала на первом входе формирователя 24 импульсов блокируется формирование пауз между импульсами регулирования на его выходе. Сигнал этот, представляющий импульс регулирования, проходит далее с выхода элемента И 3 через усилитель 5 и второй выход регулятора на реверсивный вход исполнительно- , го механизма, возвращая регулирующий орган частично .в положение, предшествовавшее циклу регулирования. Длительность этого сигнала, корректируницего перерегулирование, определяется промежутком времени между моментом исчезновения сигнала на входе регулятора и переходом триггера 7 в состояние, при котором на его выходе .сигнал исчезает., Перевод триггера 7 в это состояние и завершение цикла регулирования проирходит следующим образом. Во время действия импульса на выходе формирователя 24 сигнал, поступая на первый вход элемента И 23, обеспечивает прохождение тактовых импульсов, поступающих на второй вход этого элемента через второй выход генератора 6 импульсов и третий вход блока 8 на первый вход элемента И 26, на втором входе которого присутствует сигнал с выхода элемента ИЛИ 20. Тактовые импульсы, количество которьйх определяется суммарной длительностью регулирующих импульсов (без учета длительности пауз между ними) поступают с выхода элемента И 26 на второй счетный вход счетчика 28 и считаются последним с заданным коэффициентом деления. Например 2. При исчезновении сигнала с датчика этот сигнал исчезает и на первом входе логического блока 1, на выходе элемента ИЛИ 20, на первом входе блока 8 формирования длительности, т.е. на входе элемента НЕ 25 и на втором . входе элемента И 26. При этом на выходе элемента НЕ появляется сигнал, а на выходе элемента И 26 он исчезает. Тактовые импульсы теперь поступают с выхода элемента И 22 на первый счетный вход счетчика 23. По окончании считывания записанной ранее с учетом коэффициента деления суммы тактовьах импульсов сигнал с нулевого разряда счетчика 28 через выход блока 8 поступает на второй вход триггера 7, на выходе которого до этого продолжает действовать сигнал, устанавливая триггер в положение, при котором сигнал на его выходе исчезает. Быстродействие системы регулирования повышается дополнительно за счет того, что корректируквдий сигнал формируется в формирователе 24 импульсов непрерывным, без пауз. При исчезновении входного сигнала с датчика исчезает и сигнал на первом входе генератора 6 импульсов и соответственно на формирователе 24. Последний при этом все поступающие на второй его вход тактовые импульсы суммирует в корректирующий сигнал на своем выходе. По окончании перБого цикла регулирования регулирукзиий орган остается в новом положении ;о прихода на регулятор следующего входного ;игнала. Если последний обусловлен недостаточностью либо избыточностью регул рующего воздействия первого цикла, то при правильной настройке длительности импульсов, пауз и коэффициента компенсации перерегулирования последующий цикл приводит регулирующий ор ган в оптимальное положение. При пос туплении новых возмущений на вход объекта регулирования процесс регулирования повторяется аналогично. Если сигнал об отклонении регулируемого параметра появляется на втором входе логического блока 1, то цикл регулирования начинается с воздействия на исполнительный механизм через усилитель 5, а заканчивается компенсирующим перерегулирование воздействием через усилитель 4. Расширение функциональных возможностей регулятора достигается за счет того, что он кроме выходов с импульсными сигналами для управления реверсивным исполнительньом механизмом регулирующего устройства имеет выход с аналоговым сигналом. Сигнал этот является выходным сигналом цифро-аналогового преобразователя 10, вход которого соединен с выходом реверсивного счетчика 31. При наличии сигнала на втором выходе логического блока 1, а следовательн и на первых входах интегратора 9 и элемента И 29 (прямой ход исполнительного механизма), тактовые импульсы с второго выхода генератора б поступают через третий вход интегратора 9 и второй вход элемента И 29 н первый счетный вход счетчика 31. При наличии сигнала на третьем выходе ло гического блока 1, а следовательно, и на втором входе интегратора 9 и на первом входе-элемента И 30 (обра ный ход исполнительного механизма), тактовые импульсы поступают через второй вход элемента И 30 на второй счетный вход счетчика 31. Алгебраическая сумма тактов в прямых и реверсивных сигналах регулятора преоб разуется цифро-аналоговым преобразо вателем 10 в унифицированный аналоговый выходной сигнал, который может быть использован для управления неэлектрическими исполнительныг-ш механизмами через соответствующие преобразователи, например, пневматическими, через электропневмопреобразователь, а также может служить информацией о положении регулирующего органа. Предлагаемым регулятором, в случае его применения, повышается качество регулирования межфазного уровня в сепарационных установках при возмущениях различной амплитуды, так как величина корректирующего регулирующего воздействия пропорциональна амплитуде возмущения, в связи с чем повышается общая производительность этих установок, а также улучшается качество подготавливаемой нефти ,и воды, что позволяет получить определенный технико-экономический эффект. Кроме того, универсальность регулятора при использовании как с электрическими, так и с пневматическими исполнительными механизмами позволяет расширить область его применения. Формула изобретения 1.Импульсный регулятор, содержащий логический блок, входы которого подключены к соответствующим входам регулятора, генератор импульсов, первый и второй усилители, выходы которых подключены соответственно к первому и второму выходам регулятора, отличающийся тем, что, с целью повышения качества регулирования и расширения области применения, в него введены первый и второй элементы И, триггер, блок формирования длительности и последовательно соединенные интегратор и цифро-аналоговый преобразователь,выход которого подключен к третьему выходу регулятора, первый выход логического блока соединен с первыми входами генератора импульсов, триггера и блока формирования длительности, второй выход - с первыми входами первого элемента И и интегратора, третий выход - с первым входом второго элемента И и с вторым входом интегратора, третий .вход которого подключен к первому выходу генератора импульсов и к второму входу блока формирования длительности, выходом соединенного с вторым входом триггера, а третьим входом - с вторым выходом генератора импульсов, третий выход которого подключен к вторым входам первого и второго элементов И, выходы которых соединены соответственно с входами первого и второго усилителей, а второй вход генератора импульсов подключен к выходу триггера. 2,Регулятора по п.1, о т л и чающийся тем, что логический блок содержит третий и четвертый элементы Н,.выходы которых соединены соответственно с первыми входами первого и второго элементов ИЛИ, вторые входы которых подключены соответственно к выходам пятого и шестого элементов И, причем первый вход логического блока соединен с первьми входами третьего элемента И, второго триггера, третьего элемента ИЛИ, выходом соединенного с первым выходом блока и через первый элемент НЕ с (Первым входом четвертого элемента И, а вл:орой вход блока - с -вторыми входа ми третьего элемента ИЛИ и второго триггера,с первым входом шестого элемента И и через второй элемент НЕ - с первым входом пя-, того элемента И, первый вход второго триггера подключен к вторым входам третьего и четвертого элементов И, второй выход - к вторым входам пятого и шестого элементов И, а выходы первого и второго элементов ИЛИ соединены соответственно с вторым и треть им выходами блока. 3. Регулятор ПОП.1, отлича ющийся тем, что генератор импульсов содержит последовательно сое диненные задающий генератор, седьмой элемент И и восьмой элемент И, выход которого подключен к первому выходу генератора, а второй вход - к третье му выходу генератора и к выходу форм рователя импульсов, первый вход кото рого соединен с первым входом генератора, а второй вход - с выходом седьмого элемента И и с вторым выходом генератора, второй вход которо го подключен к второму входу се,цьмого элемента И. 4.Регулятор по п.1, отличающи и с я тем, что блок формирования длительности содержит последовательно соединенные третий элемент НЕ, девятый элемент И и первый счетчик импульсЬв, выход которого подключен к -выходу блока, а второй вход - к выходу десятого элемента И, первый вход которого соединен с вторым входом блока, а второй вход - с входом третьего элемента НЕ и с первым входом блока, причем второй вход девятого элемента И подключен к третьему входу блока. 5.Регулятор по п.1, отличающийся тем, что интегратор содержит одиннадцатый и двенадцатый элементы И, первые входы которых соединены соответственно с первым и вторым входами интегратора, вторые входы - с третьим входом интегратора, а выходы - с первым и вторым входами второго счетчика импульсов, выход которого подключен к выходу интегратора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 408271, кл. G 05 В 11/28, 1971, 2.Авторское свидетельство СССР № 570028, кл. G 05 В 11/28, 1975.

Токт инп.

инпулы

Bbnofff

1ПОПГ

ппп

1

йьподг

&ьподЪ

Авторы

Даты

1982-07-30—Публикация

1980-10-20—Подача