Изобретение относится к цифровой вычислительной технике и может быть использовано для вычисления функции

, а также для получения квадратичных характеристик числовых последовательностей, необходимых при статистической обработке данных.

Известно цифровое устройство для решения уравнений вида z y содержащее регистр, блок управления, элементы И 1 .

Недостатком его является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для вычисления функции

,- JT -.2

вида у(п) содержащее .регистр числа,блок управления, блоки коммутации, сумматор, регистры результата промежуточного результата, суммы 2.

Недостатком известного устройства является невысокое быстродействие.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в устройство для вычисления

X

функции вида .Z -i , содержащее регистр

1 г

исходного числа, выходом подключенный к входу регистра коммутации, выход которого соединен с входом регистра преобразования, блок управления, введены триггер управления инвертированием, элементы И, ИЛИ, сумматор по модулю два, элемент запрета, причем i-й разряд регистра (i Ifx) преобразования содержит триггер,

10 сумматор по модулю два, элементы И, ИЛИ, при этом выход триггера соединен с первым входом первого элемента И, второй вход которого подключен к выходу сумматора по модулю два и

15 первому входу второго элемента И, а выход - к входу элемента ИЛИ, второй вход которого подключен к выходу элемента ИЛИ (i-l)-ro разряда регистра преобразования и первому входу сум20матора по модулю два, второй вход которого и второй вход третьего элемента И соединены с выходом элемента И i-ro разряда регистра коммутации, второй вход второго элемента И

25 i-ro разряда регистра преобразования соединен с выходом первого управляющего элемента И устройства и со счетным входом триггера i-ro разряду регистра исходного числа, выход

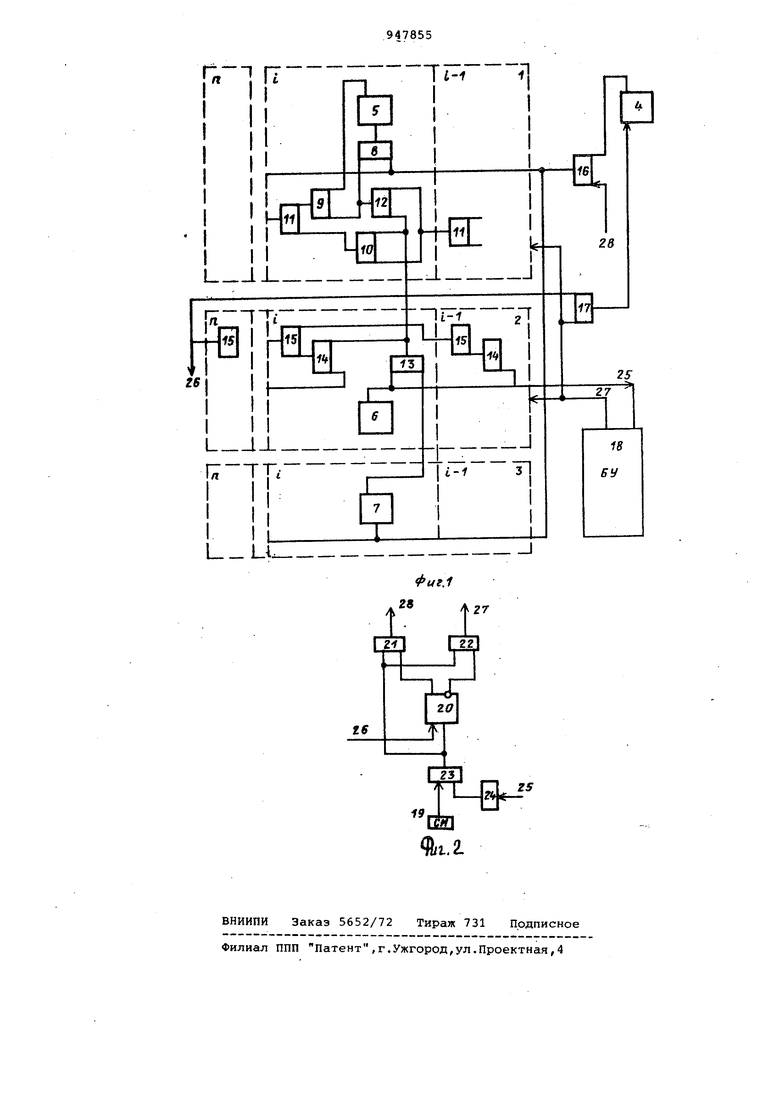

30 второго элемента И i-ro разряда регистра преобразования соединен со счетным входом триггера i-ro разряда регистра преобразования в i-м разряде регистра коммутации, выход элемен та запрета соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента ИЛИ (iго разряда регистракоммутации, первый вход элемента И i-ro разряда регистра коммутации соединен с выходом триггера i-ro разряда регистра коммутации, подключенного к первому входу блока управления, и с входом элемента запрета (i-l)-ro разряда регистра коммутации, второй вход эле мента И 1-го разряда регистра комК1утации соединен с выходом триггера i-ro разряда регистра исходного числа, выход элемента ИЛИ п-го разряда регистра коммутации соединен с вторым входом блока управления и с первьал входом второго управляющего элемента И, второй вход которого соединен с первым выходом блока управления, а выход - с входом триггера управления инвертированием, выход которого подключен к первому входу первого управляющего элемента И, вто рой вход которого подключен к втором выходу блока управления устройства. Кроме того, блок управления содержит элементы И, ИЛИ, триггер, генератор импульсов, причем выход генератора импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходом элемента ИЛИ, входы которого соединены с первым входом блока управления, выход первого элемента И подключен к первым входам второго и третьего элементов Инк счетному входу триггера, вход которого подключен к второму входу блока управления, прямой и инверсный выходы триггера соединены с вторыми входами соответственно второго и Третьего элементов И, выходы которых лсляются соответственно вторым и первым выходами блока. На фиг.1 представлена схема вычи ления функции; на фиг.2 - вариант вы полнения блока управления. Схема (фиг.1) содержит регистр 1 преобразователя, регистр 2 коммутации, регистр 3 исходного числа, три гер 4 управления инвертированием, триггеры 5-7, элементы И 8-10, элементы ИЛИ 11, сумматор 12 по модулю два, элемент И 13, элементы 14 запр та, элементы ИЛИ 15, управляющие эле менты И 16 и 17; блок 18 управления (фиг.2) содержит генератор 19 импул сов, триггер 20, элементы И 21-23, элемент ИЛИ 24, входы 25 и 26, выхо ды 27 и 28. Устройство работает следующим об разом. В исходном состоянии содержимое i триггера управления О, в регистре 1 - нули, в регистре 2 - едир1ицы, а в регистре 3 - исходное число. Поэтому на выходе элемента И 15 п-го разряда регистра 2 состояние п-го разряда регистра 3 и все разряды исходного числа подключены к регистру 1. В первом цикле работы устройства из устройства управления на выход 27 выдается сигнал сдвига. По этому сигналу происходит правый сдвиг содержимого регистра 2, при этом состояние регистра преобразуется к виду 0111...1, и левый сдвиг содержимого регистра 1. В регистре 1 остаются нули, а в триггер управления инвертированием переписывается содержимое п-го разряда регистра 3 исходного кода. В результате правого сдвига срдержимого регистра 2 происходит отключение переменной п-го разряда от соответствующего входа регистра 1. На выходе элемента ИЛИ 15 п-го разряда регистра 2 появляется переменная п-1 разряда регистра 3. В регистре 1 происходит срабатывание комбинационной логики и на соответствующих входах элементов И 8 формируются условия инвертирования разрядов этого регистра. Затем устройство управления на выход 28 инвертирования выдает сигнал инвертирования и в зависимости от состояния триггера 4 управления и условий инвертирования в разрядах происходит инвертирование содержимых разрядов регистра 1 и разрядов регистра 3. В cлeдyющe t цикле работы устройства путем подачи сигнала на выход 27 сдвига осуществляется сдвиг содержимого регистра 1 влево, а регистра 2 вправо на один разряд. При этом в регистр 1 сдвигается прежнее содержимое триггера 4 управления, в котбрый записывается новое содержимое, состояние п-1 переменной регистра 3. В регистре 2 образуется код 00111... 1. Таким образом, происходит отключение п и п-1 переменных от соответствующих входов регистра 1, а на выходе элемента ИЛИ 15 п-го разряда регистра 2 формируется значение п-2 переменной регистра 3, которое в следующем цикле переписывается в триггер 4 управления. После подачи сигнала сдвига устройство управления выдает сигнал инвертирования на вход 28 и происходит инверсия в соответствующих разрядах. Таким образом, в результате п циклов работы устройства в регистре 1 формируется результат вычисления 51 л Предлагаемое устройство является более быстродействующим имеет меньшее количество аппаратуры по сравнению с извес ными схемами. Формула изобретения 1. Устройство для вычисления функции .2 i , содержащее регистр исходного числа, выходом подключенный к входу регистра коммутации, выход которого соединен с входом регистра преобразования, блок управления, отличающееся тем, что, с целью повышения быстродействия и сокращения аппаратуры, в него введены триггер управления инвертированием, элементы И, ИЛИ, сумматор по модулю два, элемент запрета, причем i-й разряд регистра ( т х) преобразования содержит триггер, сумматор по модулю два, элементы И, ИЛИ, при этом выход триггера соединен с первым входом первого элемента И, второй вход которого подключен к выходу сумматора по модулю два и первому входу второго элемента И, а выход - к входу элемента ИЛИ, второй вход которого соединен с выходом Тре тьего элемента И, первый вход которого подключен к выходу элемента ИЛИ (i-l)-ro разряда регистра преобразования и первому входу сумматора по модулю два, второй вход которого и второй вход третьего элемента И соединены с выходом элемента И i-rq раз ряда регистра коммутации и с прямым входом элемента запрета i.-ro разряда регистра коммутощии, второй вход вто рого элемента И i-ro разряда регистра преобразования соединен с выходом первого управляющего элемента И устройства и со счетным входом триггера i-ro разряда регистра исходного числа, выход второго элемента И i-r разряда регистра преобразования соединен со счетным входом триггера i-ro разряда регистра преобразования в i-M разряде регистра коммутации, выход элемента запрета соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом эле мента ИЛИ (i-l)-ro разряда регистра коммутации, первый вход элемента И i-ro разряда регистра коммутации соединен с выходом триггера i-ro разряда регистра коммутации, подключенного к первому входу блока управления, и с входом элемента запрета (i-l)-ro разряда регистра коммутации, второй вход элемента И i-ro разряда регистра коммутации соединен с выходом триггера i-ro разряда регистра исходного числа, выход элемента ИЛИ п-го разряда регистра коммутации соединен с вторым входом блока управления и с первым входом второго управляющего элемента И, второй вход которого соединен с первым выходом блока управления, а выход - с входом триггера управления инвертированием, выход которого подключен к первому входу первого управляющего элемента И, второй вход которого подключен к второму выходу блока управления устройства. 2. Устройство ПОП.1, отличающееся тем, что блок управления содержит элементы И, ИЛИ, триггер, генератор импульсов, причем выход генератора импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходом элемента ИЛИ, входы которого соединены с первым входом блока управления, выход первого элемента И подключен к первым входам второго .и третьего элементов И и к счетному входу тригге- ра, вход которого подключен к второму входу блока управления, прямой и инверсный выходы триггера соединены с вторыми входами соответственно второго и третьего элементов И, выходы которых являются соответственно вторым и первым выходами блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 453697, кл.С 06 F 7/38, 1972. 2.Авторское свидетельство СССР № 765803, кл.С 06 F 7/38, 1978 (прототип).

Г (Т

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат | 1983 |

|

SU1151956A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Система коммутации | 1986 |

|

SU1403071A1 |

| Многофункциональный анализатор случайных процессов | 1986 |

|

SU1399766A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Генератор случайных чисел | 1984 |

|

SU1310813A1 |

| Устройство для формирования тригонометрических коэффициентов быстрого преобразования Фурье | 1981 |

|

SU1005071A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для моделирования систем массового обслуживания | 1982 |

|

SU1067508A1 |

Авторы

Даты

1982-07-30—Публикация

1979-09-03—Подача