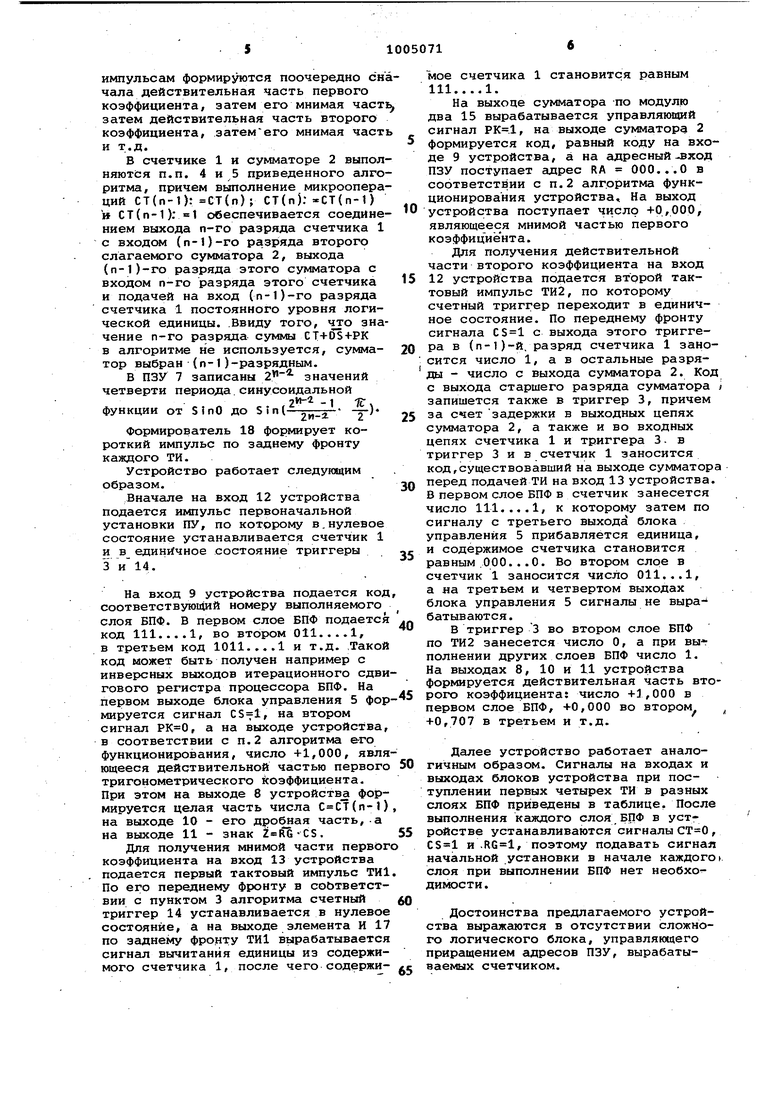

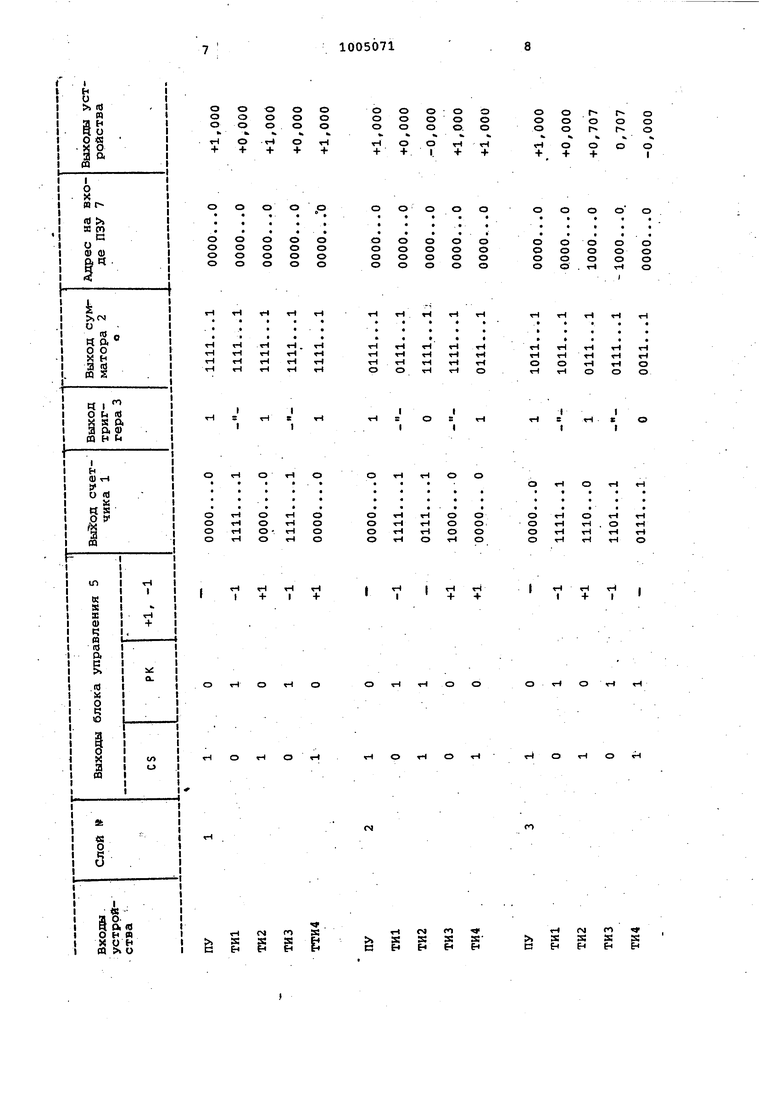

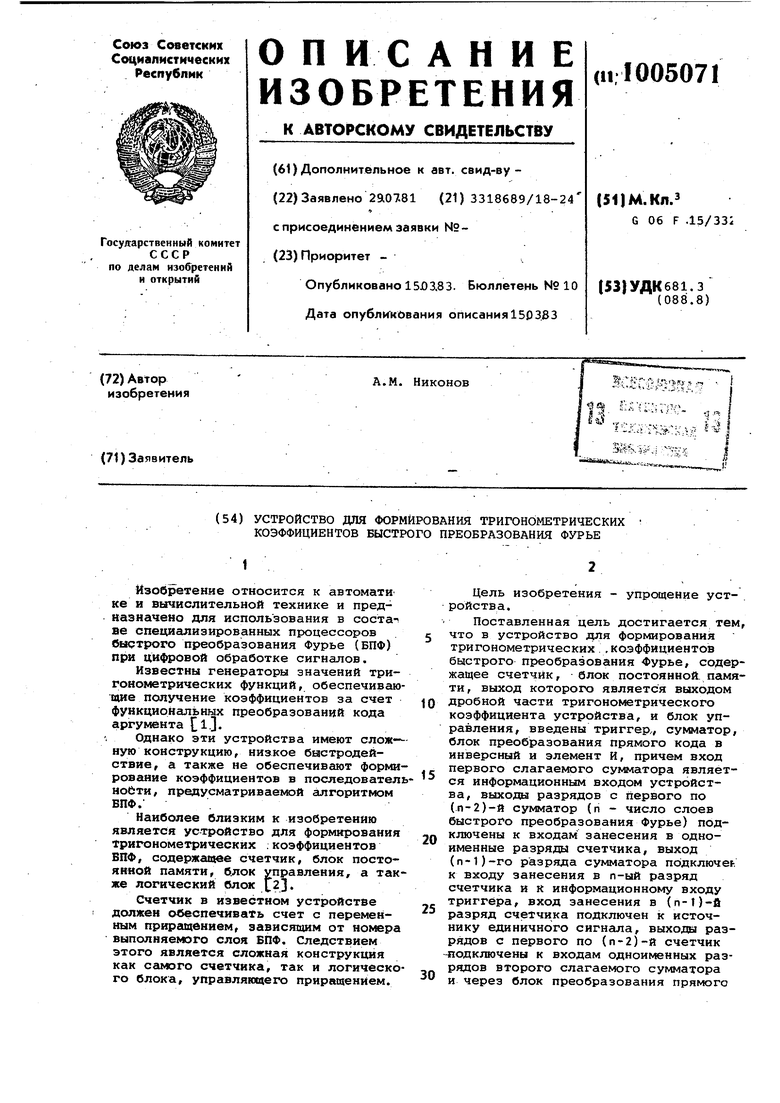

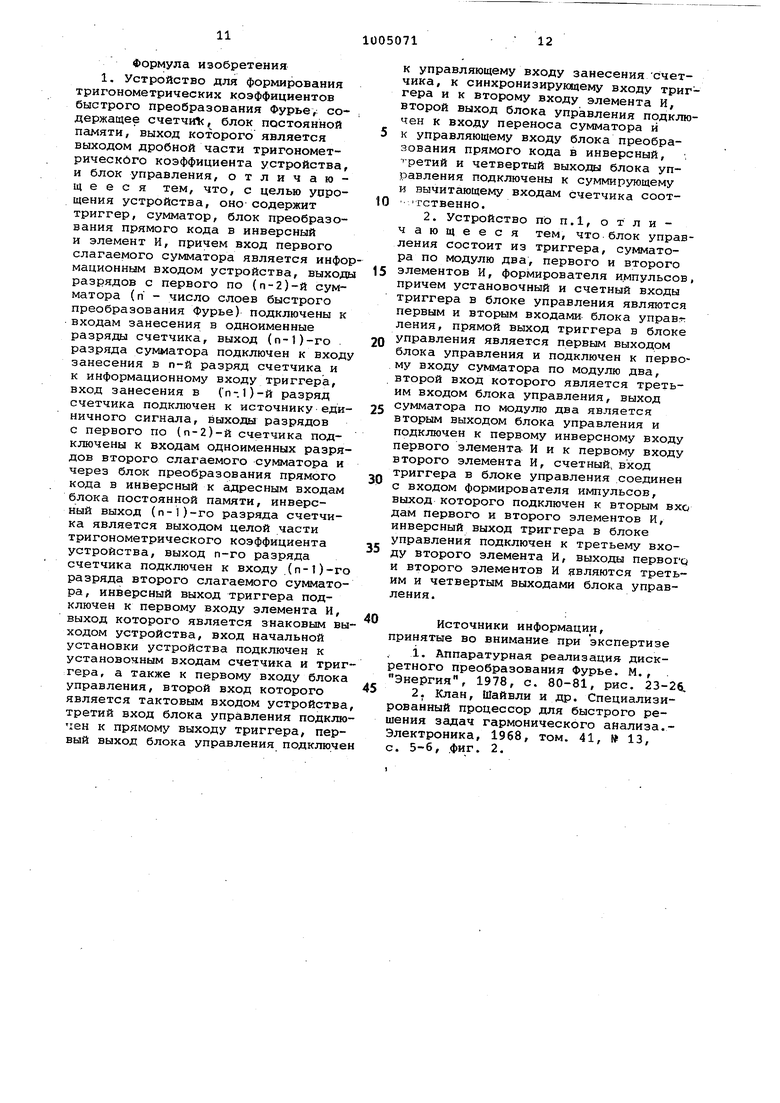

кода в инверсный к адресным входам блока постояннойпамяти, инверсный выход (n-l)-ro разряда счетчика является выходом целой части тригонометрического коэффициента устройства выход п-го раэряща счетчика подключен к входу (n-l)-ro разряда второго слагаемого сумматора, ийверсный выход триггера подключен, к первому входу элемента И, выход которого является знаковым выходом устройства, вход начальной установки устройства подключен к установоч ным входам счетчика и триггера, а также к первому входу блока управле ния, второй вход которого является тактовым входом устройства, третий вход блока управления подключен к прямому выходу триггера, первый выход управления подключен к управляющему входу занесения счетчика, к синхронизирующему входу три гера и к второму входу элемента И, второй выход блока управления подключен к входу переноса сумматора и к управляющему входу блока преобразования прямого кода в инверсный, третий и четвертый выходы блока управления подключены к суммируквдему и вычитающему входам счетчика соответственно, кроме того,блок управления состоит из триггера, сумматор по модулю два, первого и второго элементов И, формирователя импульсов причем установочный и счетный входы триггера в блоке управления являются первым и йторым Входами блока уп равления, прямой выход триггера в блоке управления является первым : выходом блока управления и подключе к первому- входу сумматора по модулю два, второй вход которого является третьим входом блока управления, выход сумматора по модулю два является вторым выходом блока управления и подключен к первому инверсному, входу первого элемента И и к пер вому входу второго элемента И, счет ный вход триггера в блоке управлени соединен с входом формирователя импульсов, выход которого подключен к вторым входам первого и второго эле ментов И,инверсный выход триггера в блоке управления подключен к трет ему входу второго элемента И, выход первого и второго элементов И являются третьим и четвертым выходами блока управления. На чертеже представлена функциональная схема устройства для формир .вания тригонометрических коэффициентов быстрого преобразования Фурье Устройство содержит п-разрядный счетчик 1, (п-1)-разрядный сумматор триггер 3, элемент И 4, блок управления 5, блок 6 преобразования прямого кода в инверсный,блок 7 пос Гоянной памяти, выход 8 целой части тригонометрического коэффициента, информационный вход 9, выход 10 робной части тригонометрического коэффициента, знаковый выход 11, вход 12 начальной установки,тактовый вход 13. Блок 5-управления состоит из триггера 14, сумматора по модулю два 15, элементов И 16 и 17, формирователя импульсов 18. В предлагаемом устройстве формирование тригонометрических коэффициентов осуществляется в следующей последовательности . 1.Производится первоначальная установка устройства: триггера 3 (), счетчика (), триггера 14 (). 2.Формируется очередной результат (действительная или мнимая часть очередного коэффициента) : знак результата; Z RG-CS ; целая часть (п-1); дробная часть считывается из ПЗУ по адресу СТ,если ... СТ ,если . Далее по тактовому импульсу (ТИ) подготавливается формирование следующего результата: 3.CS С1. 4.Если , то: CT(n-l):-СТ(п) CT: CT+OS- -PK (n-l) CT(n)(n-1) CT(n-1) 5.(CT+1, если CT: jCT-1, если PK-CS 1 ICT - в остальных случаях. 6.Переход к пункту 2, где СТ - содержимое п-разрядного счетчика; СТ(1) - содержимое i-ro разряда « счетчика; СТ(СТ)А imod - содержимое п-2 младщих разрядов счетчика; СТ - обратный код от СТ ; + - операция сложения по модулю два; CS - сигнал на первом выходе блока управления; единичное значение сигнала CS означает формирование действительной части коэффициента;PK RG+CS - сигнал на втором выходе блока управления, рзнача ет прямой код адреса ПЗУ; DS - код, соответствующий номеру выполняемого слоя БПФ. На выходе устройства после его первоначальной установки по тактовым импульсам формируются поочередно сн чала действительная часть первого коэффициента, затем его мнимая част затем действительная часть второго коэффициента, затемего мнимая част и т.д. в счетчике 1 и сумматоре 2 выпол няются п.п. 4 и 5 приведенного алго ритма, причем выполнение микроопера ций СТ(п-1)); СТ(п);.СТ(п-1) СТ(п-1): 1 обеспечивается соедине нием выхода п-го разряда счетчика 1 с входе (n-l)-ro разряда второго слагаемого сумматора 2, выхода (n-l)-ro разряда этого сумматора с входом п-го разряда этого счетчика и подачей на вход (n-l)-ro разряда счетчика 1 постоянного уровня логической единицы. .Ввиду того, что значение п-го разряда суммы CT+DS+PK в алгоритме не используется, сумматор выбран (п-1)-разрядным. В ПЗУ 7 записаны 2 значений четверти периода синусоидальной 7И-2 i -jfфункции от SInO до Sin( --} Формирователь 18 формирует короткий импульс по заднему фронту каждого ТИ. Устройство работает следующим образом. Вначале на вход 12 устройства подается импульс первоначальной установки ПУ, по которому в.нулевое состояние устанавливается счетчик 1 и в единичное состояние триггеры 3 и14. На вход 9 устройства подается код соответствуювшй номеру выполняемого слоя ВПФ. В первом слое БПФ подается код 111....1, во втором 011....1, в третьем код 1011....1 и т.д. .Такой код может быть получен например с инверсных выходов итерационного сдви гового регистра процессора ВПФ. На первом выходе блока управления 5 фор мируется сигнал , на втором сигнал , а на выходе устройства, в соответствии с п. 2 алгоритма е-го функционирования, число +1,000, явля ющееся действительной частью первого тригонометрического коэффициента. При этом на выходе 8 устройству формируется целая часть числа (п-1) на выходе 10 - его дробная часть,-а на выходе 11 - знак Z RG-CS. Для получения мнимой части первог коэффициента на вход 13 устройства подается первый тактовый импульс ТИ1 По его переднему фронту в соЬтветствии с пунктом 3 алгоритма счетный триггер 14 устанавливается в нулевое состояние, а на выходе элемента И 17 по заднему фронту ТИ1 вырабатывается сигнал вычитания единицы из содержимого счетчика 1, после чего содержимое счетчика 1 становится равным 1111. На выходе сумматора по модулю два 15 вырабатывается управляющий сигнал РК.1, на выходе сумматора 2 формируется код, равный коду на входе 9 устройства, а на адресный-вход ПЗУ поступает адрес RA 000...О в соответствии с п.2 алгоритма функционирования устройства На выход устройства поступает число +0,000, являющееся мнимой частью первого коэффициёнта. Для получения действительной части второго коэффициента на вход 12 устройства подается второй тактовый импульс ТИ2, по которому счетный триггер переходит в единичное состояние. По переднему фронту сигнала С с выхода этого триггера в (п-1)-и. разряд счетчика 1 заносится число 1, а в остальные разряды - число с выхода сумматора 2. Код с выхода старшего разряда сумматора i запишется также в триггер 3, причем за счет задержки в выходных цепях сумматора 2, а также и во входных цепях счетчика 1 и триггера 3. в триггер 3 и в счетчик 1 заносится код,существовавший на выходе сумматора перед подачей ТИ на вход 13 устройства. В первом слое ВПФ в счетчик занесется число 111....1, к которому затем по сигналу с третьего выхода блока управления 5 прибавляется единица, и содержимое счетчика становится равным 000...0. Во втором слое в счетчик 1 заносится число 011...1, а на третьем и четвертом выходах блока управления 5 сигналы не вырабатываются. В триггер 3 во втором слое ВПФ по ТИ2 занесется число О, а при вы полнении других слоев ВПФ число 1. На выходах 8, 10 и 11 устройства формируется действительная часть второго коэффициента: число +1,000 в первом слое ВПФ, +0,000 во втором +0,707 в третьем и т.д. Далее устройство работает аналогичным образом. Сигналы на входах и выходах блоков устройства при поступлении первых четырех ТИ в разных слоях ВПФ приведены в таблице. После выполнения каждого слоя ВР в устрсЛстве устанавливаются сигналы , и ., поэтому подавать сигнал начальной установки в начале каждого слоя при выполнении ВПФ нет необхо димости. Достоинства предлагаемого устройства выражаются в отсутствии сложного логического блока, управляющего приращением адресов ПЗУ, вырабатываемых счетчиком.

о о о

г о

г- о г

о о о

f-

о

о I

+

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрого преобразования Фурье при многоканальной обработке информации | 1983 |

|

SU1124324A1 |

| Формирователь линейно-частотно-модулированных сигналов | 1987 |

|

SU1584070A1 |

| Устройство для измерения параметров магнитных лент | 1986 |

|

SU1434376A1 |

| Устройство для формирования тригонометрических коэффициентов быстрого преобразования Фурье | 1985 |

|

SU1297072A1 |

| Устройство для формирования адресов процессора усеченного быстрого преобразования Фурье | 1984 |

|

SU1278883A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Цифровой фильтр | 1988 |

|

SU1566469A1 |

| Устройство для спектральногоАНАлизА | 1978 |

|

SU813286A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1982 |

|

SU1056207A1 |

оо

о о о

о о о о

оо

оо

о. тН

tH r-l

о тН тН о о

тН

о о

г-1

о гЧ

гЧ

гН гЧ

о

н I

.н I

го

г-1

гч S

S EH

S EH

н

т г

см о%

о о о со о го 1

о +

о

о

о

+

+

+

о о о

о о

о о

о о о о

тЧ

тН

гЧ

о

тН

о о

о

О О

н

гИ

гЧ

о о

тН

гЧ

о н

m Р

сч

S Ь

g

Формула изобретения 1. Устройство для формирования тригонометрических коэффициентов быстрого преобразования Фурье/ со- , держащее счетчи1, блок постоянной памяти, выход которого является выходом дробной части тригонометрического коэффициента устройства, и блок управления, отличающееся тем, что, с целью упрощения устройства, оно содержит триггер, сумматор, блок преобразования прямого кода в инверсный и элемент И, причем вход первого слагаемого сумматора является информационным входом устройства, выхо,цы разрядов с первого по {п-2)-й сумматора (п - число слоев быстрого преобразования Фурье) подключены к входам занесения в одноименные разряды счетчика, выход (n-l)-ro . разряда сумматора подключен к входу занесения в п-й разряд счетчика и к информационному входу триггера, вход занесения в (п-1)-й разряд счетчика подключен к источнику единичного сигнала, выходы разрядов с первого по (п-2)-й счетчика подключены к входам одноименных разрядов второго слагаемого сумматора и через блок преобразования прямого кода в инверсный к адресным входам блока постоянной памяти, инверсный выход (n-I)-ro разряда счетчика является выходом целой части тригонометрического коэффициента устройства, выход п-го разряда счетчика подключен к входу (п-1)-го разряда второго слагаемого сумматора, инверсный выход триггера подключен к первому входу элемента И, выход которого является знаковым выходом устройства, вход начальной установки устройства подключен к установочным входам счетчика и триггера, а также к первому входу блока управления, второй вход которого является тактовым входом устройства третий вход блока управления подключен к прямому выходу триггера, первый выход блока управления подключе

к управляющему входу занесения/счетчика, к синхронизирующему входу триггера и к второму входу элемента И, второй выход блока управления подключен к входу переноса сумматора и к управляющему входу блока преобразования прямого кода в инверсный, третий и четвертый выходы блока управления подключены к суммирующему и вычитающему входам счетчика соот тственно.

Источники информации, принятые во внимание при экспертизе

с. 5-6, ,фиг. 2.

W

Авторы

Даты

1983-03-15—Публикация

1981-07-29—Подача