Изобретение относится к электроизмерительной технике и может быть использовано при создании устройств для контроля параметров электронных -схем, включая полупроводниковые и гибридные интегральные схемы.

Известно устройство для автоматического контроля параметров электронных схем, содержащее управляющую вычислительную машину, устройство согласования, измерительные блоки, коммутационную матрицу и рабочие посты для подключения объектов контроля .Недостатком этого устройства являются ограниченные функциональные возможности вследствие ограниченного объема памяти запоминающих устройств.

Наиболее близким к изобретению по технической сущности является устройство, содержащее m контрольных установок и п вычислительных машин,.соединенных посредством В адресных н k информационных шин через коммутатор, включающий m-n(k+ Е) ключей, управляющие входы которых соединены с соответствующими выходами первой группы блока сканирования, выходы второй группы которого соединены с .соответствующими входами второй группы п-разрядного сдвигающего регистра,

лоды первой группы которого соединены с соответствующими выходами вычислительных машин, т-разрядный сдвигающий регистр, входы первой группы которого соединены с выходами -соответствующих контрольных установок, а входы второй группы - с соответствующими выходами третьей группы блока сканирования, выходам четвертой груп10пы которого соединены с соответствующими входами блока прерывания программ, выходы которого соединены с : входами соответствую1:9их вычислительных машин, регистры признаков, входы

15 и выходы -которых соединены с соответствующими информационными щинами, и дешифраторы, входы которых соединены о соответствующими адресными шина - ми, а выходы г с входами сс ответствующих регистров признаков ГЗЗНедостатками известного устройства являются низкая точность контроля и ограниченные функциональные возможности .

25

Цель изобретения - повышение точности и расширение функциональных возможностей контроля.

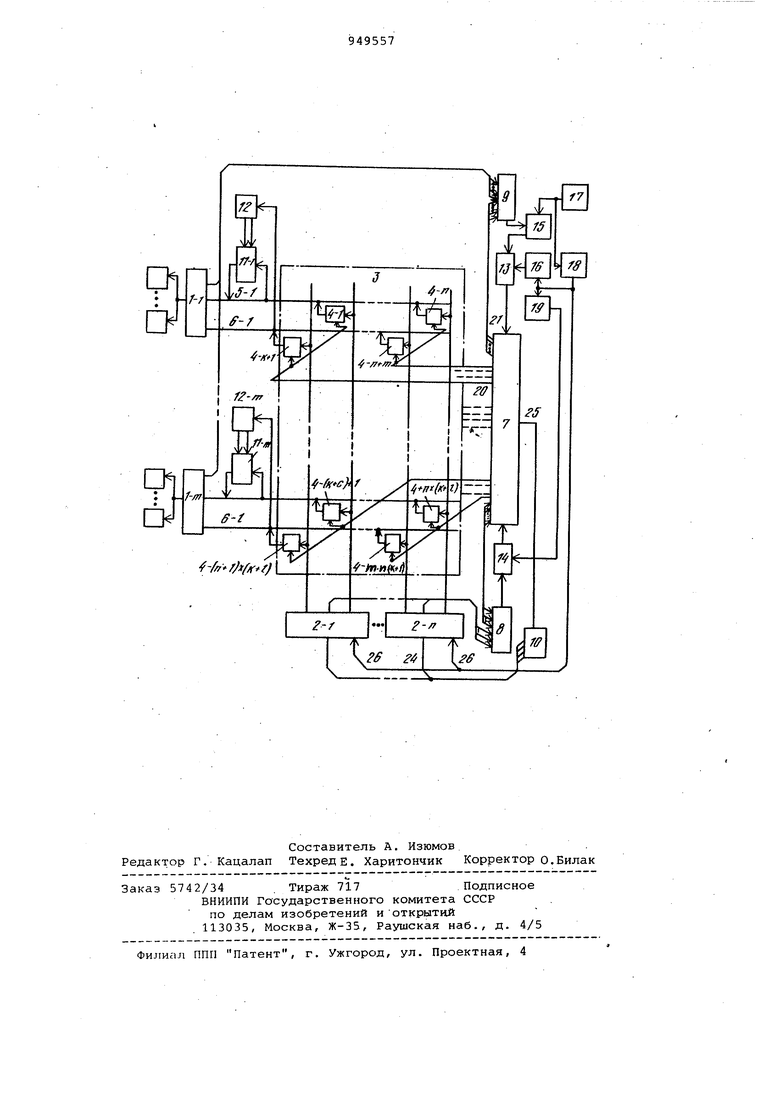

Для достижения этой цели устройство для контроля электрических па30раметров электронных схем, содержащее m контрольных установок и п вычислительных машин, соединенных посредством Е адресных и k информационных шин через коммутатор, включающий m.n(k+ F) ключей, управляющие входы которых соединены с соответствующими выходами первой группы блока сканирования, выходы второй группы которого соединены с соответствующими входами второй группы п-разрядног сдвигающего регистра, входы первой группы которого соединены с соответствующими выходами вычислительной машины, т-разрядный: сдвигающий ре гистр, входы первой группы которого соединены с выходами соответствующих контрольных установок, а входы второй группы - с соответствующими выходами третьей группы блока сканирования, выход четвертой группы которо го соединены с соответствующими входами блока прерывания программ, выходы которого соединены с входами со ответствующих вычислительных машин регистры признаков, входы и выходы которых соединены с соответствующими информационными шинами, и дешифраторы, входы которых соединены с соответствующими адресными шинами, а выходы - с входами соответствующих регистров признаков, снабжено двумя ло .гическими умножителями, сдвиговым ре гистром, генератором тактовых импуль сов, счетчиком, управляющим вычислительным блоком и преобразователем кодов, при этом входы первого логического умножителя соединены с выхо дами соответственно преобразователя кодов и сдвигового регистра, входы которого соединены с выходами соответственно генератора тактовых импульсов и т-разрядного сдвигающего регистра, входы второго логического умножителя соединены с выходами соот ветственно п-разрядного сдвигающего регистра и управляющего вычислительного блока, выходы логических умножи телей соединены с соответствующими входами блока сканирования, вход счетчика соединен с выходом генера- тора тактовых импульсов,а его выходы - соответственно с входами управляющего вычислительного блока,.преобразователя кодов, и вычислительных машин. На чертеже представлена структурная электрическая схема устройства. Устройство m контрольных установок (1-.1) - (1-т) , п вычисленных машин (2-1)-(2-п), коммутатор 3, включающий m-n/k-f Е) ключей (4-1)-, (4-т .п -(k + I) , Е адресных шин (5i) (5-E),k информационных шин (6-1)(6-k), блок 7 сканирования, п-разряд ный сдвигающий регистр 8, т-разрядны сдвигающий регистр 9, блок 10 прерывания программ, регистры (11-1)(11-т) приянаков, дешифраторы (12-1) (12-т), логические умножители 13 и 14, сдвиговый регистр 15, преобразователь 16 кодов, генератор 17 тактовых импульсов, счетчик 18 и управляющий вычислительный блок 19. Устройство работает следующим образом. Пусть в исходном состоянии в запоминающие устройства вычислительных машин (2-1) - (2-п) записана программа работы, содержащая программы контроля изделий, причем число программных единиц, записанных в запоминающие устройства, может быть неодинаково у различных .вычислительных машин и ни одна из вычислительных машин не подключена к соответствующим контрольным установкам (1-1) - (1-т) . Регистры 8,9,(ll-l)-(ll-m) и 15 установлены В исходное состояние. Единичное состояние триггеров регистра 9 свидетельствует о наличии свободных контрольных установок (1-1)-(1-т), а ре гистра 8 - свободных для обслужива вычислительных машин (2-l)-{2-n),i В управляющем вычислительном блоке 19 записана информация о том, какие вычислительные машины (2-1)-(2-п) могут .обслуживать каждую из контрольных установок (1-1)-(l-m), Состояние сдвигового регистра 15 копирует в процессе работы состояние т-разрядного регистра 9, Начинает работу генератор 17 тактовых импульсов. Тактовые импульсы поступают на сдвиговый регистр 15, и на его выходе.появляется информация (в виде логического нуля или логической (здиницы) о занятости контрольных установок. Одновременно тактовые импульсы проходят на счетчик 18, на выходах которого формируется код номера контрольной установки (1-1)(1-т), поступающий на преобразователь 16 кода и в управляющий вычислительны блок 19. Преобразователь 16 кода преобразует код номера контрольной установки (1-1)-(1-т) в параллельный позиционный код. В зависимости от кода номера контрольной установки управляющий вычислительный блок 19 формирует п-разрядный управляющий код. В логическом умножителе 14 происходит поразрядное умножение кодов сдвигающего регистра 8 и управляющего вычислительного блока 19. Непрерывно работающий блок 7 сканирования дешифрует коды, поступающие с логических умножителей 13 и 14, и подключает при помощи ключей (4-1)-(4-тП. (kt В)) вычислительные машины (2-1)-(2-п) к данной контрольной установке (1-1)tl-m) и одновременно устанавливает в нулевое состояние регистрь 8 и 9. Сигналы блока 7 сканирования поступают через блок 10 на вход прерывани соответствующей вычислительной машины (2-1)-(2-п). По сигналу прерывания и в соответствии с номером контрольной установки (1-1)-(1-т) вычислительная машина осуществляет ввод программы контроля. Аналогично проис ходит процесс подключения для других вычислительных машин и контрольных установок. После ввода командной и информационной частей программы начинается выполнение программы контроля установками (1-1)-(1-т). По окончании ввода программы контроля вычислитель ные машины (2-1)-(2-п) вьщают сигналы, которые устанавливают регистр 8 в единичное состояние. Кроме того, последняя перед прерыванием команда программы контроля раоиифровывается дешифратором (12-1)-(12-т) и подготавливает к приему регистр (ll-l)-(l-m) признаков. В регистрах (11-1)-(11-т) записывается последнее перед прерыванием информационное слово - относительный (относительно начала программа контроля) адрес ячейки памяти, с которого должно быть продолжено после прерывания дальнейшее выполнение проrpat ®ffit. По окончании выполнения программы контроля установки (l-l)-(l-in) выдарт сигнал окончания работы. Этот сиг нал поступает на регистр 9, устанавливая его в единичное состояние. Подключение освободившейся контрольной установки происходит описанным способом. После подключения и этбй установки к вычислительной машине (2-1)-(2-п) последняя первой командои через дешифратор (12-1)-(12-т) опросит регистр (11-1)-(11-т) призна koB, хранящий относительный адрес, расшифрует его и в зависимости от номера контрольной установки (1-1)(1-т), определит начальный адрес последующей части программы контроля после чего перейдет к ее выполнению. Аналогично работают и остальные контрольнне установки. Формула изобретения Устройство для контроля электрических параметров электронных схем, содержащее т контрольных установок и О вычислительных машин, соединенных посредством Е адресных и Ч информационных шин через коммутатор, включающий т- п{ К +8 ключей, управляющие входы которых соединены с соответствующими выходами первой группы блока сканирования, выходы второй группы которого соединены с соответствующими входами второй группы и -разрядного сдвигающего регистра, входы первой группы которого соединены с соответствующими выходами вычислительных машин, m -разрядный сдвигающий регистр, входы первой группы которого соединены с выходами соответствующих контрольных установок, а входда второй группы - с соответствующими выходами третьей группы блока сканирования, выходы четвертой группы которого соединены с соответствующими входами блока прерывания программ, выходы которого соединены с входами соответствующих вычислительных машин, регистры признаков, входы и выходы ко|торых соединены с соответствующими информационными шинами, и дешифраторы, входы которых соединены с соответствукицими адресными шинами, а выходы - с входами соответствующих регистров признаков, отличающееся тем, что,с целью повышения точности и расширения функцио нальных возможностей контроля, оно снабжено двумя логическими умножителями, сдвиговым регистром, генератором тактовых импульсов, счетчиком, управляющим вычислительным блоком и преобразователем кодов, при этом входы первого логического умножителя соединены с выходами соответственно преобразователя кодов и сдвигового регистра, входы которого соединены с выходами соответственно генератора тактовых импульсов иго-разрядного сдвигающего регистра, входы второго логического умножителя соеДинены с выходами соответственно п -разрядного сдвигающего регистра и управляющего вычислительного блока, выходы логических умножителей соединены с соответствующими входами блока сканирования, вход счетчика соединен с выходом генератора тактовых импульсов, а его выходы - соответственно с входами управляющего вычислительного .блока, преобразователя кодов и вычислительных машин. Источники илформации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 382095, кл. G .01 R 31/28, 1969. 2. Авторское свидетельство СССР №471560, кл. G 01 R31/28, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1474635A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Система для контроля сложных релейных распределителей | 1985 |

|

SU1252780A1 |

| Система для автоматического контроля электрических параметров электронных схем | 1972 |

|

SU471560A1 |

| Система для контроля сложных релейных распределителей | 1987 |

|

SU1522209A2 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Устройство для контроля схем управления | 1984 |

|

SU1252785A1 |

| СИСТЕМА ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2011 |

|

RU2466448C1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

Авторы

Даты

1982-08-07—Публикация

1980-12-30—Подача