(54) ПРИЕМНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для LU-разложения матриц | 1987 |

|

SU1509933A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для согласования потоков телеметрических отсчетов | 1987 |

|

SU1543561A1 |

| Цифровой фильтр | 1986 |

|

SU1437968A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ТЕЛЕГРАФНЫХ РАДИОСИГНАЛОВ | 1990 |

|

RU2009615C1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Счетное устройство | 1986 |

|

SU1368981A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

1

Изобретение относится к технике передачи цифровой информации и может быть использовано для оперативного приема сведений от многих территориально разнесенных корреспондентов в центр сбора, хранения и отображения информации, заданной в цифровой форме, при помощи линий АТС.

Известно, что цифровая информация по линиям АТС обычно передается с помощью устройств, содержащих генераторы тональных частот по количеству каналов и мани- ю пулятор (например, номеронабирательньгй диск). Для адресации передаваемой информации каждое из передающих устройств имеет индивидуальный узел маркерного сигнала, идентифицирующий его место в приемном устройстве. При автоматическом приеме цифровой информации приемное устройство имеет выделить маркерных сигналов, а также блоки автоматического приема информации, выделения каналов и оперативного запоминания 1.20

Недостатком таких систем является необходимость дополнительного оборудования для формирования маркерных сигналов и дешифрации.

Известно приемное устройство с адресацией информационных каналов, содержащее последовательно соединенные управляющий коммутатор и блок выделения каналов, выходы которого подключены к первым входам п элементов И, выходы которых подключены к соответствующим входам блока памяти 2.

Недостаток данного устройства заключается в невысокой достоверности принимаемой информации.

Цель изобретения - повыщение достоверности принимаемой информации.

Указанная цель достигается тем, что в приемное устройство с адресацией информационных каналов, содержащее последовательно соединенные управляющий коммутатор и блок выделения каналов, выходы которого подключены к первым входам п элементов И, выходы которых подключены к соответствующим входам блока памяти, введены п RS-триггеро, дополнительный элемент И и элемент НЕ, при этом выход элемента НЕ подключен к объединенным вторым входам п элементов И, выход «Сброс управляющего коммутатора подключен к

объединенным R-входам RS-триггеров, С-входы которых объединены со входом элемента НЕ и подключены к вьЕходу дополнительного элемента И, ко входам которого под(Счючеяы инверсные выходы RS-триггеров, выходы «Запись которых подключены к информационным входам блока памяти, причем выходы блока выделения каналов подключены к S-входам соответствующих RS-триггеров.

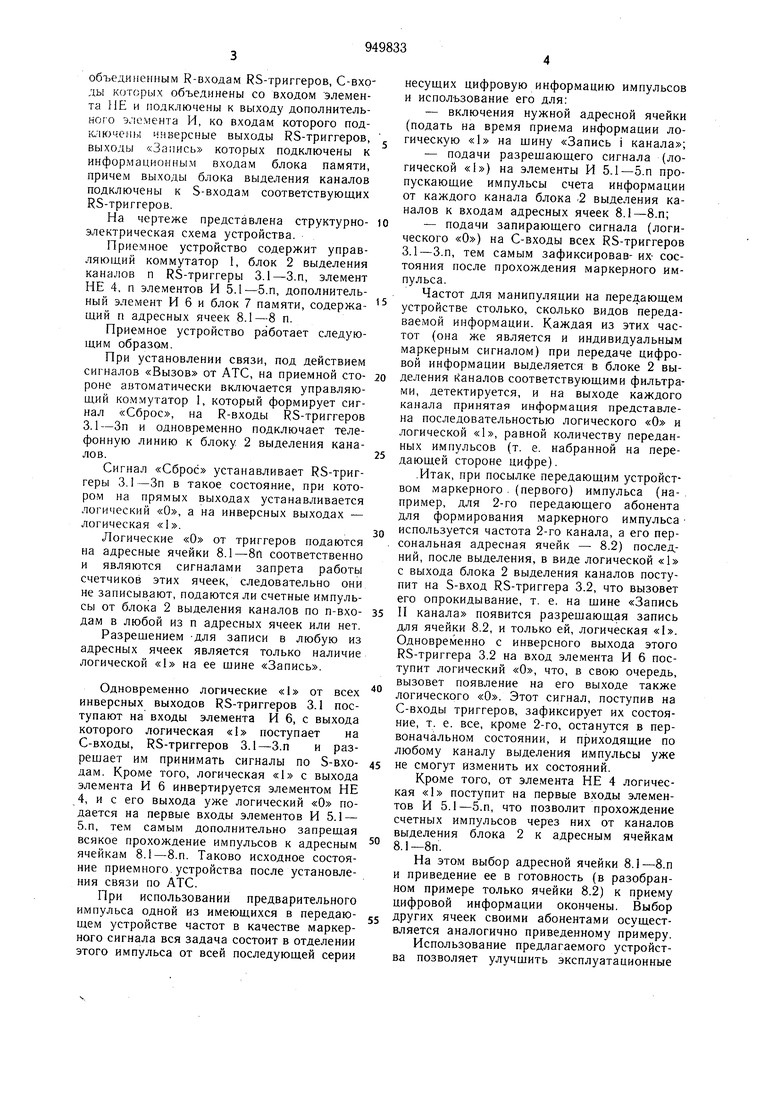

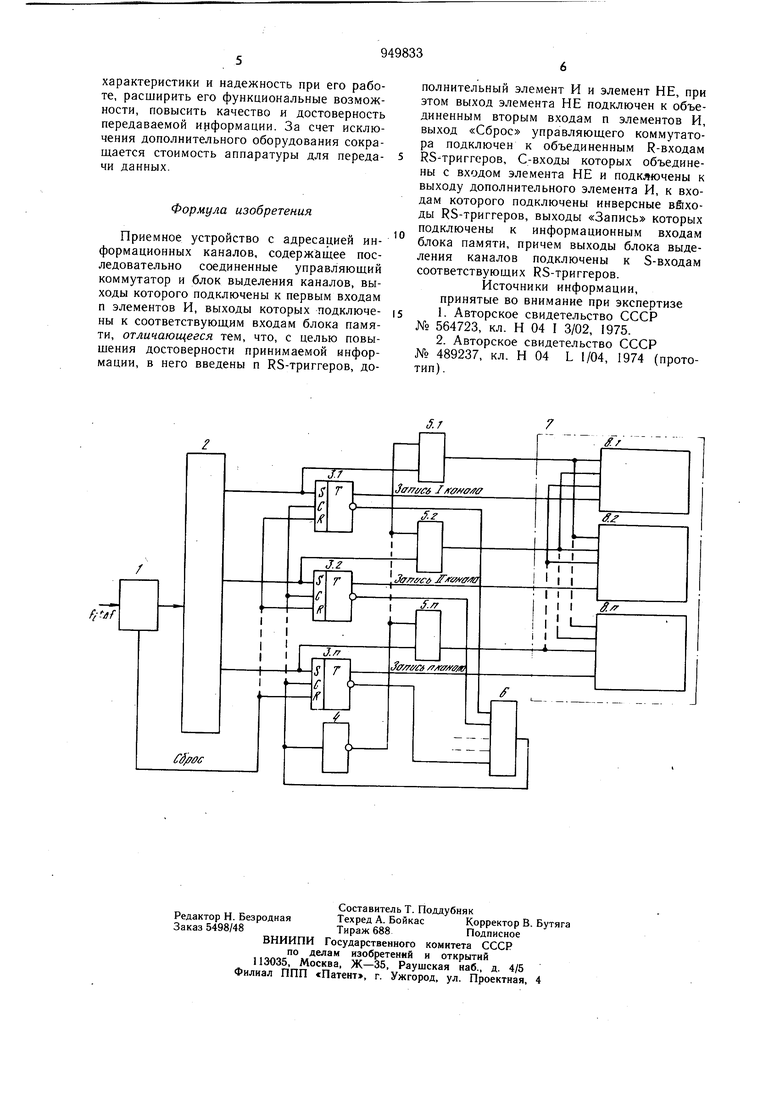

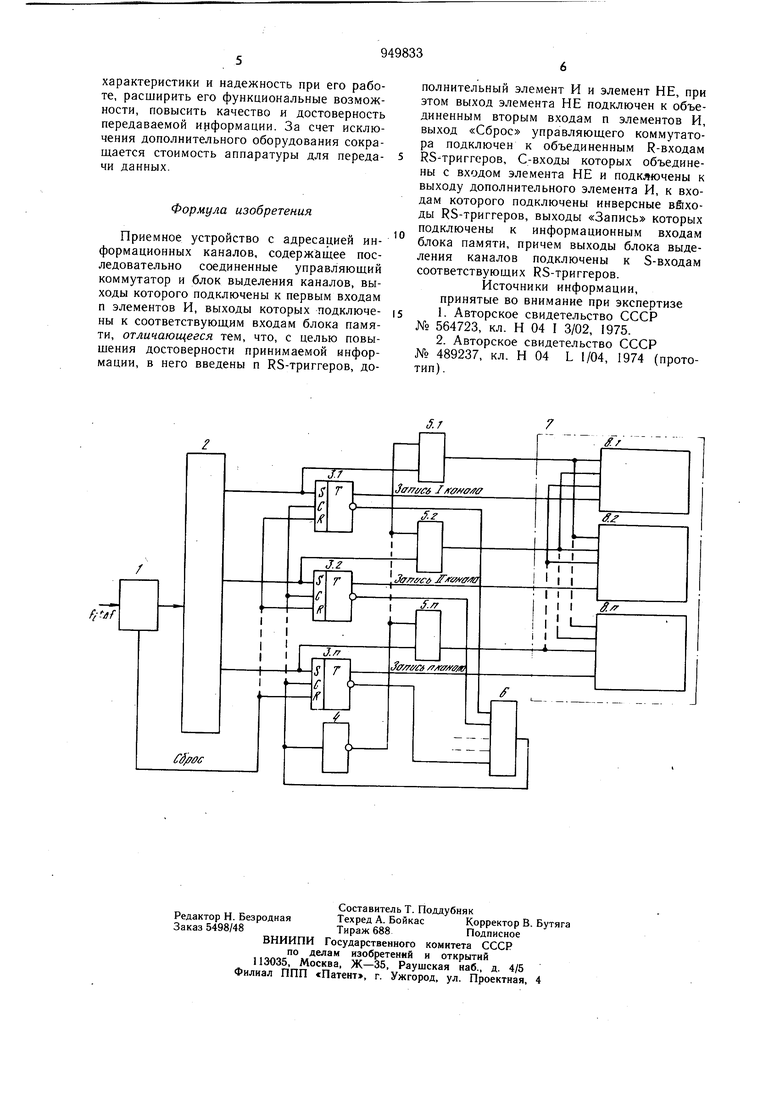

На чертеже представлена структурноэлектрическая схема устройства.

Нриемное устройство содержит управляющий коммутатор 1, блок 2 выделения каналов п RS-триггеры 3.1-З.п, элемент НЕ 4, п элементов И 5.1-5.п, дополнительный элемент И 6 и блок 7 памяти, содержащий п адресных ячеек 8.1-8 п.

Приемное устройство работает следующим образом.

При установлении связи, под действием сигналов «Вызов от АТС, на приемной стороне автоматически включается управляющий коммутатор 1, который формирует сигнал «Сброс, на R-входы RS-триггеров 3.1-Зп и одновременно подключает телефонную линию к блоку 2 выделения каналов.

Сигнал «Сброс устанавливает RS-триггеры 3.1-Зп в такое состояние, при котором на прямых выходах устанавливается логический «О, а на инверсных выходах - логическая «1.

Логические «О от триггеров подаются на адресные ячейки 8.1-8п соответственно и являются сигналами запрета работы счетчиков этих ячеек, следовательно они не записывают, подаются ли счетные импульсы от блока 2 выделения каналов по п-входам в любой из п адресных ячеек или нет.

Разрещением -для записи в любую из адресных ячеек является только наличие логической «1 на ее щине «Запись.

Одновременно логические «1 от всех инверсных выходов RS-триггеров 3.1 поступают на входы элемента И 6, с выхода которого логическая «1 поступает на С-входы, RS-триггеров 3.1-З.п и разрещает им принимать сигналы по S-входам. Кроме того, логическая «1 с выхода элемента И 6 инвертируется элементом НЕ 4, и с его выхода уже логический «О подается на первые входы элементов И 5.1 - 5.П, тем самым дополнительно запрещая всякое прохождение импульсов к адресным ячейкам 8.1-8.п. Таково исходное состояние приемного устройства после установления связи по АТС.

При использовании предварительного импульса одной из имеющихся в передающем устройстве частот в качестве маркерного сигнала вся задача состоит в отделении этого импульса от всей последующей серии

несущих цифровую информацию импульсов и использование его для:

-включения нужной адресной ячейки (подать на время приема информации логическую «1 на шину «Запись i канала ;

-подачи разрешающего сигнала (логической «1) на элементы И 5.1-5.п пропускающие импульсы счета информации от каждого канала блока 2 выделения каналов к входам адресных ячеек 8.1-8.п;

- подачи запирающего сигнала (логического «О) на С-входы всех RS-триггеров 3.1-З.п, тем самым зафиксировав- их- состояния после прохождения маркерного импульса.

Частот для манипуляции на передающем устройстве столько, сколько видов передаваемой информации. Каждая из этих частот (она же является и индивидуальным маркерным сигналом) при передаче цифровой информации выделяется в блоке 2 выделения каналов соответствующими фильтрами, детектируется, и на выходе каждого канала принятая информация представлена последовательностью логического «О и логической «Ь, равной количеству переданных импульсов (т. е. набранной на передающей стороне цифре).

.Итак, при посылке передающим устройством маркерного . (первого) импульса (например, для 2-го передающего абонента для формирования маркерного импульса

0 используется частота 2-го канала, а его пер. сональная адресная ячейк - 8.2) последний, после выделения, в виде логической «1 с выхода блока 2 выделения каналов поступит на S-вход RS-триггера 3.2, что вызовет его опрокидывание, т. е. на шине «Запись

5 II канала появится разрешающая запись для ячейки 8.2, и только ей, логическая «1. Одновременно с инверсного выхода этого RS-триггера 3.2 на вход элемента И 6 поступит логический «О, что, в свою очередь, . вызовет появление на его выходе также логического «О. Этот сигнал, поступив на С-входы триггеров, зафиксирует их состояние, т. е. все, кроме 2-го, останутся в первоначальном состоянии, и приходящие по любому каналу выделения импульсы уже

5 не смогут изменить их состояний.

Кроме того, от элемента НЕ 4 логическая «1 поступит на первые входы элементов И 5.1-5.П, что позволит прохождение счетных импульсов через них от каналов выделения блока 2 к адресным ячейкам

° 8.1-8п.

На этом выбор адресной ячейки 8.1-8.п и приведение ее в готовность (в разобранном примере только ячейки 8.2) к приему цифровой информации окончены. Выбор

5 Других ячеек своими абонентами осуществляется аналогично приведенному примеру. Использование предлагаемого устройства позволяет улучшить эксплуатационные характеристики и надежность при его работе, расширить его функциональные возможности, повысить качество и достоверность передаваемой и{1формации. За счет исключения дополнительного оборудования сокращается стоимость аппаратуры для передачи данных. Формула изобретения Приемное устройство с адресацией информационных каналов, содержащее последовательно соединенные управляющий коммутатор и блок выделения каналов, выходы которого подключены к первым входам п элементов И, выходы которых подключены к соответствующим входам блока памяти, отличающееся тем, что, с целью повыщения достоверности принимаемой информации, в него введены п RS-триггеров, дополнительный элемент И и элемент НЕ, при этом выход элемента НЕ подключен к объединенным вторым входам п элементов И, выход «Сброс управляющего коммутатора подключен к объединенным R-входам НЗ триггеров, С-входы которых объединены с входом элемента НЕ и подключены к выходу дополнительного элемента И, к входам которого подключены инверсные в&ходы RS-триггеров, выходы «Запись которых подключены к информационным входам блока памяти, причем выходы блока выделения каналов подключены к S-входам соответствующих RS-триггеров. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 564723, кл. Н 04 I 3/02, 1975. 2.Авторское свидетельство СССР № 489237, кл. Н 04 L 1/04, 1974 (прототип).

ff-jif

Авторы

Даты

1982-08-07—Публикация

1980-05-21—Подача