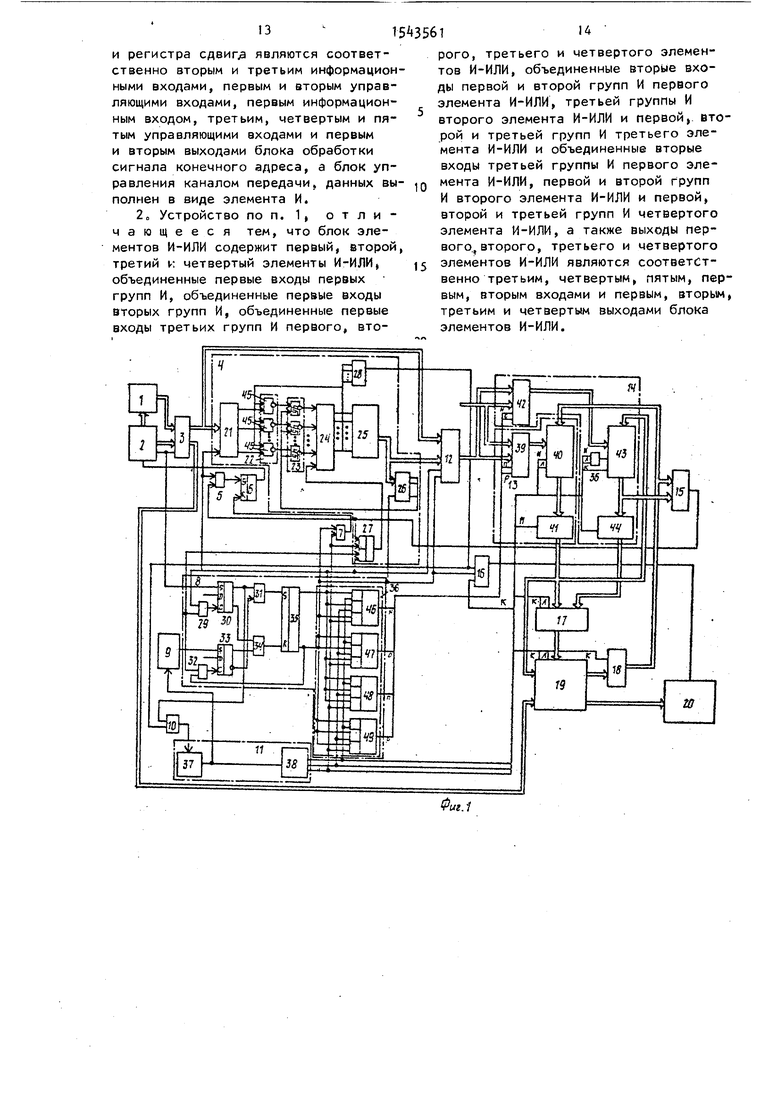

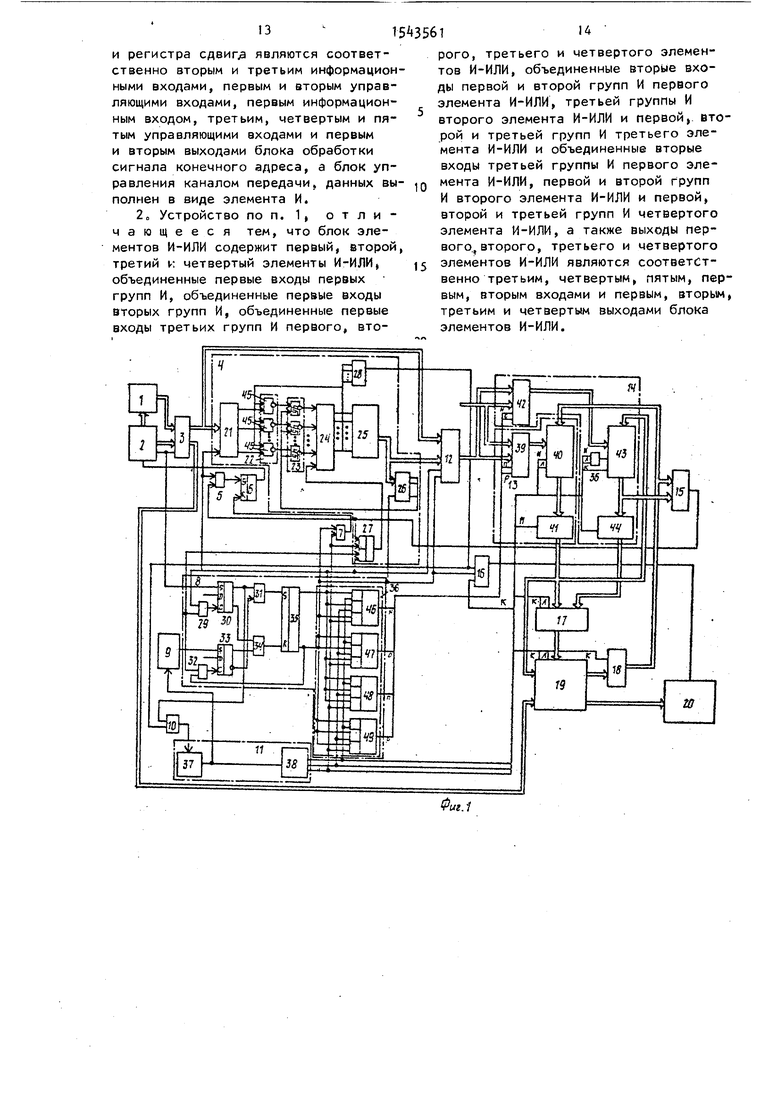

налов приоритета, блок 13 обработки сигнала начального адреса, блок 1 обработки сигнала конечного адреса, блок 15 сравнения, блок 16 управления, каналом передачи данных, коммутатор 17 адресных сигналов, второй регистр 18 сдвига и буферный ЗБ 19. На фиг. 1 обозначен также канал 20 передачи данных.

Блок регистрации сигналов приоритета образуют первый дешифратор 21, первый и второй блоки 22 и 23 элементов ИЛИ-НЕ, регистр 2k сдвига, блок25 выбора приоритета передачи сигнала, второй дешифратор 26, элемент И-ИЛИ 27 и элемент ИЛИ 28.

Формирователь 8 сигналов управления коммутацией сигналов начального и конечного адресов содержит первый элемент И 29, первый В-триггер 30 второй элемент И 31, третий элемент И 32, второй D-триггер 33 четвер ч элемент И 3, RS-триггер 35 и блок i36 элементов И-ИЛИ.

Блок Н синхронизации выполнен в виде тактового генератора 37 и рас пределителя 38 импульсов.

Блок 13 обработки сигналов начального адреса образуют коммутатор 39 элемент kQ памяти (ЭП) и регистр 1 сдвига.

I Блок 1 обработки сигналов конеч ного адреса включает коммутатор 2, ЭП A3 и регистр М сдвига.

Первый и второй блоки 22 и 23 элементов ИЛИ-ВЕ содержат элементы ИЛИ- НЕ 5.

Блок 36 элементов И-ИЛИ выполненi а виде первого, второгоs третьего и четвертого элементов И-ИЛИ .

Устройство для согласования потока телеметрических отсчетов работает следующим образом.

10

и

30

35

40

Пусть из блока 2 сокращения избыточности поступают отсчеты трех уровней приоритетов Ед, Е в и Ес, которые запоминаются в буферном ЗБ 19, причем наивысший приоритет Ед, а наинизший - Ес. В канал 20 должны поступать вначале все отсчеты с наивысшим из имеющихся приоритетов, а затем остальные. Если при передаче в канал 20 отсчетов с низшим уровнем приоритета из блока 2 начинают поступать отсчеты с приоритетом более высоким, то они должны передаваться в первую очередь, а передача отсчетов с более низким приоритетом должна прерываться.

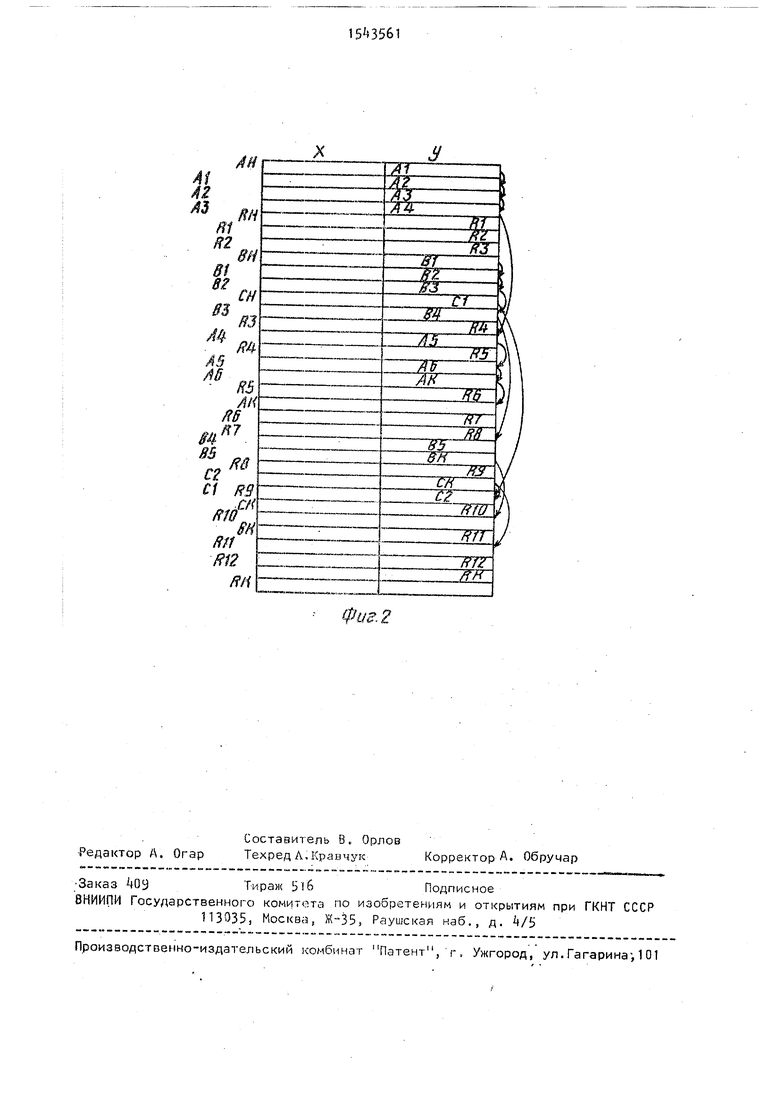

В буферном ЗБ 19 значения поступающих отсчетов размещаются в следующем логическом порядке.

Рассмотрим состояние буферного ЗБ 19 в некоторый момент времени. Пусть отсчеты с приоритетом Ед находятся в ячейках с адресами АН, А1, А2, A3, , A5, Аб, отсчеты с приоритетом Ев - в ячейках ВН В1, 82, ВЗ, 84, В5, а отсчеты с приоритетом Ес - в ячейках СН, С1, С2. Ячейки АК, ВК, СК зарезервированы для записи очередных отсчетов соответствующих приоритетов. Оставшиеся ячейки ЕШ, R1-R12, RK свободны и заполняются по мере поступления отсчетов.

Для организации ячеек в блоки в соответствии с приоритетом находящихся в них отсчетов используется принцип косвенной адресации. В адресной части каждой ячейки записан ад- оес следующей ячейки, в которой хранится последующий отсчет с данным приоритетом. Так, например, в адресной части ячейки АН хранится ссылка, т.е. адрес ячейки А1, в ячейке А1 - адрес ячейки А2 и т.д, вплоть до ячейки А5 В ячейке Аб хранится адС блока 2 сокращения избыточности 45 рес (ссшжа) зарезервированной ячейслучайным образом приходят телеметрические слова (значение отсчета, данные о приоритете, тактовый импульс)9 предназначенные для буферизации в буферном ЗБ 19 и дальнейшего посту

50

кй АК. Аналогичным образом организуются ячейки, предназначенные для хранения отсчетов с приоритетами Е9, и Ес, а также свободные ячейки R.

Таким образом, все ячейки логически объединены в блоки А, В, С, в которых находятся отсчеты соответствующих приоритетов, и блок свободных ячеек R. Начальные и конечные адреса каждого из блоков записаны соответственно в ЭП 0 и 43 начального и конечного адресов. Адреса ячеек с начальными и конечными адресами блоков определяются приоритетом блока данных

5

пления с частотой fK в канал 20 передачи данных.

Буферный ЗБ 19 логически построен пооследующему прин«4ипу.

Каждая ячейка состоит из двух час- тей X и Y (фиг. 2). Часть X предназ- начена для записи отсчета, а часть Y - адресная и служит для организации блоков отсчетов по Их приоритетам.

,

i

10

и

30

35

40

5 35614

Пусть из блока 2 сокращения избыточности поступают отсчеты трех уровней приоритетов Ед, Е в и Ес, которые запоминаются в буферном ЗБ 19, причем наивысший приоритет Ед, а наинизший - Ес. В канал 20 должны поступать вначале все отсчеты с наивысшим из имеющихся приоритетов, а затем остальные. Если при передаче в канал 20 отсчетов с низшим уровнем приоритета из блока 2 начинают поступать отсчеты с приоритетом более высоким, то они должны передаваться в первую очередь, а передача отсчетов с более низким приоритетом должна прерываться.

В буферном ЗБ 19 значения поступающих отсчетов размещаются в следующем логическом порядке.

Рассмотрим состояние буферного ЗБ 19 в некоторый момент времени. Пусть отсчеты с приоритетом Ед находятся в ячейках с адресами АН, А1, А2, A3, , A5, Аб, отсчеты с приоритетом Ев - в ячейках ВН В1, 82, ВЗ, 84, В5, а отсчеты с приоритетом Ес - в ячейках СН, С1, С2. Ячейки АК, ВК, СК зарезервированы для записи очередных отсчетов соответствующих приоритетов. Оставшиеся ячейки ЕШ, R1-R12, RK свободны и заполняются по мере поступления отсчетов.

Для организации ячеек в блоки в соответствии с приоритетом находящихся в них отсчетов используется принцип косвенной адресации. В адресной части каждой ячейки записан ад- оес следующей ячейки, в которой хранится последующий отсчет с данным приоритетом. Так, например, в адресной части ячейки АН хранится ссылка, т.е. адрес ячейки А1, в ячейке А1 - адрес ячейки А2 и т.д, вплоть до ячейки А5 В ячейке Аб хранится ад5 рес (ссшжа) зарезервированной ячей0

кй АК. Аналогичным образом организуются ячейки, предназначенные для хранения отсчетов с приоритетами Е9, и Ес, а также свободные ячейки R.

Таким образом, все ячейки логически объединены в блоки А, В, С, в которых находятся отсчеты соответствующих приоритетов, и блок свободных ячеек R. Начальные и конечные адреса каждого из блоков записаны соответственно в ЭП 0 и 43 начального и конечного адресов. Адреса ячеек с начальными и конечными адресами блоков определяются приоритетом блока данных

или константой (для Н и К). В исходном состоянии RS-триггер 6 установлен в единичное состояние, первый и второй RS-триггеры 30 и 33 и регистр 2 в нулевое состояние. В ЭП 0 и 3 записаны начальные и конечные адреса (AM АК,,ВМ ВК,,.., RM - RK) а в буферном ЗБ 19 организованы блоки А| В и С из одной ячейки (в частях Y ячеек записаны собственные адреса) и блок R из всех остальных ячеек.. Цепи начальной установки для упрощения не указаны.

Устройство для согласования потоков телеметрических отсчетов работает в двух режимах: запись поступающего отсчета в буферный ЗБ 19 и считывание очередного отсчета с наивысшим приоритетом из буферного ЗБ 19 в кап нал 20. Инициация режимов работы (запись/считывание) осуществляется путем установки соответствующих флажков (первый D-триггер 30 (второй D10

15

20

на время, необходимое для записи о счета в буферный ЗБ 19.

Приоритет отсчета определяется формирователем 1 на основании инфо мации, поступающей с блока 2 сокра щения избыточности, например номера измерительного канала, номера программы опроса или др0 При этом формирователь 1 может иметь различную структуру, в частности представлять собой постоянный запоминающий блок где в ячейках с адресами, соответствующими номерам информационных ка налов (программ опроса или др.), за писаны их приоритеты ЕЛ, Ев, Ес. Зн чение отсчета с выхода первого регистра 3 поступает на первые информ ционные входы (X) буферного ЗБ 19, а значение приоритета - на первый информационный вход коммутатора 12, управляемого RS-триггером 35, и информационный вход блока k регистрации, который регистрирует приоритет

триггер 33)) тактовыми импульсами бло- 25 логических блоков отсчетов для по0

5

0

на время, необходимое для записи отсчета в буферный ЗБ 19.

Приоритет отсчета определяется формирователем 1 на основании информации, поступающей с блока 2 сокращения избыточности, например номера измерительного канала, номера программы опроса или др0 При этом формирователь 1 может иметь различную структуру, в частности представлять собой постоянный запоминающий блок, где в ячейках с адресами, соответствующими номерам информационных каналов (программ опроса или др.), записаны их приоритеты ЕЛ, Ев, Ес. Значение отсчета с выхода первого регистра 3 поступает на первые информационные входы (X) буферного ЗБ 19, а значение приоритета - на первый информационный вход коммутатора 12, управляемого RS-триггером 35, и информационный вход блока k регистрации, который регистрирует приоритеты

5 логических блоков отсчетов для по

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1981 |

|

SU995123A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство сопряжения | 1981 |

|

SU1121667A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение быстродействия. Устройство содержит формирователь (Ф) сигналов программных приоритетов, блок сокращения избыточности эл-тов сообщения, регистры сдвига, блок регистрации сигналов приоритета, эл-ты И, RS-триггер, Ф сигналов управления коммутацией сигналов начального и конечного адресов, делитель частоты, эл-т ИЛИ, блок синхронизации (БС), коммутатор сигналов приоритета, блоки обработки сигналов начального и конечного адресов, блок сравнения, блок управления каналом передачи данных, коммутатор адресных сигналов и буферный запоминающий блок (БЗБ), а также канал передачи данных. Данное устройство работает в двух режимах: запись поступающего отсчета в БЗБ и считывание очередного отсчета с наивысшим приоритетом из БЗБ в канал передачи данных. Синхронизация работы в каждом из режимов осуществляется при помощи соответствующих им сеток частот, которые вырабатываются Ф формирователем сигналов управления коммутацией и БС. Цель достигается за счет инициации режимов работы в пределах трех периодов тактовой частоты. 1 з.п. ф-лы, 2 ил.

ка 2 сокращения избыточности или импульсами с выхода делителя задающего частоту передачи данных в канал 20.

Синхронизация работы в каждом из режимов осуществляется при помощи соответствующих им сеток частот, вырабатываемых формирователем 8 и блоком 11 синхронизации. При этом предусматривается устранение формирователем 8 конфликтов, возникающих при одновременных (в пределах трех периодов тактовой частоты Јт) требованиях на запись отсчета от блока 2 сокращения избыточности и считывание от делителя 9. Требование, которое пришло позже, запоминается соответствующим флажком, осуществляющим переключение RS-триггера 35 после окончания текущего цикла.

Рассмотрим работу устройства для согласования потоков телеметрических отсчетов при записи поступившего из блока 2 сокращения избыточности отсчета в буферный ЗБ 19 и при считы вании из него очередного отсчета в канал 20. Пусть в буферный ЗБ 19 производится запись отсчета с приоритетом Еь, а считывается отсчет с высшим приоритетом.

При поступлении телеметрического слова с блока 2 сокращения избыточности значение отсчета и его приоритет -запоминаются в первом регистре 3

5

0

0

0 5

5

следующего извлечения в режиме считывания из буферного ЗБ 19 отсчетов с максимальным текущим приоритетом. Приоритет отсчета через первый дешифратор 21 и первый и второй блоки 22 и 23 элементов ИЛИ-НЕ, поступает на вход регистра 2k. По срезу импульса, формируемого на третьем выходе распределителя 38, соответствующий приоритету разряд регистра 2k устанавливается в единицу, а значения остальных подтверждаются при помощи первого и второго блоков 22 и 23 элементов ИЛИ-НЕ. Блок 25 выбора на основании выходной информации регистра определяет максимальный существующий в ЗБ 19 приоритет,, Таким образом, на выходе блока k регистрации постоянно присутствует информация о номере блока отсчетов с наивысшим текущим приоритетом.

В режиме записи отсчета коммутатор 12 подключает выход регистра 3 (приоритет отсчета) входам коммутаторов 39 и 42.

Импульс с первого выхода распределителя 38 разрешает прохождение сигнала приоритета через коммутатор k2 на адресные входы ЭП 43 и сигнала константы с входа константы устройства для согласования потоков те леметрических отсчетов через коммутатор 39 на адресные входы ЭП 0. Считанные при этом из ЭП kQ началь

715

ный адрес резервной ячейки, предназначенной для записи текущего отсче- та, и конечный адрес блока ВК из ЭП 3 записываются соответственно в регистры 41 и й„

На втором такте работы импульс с второго выхода распределителя 38 осуществляет подачу через коммутатор 39 начального адреса резервной ячейки RH на адресные входы буферного ЗБ 19, чтение из ячейки RH буферного ЗБ 19 ссылки На следующую резервную ячейку Rt, запись ее во второй регистр 18, а также запись в ЭП 3 знамения нового конечного адреса RH блока Н вместо прежнего ВК.

На третьем такте импульс с третьего выхода распределителя 38 через коммутатор 17 подключает к адресным вхо дам буферного ЗБ 19 выход регистра kk и, соответственно, записывает по адресу ВК значение отсчета (часть X ячейки) и ссылку на новый адрес RH конечной ячейки блока ВС. Кроме того,, этот же импульс переписывает из второго регистра 18 в ЗП 0 новый начал,, ный адрес R1 блока R прежнего адреса RH и производит чтение из ЭП 43 адреса RK блока R (путем соответствующего переключения коммутатора 2), Совпадение считанного адреса RK со ссылкой записанной во втором регистре 18, свидетельствует об исчерпании резервных ячеек (в блоке R остается одна)а При этом, выходной импульс с блока 15 сов падения устанавливает в нулевое состояние RS-триггер 65 который запрещает блоку 2 сокращения избыточности выдачу отсчетов до разгрузки буфер- ного ЗБ 19- На этом цикл записи отсчета заканчивается.

В режиме считывания отсчета из буферного ЗБ 19 RS-триггер 35 при помощи коммутатора 12 подключает блок 25 выбора к первым информационным входам коммутаторов 39 и k2. Это обеспечивае выборку для считывания блока данных с наивысшим текущим приоритетом (в данном примере блок А)„

На первом такте импульс с первого выхода распределителя 38 осуществляет при помощи коммутаторов 39 и 2 подключение адресных входов ЭП 0 и k2 соответственно к выходу коммутато ра 12 и входу сигнала константы устройства для согласования потоков телеметрических отсчетов и считывает начальный адрес АН блока данных А в

0

к

56

. .

ГО

35

50

1 ,8

регистр и конечный адрес RK резервного блока R в регистр М.

На втором такте производится чтение из буферного ЗБ 19 по адресу АН - значения отсчета (часть X ячейки), который поступает на вход канала 20 (при этом на его управляющий вход через блок 16 управления поступает синхроимпульс), и ссылки на последующую ячейку А1 блока А, подлежащую считыванию в следующем цикле. Этот адрес запойинается во втором регистре 18„ Параллельно в ЭП 3 записывается новый конечный адрес АН резервного блока R вместо прежнего RK.

На третьем такте в ЭП 0 записывается новый начальный адрес А1 блока А вместо прежнего АН, а в буферный ЗБ 19 по адресу RK - ссылка на ячейку АН. Кроме того, из ЭП 3 считывается конечный адрес АК блок А и сравнивается со ссылкой из второго регистра 18 блока 15 сравнения При совпадении адресов (блок А исчео пан) происходит сброс соответствующего разряда в регистре 2 при помощи второго дешифратора 26, второго блока 23 элементов ИЛИ-НЕ и элемента И-ИЛИ 27. Параллельно через второй элемент И 7 осуществляется перевод (подтверждение) в единичное состояние RS-три - гера 6S что разрешает блоку 2 сокращения избыточности выдачу отсчетов.

В случае отсутствия отсчетов с блока 2 сокращения избыточности и передачи всей информации из буферного ЗБ 19 а канал 20 работа устройства для согласования потоков телеметрических отсчетов приостанавливается путем блокировки тактового генератора 37 сигналом с выхода элемента ИЛИ 10.

tj Последующий запуск тактового генератора 37 осуществляется при поступлении первого же импульса отсчета с блока 2 сокращения избыточности.

Формула изобретения

91

чем выходы буферного запоминающего блока и блока управления каналом передачи данных являются соответственн информационным и управляющим выходам устройства, отличающеес тем, что, с целью повышения быстро-, действия, введены последовательно соединенные первый регистр сдвига блок регистрации сигналов приоритета коммутатор сигналов приоритета, блок обработки сигнала начального адреса и коммутатор адресных сигналов, выхо которого подсоединен к адресному входу буферного запоминающего блока, последовательно соединенные блок обработки сигнала конечного адреса, блок сравнения, первый элемент И и RS-триггер, прямой выход которого подсоединен к управляющему входу блока сокращения избыточности элементов сообщения, последовательно соединенные элемент ИЛИ, блок синхронизации, делитель частоты, формирователь CHI- налов управления коммутацией начальных и конечных адресов, а также второй элемент И и второй регистр сдвига, при этом первый информационный вход первого регистра сдвига через формирователь сигналов программных приоритетов подключен к первому информационному выходу блока сокращения избыточности элементов сообщени второй информационный выход и управляющий выход которого подключены соответственно к второму информационному входу и объединенным управляющему входу первого регистра сдвига и упраляющему входу формирователя сигналов управления коммутацией начальных и конечных адресов, первый, второй, и третий выходы которого подсоединены соответственно к первому входу элемента ИЛИ, объединенным первому управляющему входу.блока регистрации сигналов приоритета, второму входу первого элемента И и первому управляющему входу коммутатора сигналов приоритета и объединенным первому входу второго элемента И, второму управляющему входу коммутатора сигналов приоритета, первому входу блока управления каналом передачи данных и второму управляющему входу блока регистрации сигналов приоритета, .третий управляющий вход которого подключен к выходу блока сравнения, четвертый, пятый, шестой и седьмой выходы формирователя сигналов управления коммутацией

10

15

20

25

356l

30

35

40

45

50

5

10

начальных и конечных адресов подсоединены соответственно к первому и второму управляющим входам блока обработки сигнала начального адреса и первому и второму управляющим входам блока обработки сигнала конечного адреса , второй выход блока регистрации сигнала приоритета подсоединен к вторым входам элемента ИЛИ и блока управления каналом передачи данных, второй, третий, и четвертый выходы блока синхронизации подсоединены соответственно к второму, третьему и четвертому тактовым входам формирователя сигналов управления коммутацией начальных и конечных адресов и соответственно к третьему, четвертому и пятому управляющим входам блока обработки CHI- нала конечного адреса, второй и четвертый выходы блока синхронизации подсоединены соответственно к третьему входу блока обработки сигнала начального адреса и объединенным четвертому входу блока обработки сигнала начального адреса, тактовому входу блока регистрации сигналов приоритета и второму входу второго элемента И, выход которого подсоединен к S-входу RS-триггера, соответственно объединенные первый и второй управляющие входы коммутатора адресных сигналов и записывающий и считывающий входы буферного запоминающего блока подключены соответственно к третьему и четвертому выходам блока синхронизации, третий выход которого подсоединен к объединенным третьему входу блока управления каналом передачи данных и управляющему входу второго регистра сдвига, информационный вход которого подключен к второму выходу буферного запоминающего блока, первый и второй выходы первого регистра .- сдвига подсоединены соответственно к второму информационному входу коммутатора сигналов приоритета и первому информационному входу буферного запоминающего блока, второй информационный вход которого объединен с первым информационным входом блока обработки сигнала конечного адреса и подключен к выходу блока обработки сигнала начального адреса, выход которого подсоединен к второму информационному входу коммутатора адресных сигналов, второй информационный вход блока обработки сигнала начального адреса объединен с вторым входом

блока сравнения и подключен к выходу второго регистра сдвига, втором информационный вход блока обработки сигнала конечного адреса подключен к выходу коммутатора сигналов приоритета, причем объединенные третьи, информационные входы блока обработки сигнала начального адреса и блока обработки сигнала конечного адреса являются входом сигнала константы устройства, при этом блок регистрации сигналов приоритета содержит последовательно соединенные первый дешифратор, первый и второй блоки элемен1- тов ИЛИ-НЕ, регистр сдаига, блок вы бора приоритета передачи сигнале и второй дешифратор, выходы которого подсоединены к соответствующим вторым входам

второго блока элементов ИЛИ-ИЕ, а также элемент И-ИЛИ и элемент ИЛИ, входы которого объединены с соответствующими вторыми входами первого блока элементов ИЛИ-НЕ и подсоединены к соответствующим выходам регистра сдвига, а выход блока И-ИЛИ подсоединен к управляющему входу регистра сдвига, причем информационный и управляющий входы первого дешифратора, первый вход, объединенные второй и третий входы и четвертый вход элемента И-ИЛИf выходы блока выбора приоритета передачи сигнала и блока ИЛИ являются соответственно информационным входом, первым и вторым управляющими ,входами, тактовым входом, третьим уп- 1равляющим входом и первым и вторым выходами блока регистрации сигналов приоритета, формирователь сигналов управления коммутацией начальных и конечных адресов содержат последовательно соединенные первый элемент И, первый D-триггер, второй элемент И, RS-триггер и блок элементов И-ИЛИ, последовательно соединенные третий элемент И, второй D-т риггер и четвертый элемент И, выход которого подсоединен к R-входу RS-триггера, объединенные D-входы и инверсные выходы первого и второго D-триггероа подключены соответственно к общему проводу источника питания и вторым входам второго и четвертого элементов И, прямой и инверсный выходы RS-ipur- гера подсоединены соответственно к первому входу первого элемента И и объединенным второму входу блока элементов ИЛИ и первому входу третьего элемента И, причем S-входы первого

5

0

5

0

5

0

5

0

5

и второго D-триггеров и третий и четвертый входы блока элементов И-ИЛИ и объединенные пятый вход блока элементов И-ИЛИ и вторые входы первого и третьего элементов И являются соответственно управляющим входом, первым, вторым, третьим и четвертым тактовыми входами формирователя сигналов управления коммутацией начальных и конечных адресов, а прямой выход первого D-триггера, прямой и инверсный выходы RS-триггера, первый, второй, третий и четвертый выходы блока элементов И-ИЛИ являются соответственно первым, вторым, третьим, четвертым, пятым, шестым и седьмым выходами формирователя сигналов управления коммутацией начальных и конечных адресов, блок синхронизации содержит последовательно соединенные тактовый генератор и распределитель импульсов, причем вход и выход тактового генератора и первый, второй и третий выходы распределителя импульсов являются соответственно входом, первым., вторым, третьим и четвертым выходами блока синхронизации, блок обработки сигнала начального адреса содержит последовательно соединенные коммутатор, элемент памяти и регистр сдвига, причем первый и второй информационные входы и первый и второй управляющие , входы коммутатора, информационный вход элемента памяти, объединенные считывающий вход элемента памяти И управляющий вход регистра сдвига, а также записывающий вход элемента памяти и выход регистра сдвига являются соответственно первым и третьим информационными входами, первым и вторым управляющими входами, вторым информационным входом, третьим и четвертым управляющими входами и выходом блока обработки сигнала начального адреса, блок обработки сигнала конечного адреса содержит последовательно соединенные коммутатор, элемент памяти и регистр сдаига, а также элемент ИЛИ, выход которого подсоединен к считывающему входу элемента памяти, причем первый и второй информационные входы и первый и второй управляющие входы коммутатора, информационный вход элемента памяти, объединенные первый вход элемента ИЛИ и управляющий вход регистра сдвига, а также записывающий вход элемента памяти, второй вход элемента ИЛИ, выходы элемента памяти

Фиг. 2

| 0 |

|

SU351335A1 | |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ получения магнезитовых изделий | 1937 |

|

SU52608A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ( УСТРОЙСТВО ДЛЯ СОГЛАСОВАНИЯ ПОТОКОВ ТЕЛЕМЕТРИЧЕСКИХ ОТСЧЕТОВ | |||

Авторы

Даты

1990-02-15—Публикация

1987-12-22—Подача