4

СО

со

05 00

Изобретение относится к радиотехнике и может быть использовано в устройствах обработки информации. Цель изобретения - расширение функциональных возможностей путем фильтрации входного сигнала на нескольких частотах.

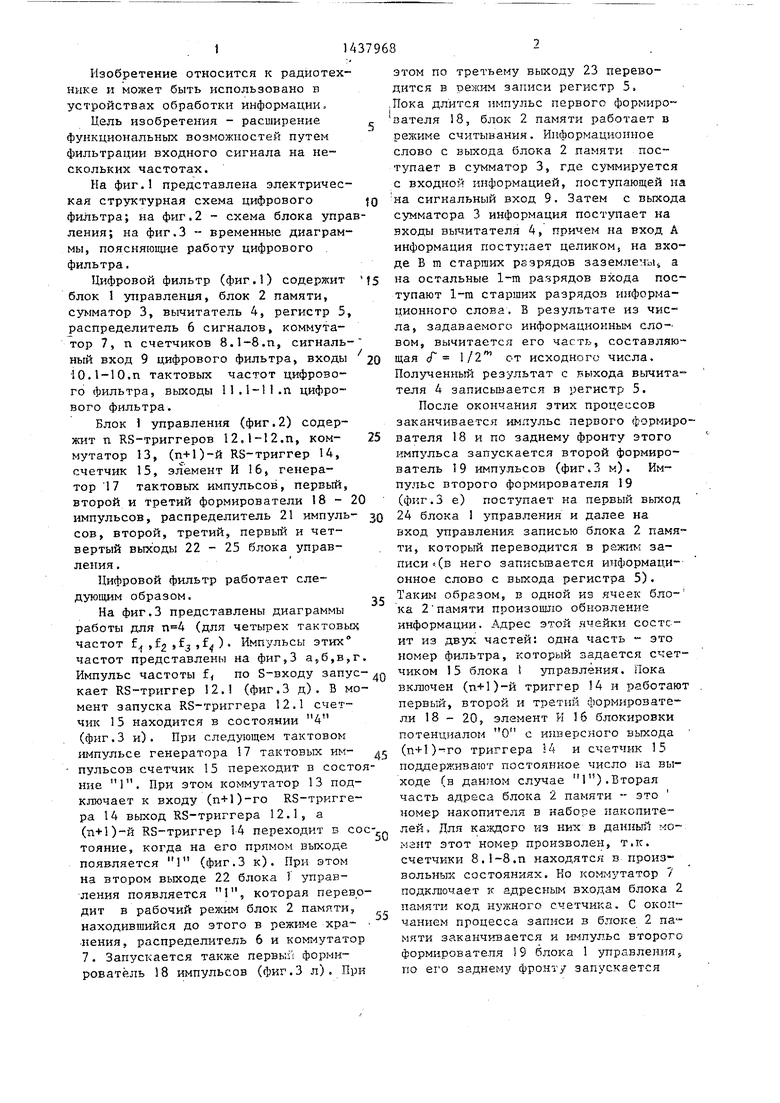

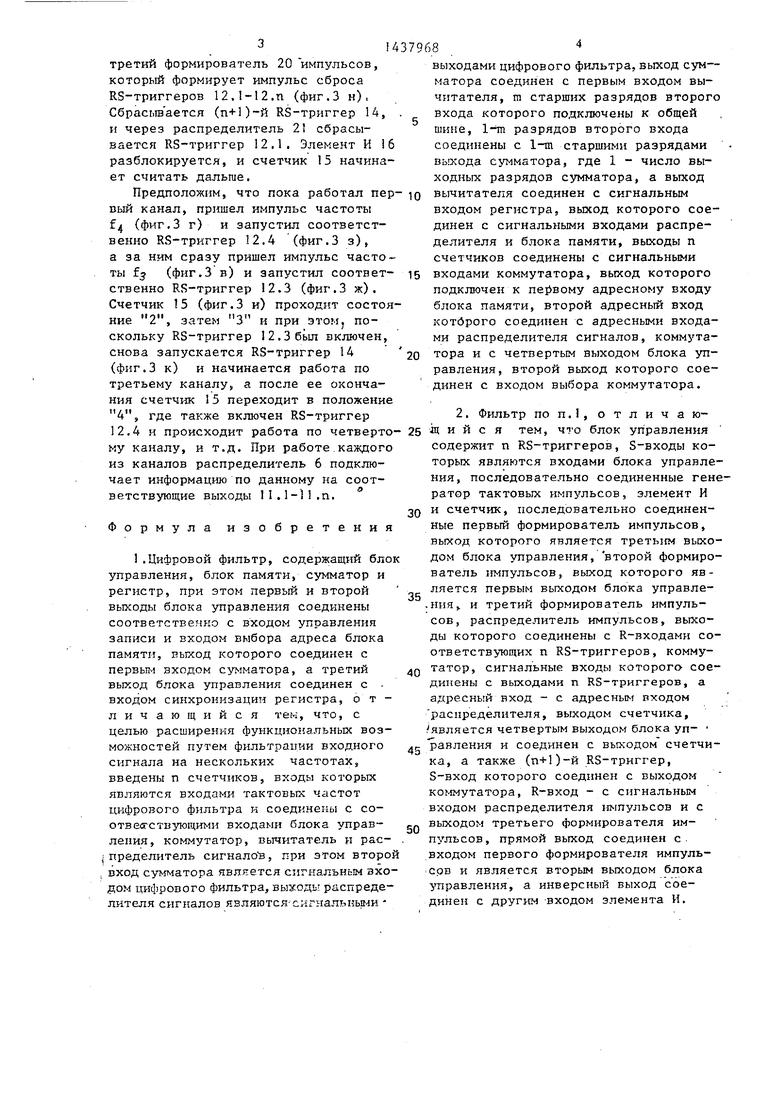

На фиг. представлена электрическая структурная схема цифрового фильтра; на фиг.2 - схема блока управления; на фиг.З - временные диаграммы, поясняющие работу цифрового фильтра.

Цифровой фильтр (фиг.О содержит блок 1 управления, блок 2 памяти, сумматор 3, вьиитатель 4, регистр 5, распределитель 6 сигналов, коммутатор 7, п счетчиков 8.1-8.П, сигнальный вход 9 цифрового фильтра, входы iO.l-10.П тактовых частот цифрового фильтра, выходы 11.1-ll.n цифрового фильтра.

Блок 1 управления (фиг.2) содержит п RS-триггеров 12.1-12.п, ком- мутатор 13, (п+1)-й RS-триггер 14, счетчик 15, элемент И 16, генератор 17 тактовых импульсов, первый, второй и третий формирователи 18-2 импульсов, распределитель 21 импуль- сов, второй, третий, первый и четвертый выходы 22 - 25 блока управления ,

Цифровой фильтр работает следующим образом.

На фиг.З представлены диаграммы работы для (для четырех тактовых частот f ,f2 ,f f) Импульсы этих частот представлены на фиг,3 а,б,в,г Импульс частоты f по S-входу запус кает RS-триггер 2. (фиг.З д). В мо мент запуска RS-триггера 12.1 счетчик 15 находится в состоянии 4 (фиг.З и). Цри следующем тактовом импульсе генератора 17 тактовых им- - пульсов счетчик 15 переходит в состоние 1. При этом коммутатор 13 подключает к входу (n-t-l)-ro RS-триггера 14 выход RS-триггера 12.1, а (п+1)-й RS-триггер 1-4 переходит в со тояние, когда на его прямом выходе появляется 1 (фиг.З к). При этом на втором выходе 22 блока 1 управления появляется 1, которая переводит в рабочий режим блок 2 памяти, находившийся до этого в режиме хра нения, распределитель 6 и коммутатор 7. Запускается также первый формирователь S8 импульсов (фиг.З л). При

g

s 0

5 Q

с

Q дд ,.

этом по третьему выходу 23 переводится в режим записи регистр 5. .Пока длится импульс первого формиро™ вателя 18, блок 2 памяти работает в режиме считывания. Информационное слово с выхода блока 2 памяти поступает в сумматор 3, где суммируется с входной информацией, поступающей на на сигнальный вход 9. Затем с выхода сумматора 3 информация поступает на входы вычитателя 4, причем на вход А информация поступает целиком, на входе В m старших рззрядов заземлены5 а на остальные 1-т разрядов входа поступают 1-т старших разрядов информационного слова, В результате из числа, задаваемого информационным ело- вом, вычитается его часть, составляющая Г l/Z от исходного числа. Полученный результат с выхода вычита™ теля 4 записьшается в регистр 5.

После окончания этих процессов заканчивается имлульс первого формирователя 18 и по заднему фронту этого импульса запускается второй формирователь 19 импульсов (фиг.З м). Импульс второго формирователя 19 (фиг.З е) поступает на первый выход 24 блока 1 управления и далее на вход управления записью блока 2 памяти, который переводится в режим записи «.(в него записьшается информаци-- онное слово с выхода регистра 5). Таким образом, в одной из ячеек бло- ка 2 памяти произошло обновление информации. Адрес этой ячейки состоит из двух частей: одна часть это номер фильтра, который задается счетчиком 15 блока 1 управления. Пока включен (п+1)-й триггер 4 и работают первый, второй и третий формирователи 18 - 20, элемент К 16 блокировки потенциалом О с инверсного выхода (п+1) триггера 14 и счетчик 15 поддерживают постоянное число на выходе (в данном случае 1).Вторая часть адреса блока 2 памяти - это номер накопителя в наборе накопителей. Для каждого из них в данный мо- мгнт этот номер произволен, т.к. счетчики 8.1-8.П находятся в произвольных состояниях. Ко комг.13 -татор 7 подключает к адресньм входам блока 2 памяти код нужного счетчика. С окончанием процесса записи в блоке 2 памяти заканчивается и импульс второго формирователя 19 блока 1 управления, по его заднему фронт/ запускается

третий формирователь 20 импульсов, который формирует импульс сброса RS-триггеров 12.1-12.П (фиг.З н). Сбрасьш ается (п+1)й RS-триггер 14, и через распределитель 21 сбрасывается RS-триггер 12.1. Элемент И 16 разблокируется, и счетчик 15 начинает считать дальше.

437968

выходами цифрового фильтра, выход сум- матора соединен с первым входом вы- читателя, m старших разрядов второго . входа которого подключены к общей

шине, l-m разрядов второго входа соединены с l-m старшими разрядами вьжода сумматора, где 1 - число выходных разрядов сумматора, а выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1990 |

|

SU1730718A1 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| Цифровой рекурсивный фильтр | 1988 |

|

SU1578720A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168282C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ КОНТРОЛЯ ПО РАДИОКАНАЛУ | 2005 |

|

RU2280330C1 |

| Устройство для передачи информации | 1989 |

|

SU1736001A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

Изобретение, относится к радиотехнике и м.б. использовано в устр-вах обраоотки информации. Цель изобретения - расширение функциональных возможностей путем фильтрации входного сигнала на нескольких частотах. Цифровой фильтр ЦФ содержит блок 1 управления, блок 2 памяти, сумматор 3, регистр 5, сигнальный вход 9 ЦФ, входы 10.I - 10.п тактовых частот ЦФ, выходы 11.1-11.п ЦФ. Для достижения цели в ЦФ введены п счетчиков 8.1- 8.П, входы которых являются входами тактовых частот ЦФ, коммутатор 7, вычитатель 4 и распределитель 6 сигналов . Блок 1 управления содержит п RS-триггеров, последовательно соединенные г-р тактовых импульсов, элемент И и счетчик, последовательно соединенные три формирователя импульсов и коммутатор, а также (п+1)-й RS-триггер. 1 з.п.ф-лы, 3 ил.

Предположим, что пока работал пер- IQ вычитателя соединен с сигнальным

вый канал, пришел импульс частоты f (фиг.З г) и запустил соответственно RS-триггер 12,4 (фиг.З з), а за ним сразу пришел импульс частоты f (фиг.З в) и запустил соответ- 15 входами коммутатора, выход которого ственно RS-триггер 12.3 (фиг.З ж). Счетчик 5 (фиг.3 и) проходит состояние 2, затем 3 и при 3TOMj поскольку RS-триггер 12.3бьт включен, снова запускается RS-триггер 14 20 (фиг.З к) и начинается работа по третьему каналу, а после ее окончания счетчик 15 переходит в положение 4, где также включен RS-триггер

подклзочен к первому адресному входу блока памяти, второй адресный вход котйрого соединен с адресными входами распределителя сигналов, коммутатора и с четвертым выходом блока управления, второй выход которого соединен с входом выбора коммутатора.

му каналу, и т.д. При работе каждого из каналов распределитель 6 подключает информацию по данному на соответствующие выходы 11.1-11.п.

Формула изобретения

входом регистра, выход которого соединен с сигнальными входами распределителя и блока памяти, выходы п счетчиков соединены с сигнальными

входами коммутатора, выход которого

подклзочен к первому адресному входу блока памяти, второй адресный вход котйрого соединен с адресными входами распределителя сигналов, коммутатора и с четвертым выходом блока управления, второй выход которого соединен с входом выбора коммутатора.

5

содержит п RS-триггеров, S-входы которых являются входами блока управления, последовательно соединенные генератор тактовых импульсов, элемент И и счетчик, последовательно соединенные первый формирователь импульсов, выход которого является третьим выходом блока управления, второй формирователь импульсов, выход которого является первым выходом блока управления и третий формирователь импульсов, распределитель импульсов, выходы которого соединены с R-входами соответствующих п RS-триггеров, коммутатор, сигнальные входы которого соединены с вькодами п RS-триггеров, а адресный вход - с адресныь входом распределителя, выходом счетчика, /является четвертым выходом блока уп- г- Давления и соединен с выходом счетчика, а также (п+1)-й RS-триггер, S-вход которого соединен с выходом коммутатора, R-вход - с сигнальным входом распределителя импульсов и с выходом третьего формирователя импульсов, прямой выход соединен с. входом первого формирователя импульсов и является вторым выходом блока ТгТфавления, а инверсный выход соединен с другим -входом элемента И.

0

0

Л

фи.7

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-15—Публикация

1986-09-19—Подача