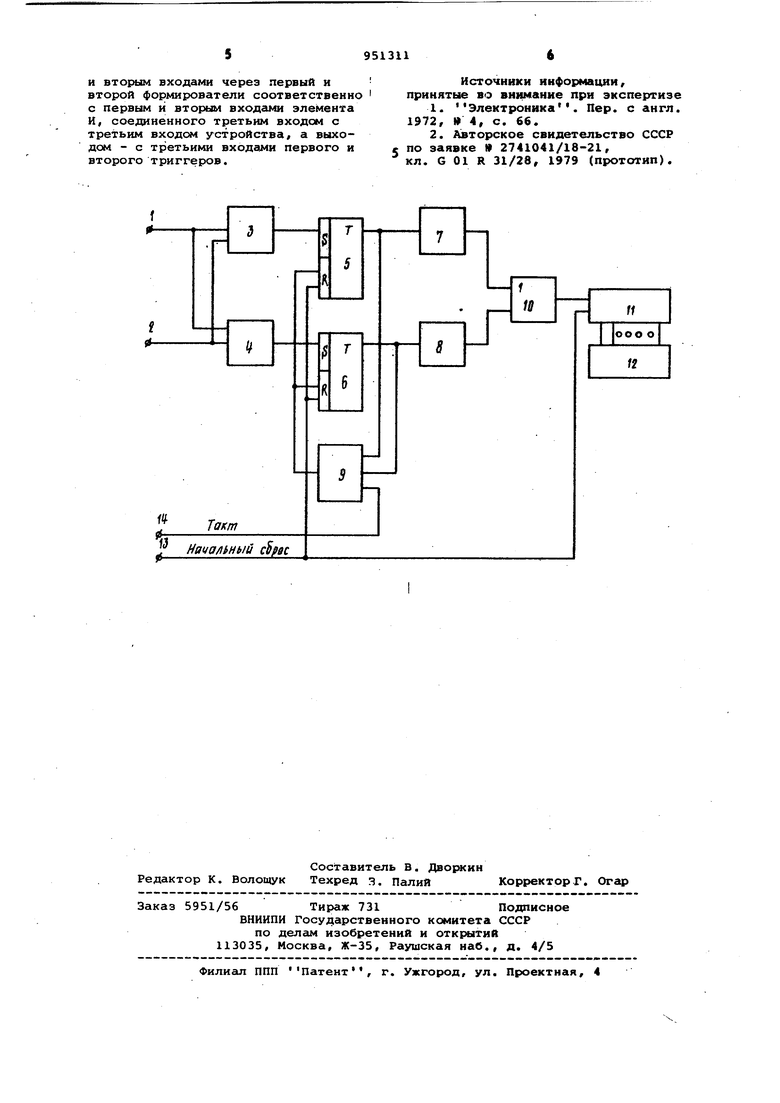

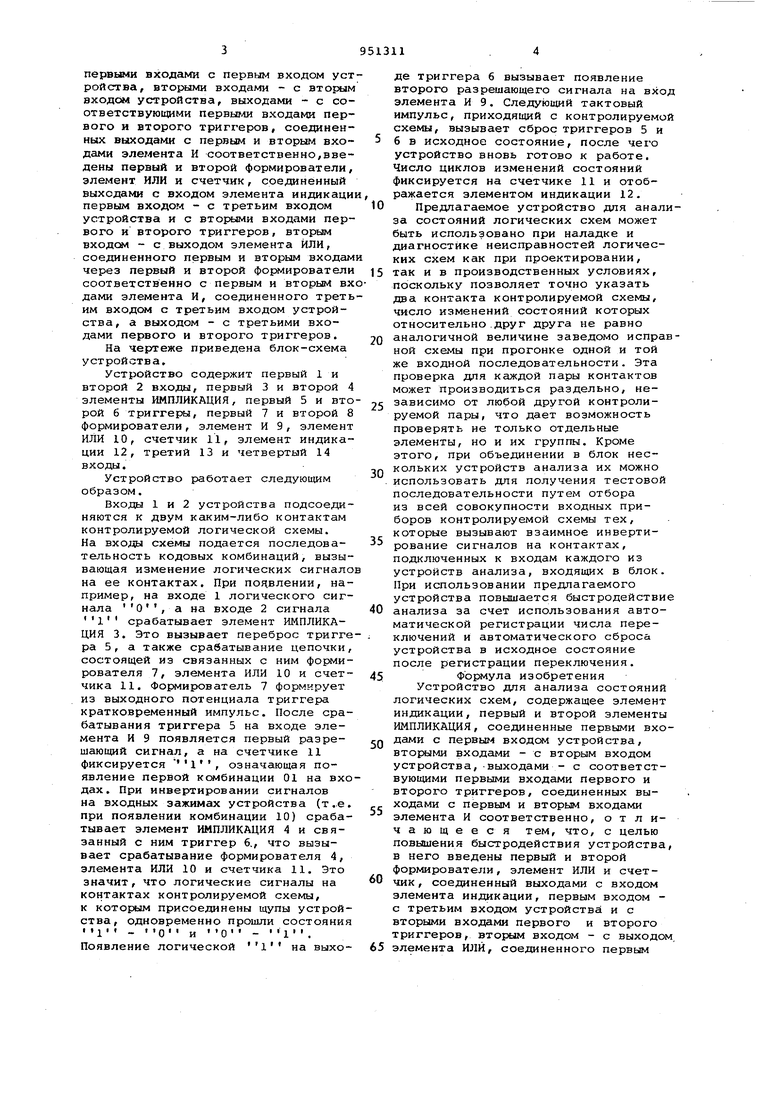

Изобретение относится к автомати ке и вычислительной технике и может быть использовано при реализации средств контроля и диагностики отказов логических узлов. Известно устройство для анализа изменений состояний, содержащее генератор кодов и логический анализатор состояний 1. Однако это устройство имеет огра ниченные функциональные возможности так как фиксирует только абсолютные (относительно некоторого наперед заданного уровня) изменения состояний схемы на одном контакте при подаче каждой очередной, кодовой комбинации . В результате не учитываетс изменение сигналов на контактах про веряемой схемы относительно друг друга. При этом теряется важная информация , позволяющая судить о правильности передачи сигналов по цепя схемы. Наиболее близким техническим решением к изобретению является устро ство, содержащее две электрические цепи, каждая из которых образована последовательно соединенным элементом ИМПЛИКАЦИЯ и триггером, причем первый вход первого элемента ИМПЛИКАЦИЯ и второй вход второго элемента ИМПЛИКАЦИЯ подключены к первому входу устройства, а второй вход первого элемента ИМПЛИКАЦИЯ и первый вход второго элемента ИМПЛИКАЦИЯ подключены к второму входу устройства, выходы триггеров подсоединены к входам элемента И, к выходу которого подключены первый элемент индикации и вход инвертора, к выходу которого подсоединен второй элемент индикации 2, Недостатками известного устройства являются невозможность автоматической быстродействующей регистрации числа изменений состояний между двумя контрольными точками измеряемой схемы, подсоединенными ко входам устройства анализа, а также снижение быстродействия, обусловленное сбросом триггеров вручную при необходимости повторного использования устройства. Цель изобретения - повьшение быстродействия устройства. Поставленная цель достигается тем, что в устройство для анализа состояния логических схем, содержащее элемент индикации, первый и второй элементы ИМПЛИКАЦИЯ, соединенные первыми входами с первым входом уст ройства, вторыми входами - с вторым входом устройства, выходами - с соответствующими первыгда входами первого и второго триггеров, соединенных выходами с первым и вторым входами элемента И соответственно,введены первый и второй формирователи, элемент ИЛИ и счетчик, соединенный выходами с входом элемента индикаци первым входом - с третьим входом устройства и с вторыми входами первого и второго триггеров, вторым входсм с выходом элемента ИЛИ, соединенного первым и вторым входам через первый и второй формирователи соответственно с первым и вторым вх дами элемента И, соединенного треть им входом с третьим входом устройства, а выходом - с третьими входами первого и второго триггеров. На чертеже приведена блок-схема устройства. Устройство содержит первый 1 и второй 2 входы, первый 3 и второй 4 элементы ИМПЛИКАЦИЯ, первый 5 и вто рой б триггеры, первый 7 и второй 8 формирователи, элемент И 9, элемент ИЛИ 10, счетчик 11, элемент индикации 12, третий 13 и четвертый 14 входы. Устройство работает следующим образом. Входы 1 и 2 устройства подсоединяются к двум каким-либо контактам контролируемой логической схемы, На входы схемы подается последовательность кодовых комбинаций, вызывающая изменение логических сигнало на ее контактах. При появлении, например, на входе 1 логического сигнала , а на входе 2 сигнала 1 срабатывает элемент ИМПЛИКАЦИЯ 3, Это вызывает переброс тригге ра 5 , а также срабатывание цепочки, состоящей из связанных с ним формирователя 7, элемента ИЛИ 10 и счетчика 11, Формирюватель 7 формирует из выходного потенциала триггера кратковременный импульс. После срабатывания триггера 5 на входе элемента И 9 появляется первый разрешающий сигнал, а на счетчике 11 фиксируется 1 означающая появление первой комбинации 01 на вхо дах. При инвертировании сигналов на входных зажимах устройства (т,е, при появлении комбинации 10) срабатывает элемент ИМПЛИКАЦИЯ 4 и связанный с ним триггер 6., что вызывает срабатывание формирователя 4, элемента ИЛИ 10 и счетчика 11, Это значит, что логические сигналы на контактах контролируемой схемы, к которым присоединены щупы устройства, одновременно прошли состояния Появление логической i« на выходе триггера 6 вызывает появление второго разрешающего сигнала на вход элемента И 9, Следующий тактовый импульс, приходящий с контролируемой схемы, вызывает сброс триггеров 5 и 6 в исходное состояние, после чего устройство вновь готово к работе. Число циклов изменений состояний фиксируется на счетчике 11 и отображается элементом индикации 12, Предлагаемое устройство для анализа состояний логических схем может быть использовано при наладке и диагностике неисправностей логических схем как при проектировании, так и в производственных условиях, поскольку позволяет точно указать два контакта контролируемой схемы, число изменений состояний которых относительно.друг друга не равно аналогичной величине заведомо исправной схемы при прогонке одной и той же входной последовательности. Эта проверка для каждой пары контактов может производиться раздельно, независимо от любой другой контролируемой пары, что дает возможность проверять не только отдельные элементы, но и их группы. Кроме этого, при объединении в блок нескольких устройств анализа их можно использовать для получения тестовой последовательности путем отбора из всей совокупности входных приборов контролируемой схемы тех, которые вызывают взаимное инвертирование сигналов на контактах, подключенных к входам каждого из устройств анализа, входящих в блок. При использовании предлагаемого устройства повышается быстродействие анализа за счет использования автоматической регистрации числа переключений и автоматического сброса устройства в исходное состояние после регистрации переключения. Формула изобретения Устройство для анализа состояний логических схем, содержащее элемент индикации, первый и второй элементы ИМПЛИКАЦИЯ, соединенные первыми входами с первым входом устройства, вторыьли входами - с вторым входом устройства,-выходами - с соответствующими первыми входами первого и второго триггеров, соединенных выходами с первым и вторым входами элемента И соответственно, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены первый и второй формирователи, элемент ИЛИ и счетчик , соединенный выходами с входом элемента индикации, первым входом с третьим входом устройства и с вторыми входами первого и второго триггеров, вторым входом - с выходом элемента ИЛИ, соединенного первьлм

и вторым входами через первый и второй формирователи соответственно с первым и вторым входами элемента И, соединенного третьим входом с третьим входом устройства, а Btixoдом - с третьими входами первого и второго триггеров.

Источники информации, принятые во внимание при экспертизе

1.Электроника. Пер. с англ. 1972, 4, с. 66.

2.Авторское свидетельство СССР по заявке О 2741041/18-21,

кл. G 01 R 31/28, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и локализации неисправностей логических схем | 1982 |

|

SU1092508A1 |

| Устройство для формирования тестов диагностики дискретных блоков | 1983 |

|

SU1149265A1 |

| Устройство для контроля цифровых модулей | 1981 |

|

SU1001015A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1264184A1 |

| Устройство для сбора информации | 1986 |

|

SU1388928A1 |

| ЦИФРОВОЙ ФАЗОМЕТР ДЛЯ ИЗМЕРЕНИЯ МГНОВЕННОГО ЗНАЧЕНИЯ УГЛА СДВИГА ФАЗ | 1991 |

|

RU2022280C1 |

| Устройство для контроля монтажа плат | 1982 |

|

SU1092434A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1166115A1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ ОТКЛОНЕНИЙ ПАРАМЕТРОВ ПРИ ДОПУСКОВОМ КОНТРОЛЕ | 2016 |

|

RU2617982C1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1367015A1 |

Авторы

Даты

1982-08-15—Публикация

1980-12-11—Подача