Изобретение относится к области релейной защиты и автоматики и может быть применено, например, в системах многоканального контроля и телесигнализации для различных технологических процессов.

Известно устройство для допускового контроля параметров, состоящее из блока управления контролем, операционного усилителя, блока масштабирования, блока измерения напряжений, первого и второго программируемых генераторов тока, блока регистрации и индикации и коммутатора (см. патент РФ №1440240, МПК G06F 11/36, опубл. 27.07.2004).

Недостатком указанного устройства является отсутствие контроля качества динамически изменяющихся процессов при случайном характере оценок измерений показателей качества, а также отсутствие учета изменяющейся погрешности измерений.

Известно устройство для сигнализации отклонений параметра при допусковом контроле, состоящее из датчиков, коммутатора, формирователей сигналов «Отклонение вверх» и «Отклонение вниз», генераторов импульсов, дешифраторов, счетчиков импульсов, элементов ИЛИ-НЕ, буферного каскада и элементов индикации (см. авторское свидетельство СССР №1357991, кл. G08B 23/00, опубл. 07.12.1987 в бюл. №45).

Недостатком указанного устройства является относительно большая временная задержка сигнализации при многоканальном контроле сигналов. Это обусловлено тем, что анализ каждого канала ведется до тех пор, пока не будет вынесено решение о наличии или отсутствии отклонений параметра от установленных допусков. Если элемент устройства, характеризуемый таким параметром, находится в каналах с последними номерами, то содержание его параметра может быть обнаружено только после просмотра всех каналов, что требует значительных временных затрат и не всегда приемлемо в системах реального времени.

Известно устройство сигнализации отклонений параметра при допусковом контроле, содержащее последовательно соединенные кнопку «Пуск», RS-триггер, генератор счетной частоты, счетчик импульсов, дешифратор, коммутатор, датчики по числу контролируемых каналов, формирователь сигнала «Отклонение вверх», формирователь сигнала «Отклонение вниз», три элемента И, два генератора импульсов, блок реверсивных регистров, элемент ИЛИ, два формирователя единичного импульса, блок установки в исходное состояние, регистр сдвига, два блока элементов И, шифратор, блок памяти и блок индикации (см. патент на полезную модель РФ №68736, МПК G08 23/00, опубликовано 27.11.2007, бюл. №33).

Недостатком устройства является относительно большая задержка при формировании сигнала тревоги на этапе предварительного контроля каналов.

Наиболее близким аналогом (прототипом) по технической сущности к предлагаемому устройству является устройство сигнализации при допусковом контроле по патенту на полезную модель РФ №140746, МПК G08 23/00 (опубликовано 20.05.2014), содержащее последовательно соединенные кнопку «Пуск», RS-триггер, генератор счетной частоты, два счетчика импульсов, дешифратор, коммутатор, датчики по числу контролируемых каналов, формирователь сигнала «Отклонение вверх», формирователь сигнала «Отклонение вниз», три элемента И, два генератора импульсов, блок реверсивных регистров, элемент ИЛИ, два формирователя единичного импульса, блок установки в исходное состояние, регистр сдвига, два блока элементов И, шифратор, блок памяти, блок индикации, блок идентификации сигнала тревоги, блок анализа двухэтапного поиска сигнала и формирователь периода последовательности импульсов.

Недостатком устройства является относительно большая задержка при формировании сигнала тревоги на этапе предварительного контроля каналов.

Техническим результатом, достигаемым с помощью заявленного устройства для сигнализации отклонения параметров при допусковом контроле, является повышение быстродействия двухэтапного поиска сигнала тревоги в системе многоканального контроля путем адаптивного изменения длительности предварительного просмотра каналов на первом этапе поиска сигнала тревоги.

В заявленном устройстве для сигнализации отклонения параметров при допусковом контроле технический результат достигается тем, что в известное устройство для сигнализации отклонений параметров при допусковом контроле, содержащее N≥2 датчиков, выход каждого n-го из которых, n=1, 2, …, N, соединен с соответствующим n-м информационным входом коммутатора, управляющий вход которого соединен с выходом дешифратора, первый вход которого соединен с первым выходом первого счетчика импульсов, формирователь сигнала «Отклонение вверх» и формирователь сигнала «Отклонение вниз», объединенные входы которых подключены к выходу коммутатора, кнопку «Пуск», первый контакт которой подключен к источнику питания устройства, а второй подключен к первому входу элемента ИЛИ и S входу RS-триггера, прямой выход которого соединен с управляющим входом первого счетчика импульсов и вторым входом формирователя периода последовательности импульсов, второй выход первого счетчика импульсов подключен ко второму входу первого генератора импульсов и входам второго генератора импульсов и второго формирователя единичного импульса, выход которого подключен к информационному входу регистра сдвига, второй выход которого подключен к R входу RS-триггера, инверсный выход которого соединен со вторым входом элемента ИЛИ, первым входом третьего элемента И, управляющим входом второго блока элементов И и вторым входом генератора счетной частоты, выход которого подключен к информационному входу первого счетчика импульсов и второму входу третьего элемента И, выход которого соединен со вторым входом второго счетчика импульсов и с управляющим входом блока памяти, выход которого подключен ко второму входу дешифратора, выход которого подключен к первому управляющему входу блока реверсивных регистров, суммирующий информационный вход которого соединен с выходом первого элемента И, управляющий вход которого подключен к выходу формирователя сигнала «Отклонение вверх», вычитающий информационный вход блока реверсивных регистров соединен с выходом второго элемента И, управляющий вход которого подключен к выходу формирователя сигнала «Отклонение вниз», а информационные входы первого и второго элементов И соединены с выходом первого генератора импульсов, первый вход которого соединен с входом блока установки в исходное состояние и подключен к выходу первого формирователя единичного импульса, вход которого соединен с выходом элемента ИЛИ, а выход блока установки в исходное состояние подключен ко второму управляющему входу блока реверсивных регистров, выход которого подключен к информационному входу первого блока элементов И, первый вход блока индикации соединен с входом блока идентификации сигнала тревоги, выход которого соединен с первым входом второго счетчика импульсов, выход которого соединен с входом блока анализа двухэтапного поиска сигнала, выход которого соединен с первым входом формирователя периода последовательности импульсов, выход которого подключен к первому входу генератора счетной частоты, второй вход блока индикации соединен с выходом второго блока элементов И, информационный вход которого подключен к выходу блока памяти, первый вход которого соединен с выходом шифратора, вход которого подключен к выходу первого блока элементов И, управляющий вход которого соединен с первым выходом регистра сдвига, тактовый вход которого подключен к выходу второго генератора импульсов, дополнительно введен контроллер, вход которого соединен с выходом блока реверсивных регистров, а выход соединен с первым входом блока индикации. При этом контроллер состоит из делителя, вход которого является входом контроллера, а первый выход соединен с входом счетчика, выход которого соединен с входом элемента памяти, выход которого соединен с первым входом элемента сравнения, второй вход которого соединен с выходом элемента задания коэффициентов, а выход соединен с вторым входом элемента умножения, первый вход которого соединен со вторым выходом делителя, а выход элемента умножения соединен с первым входом управляемого делителя, второй вход которого соединен с выходом генератора тактовых импульсов, а выход является выходом контроллера.

Благодаря перечисленной новой совокупности существенных признаков заявляемого устройства для сигнализации отклонения параметров при допусковом контроле обеспечивается повышение быстродействия двухэтапной процедуры поиска сигнала тревоги в системе многоканального контроля путем изменения периодичности контроля параметров в зависимости от скорости их дрейфа, а также адаптивного изменения длительности предварительного просмотра каналов на первом этапе поиска сигнала тревоги.

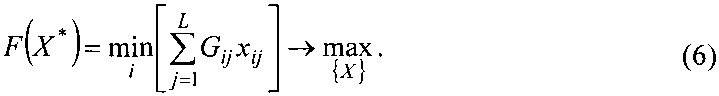

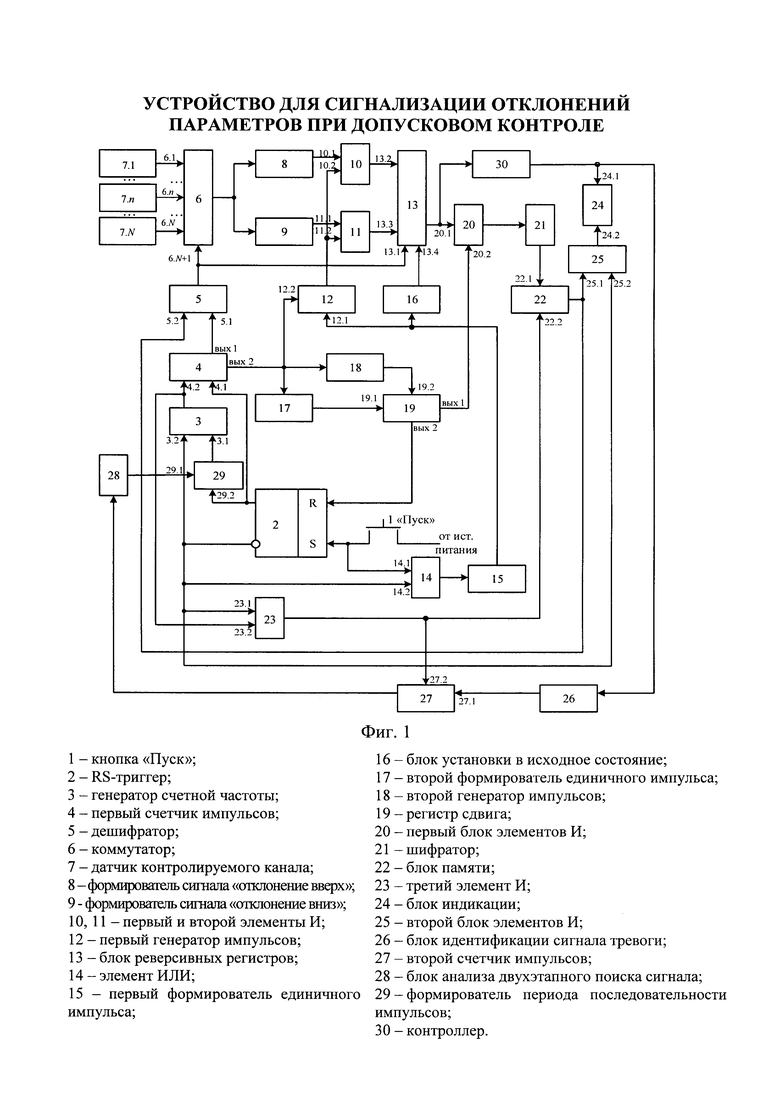

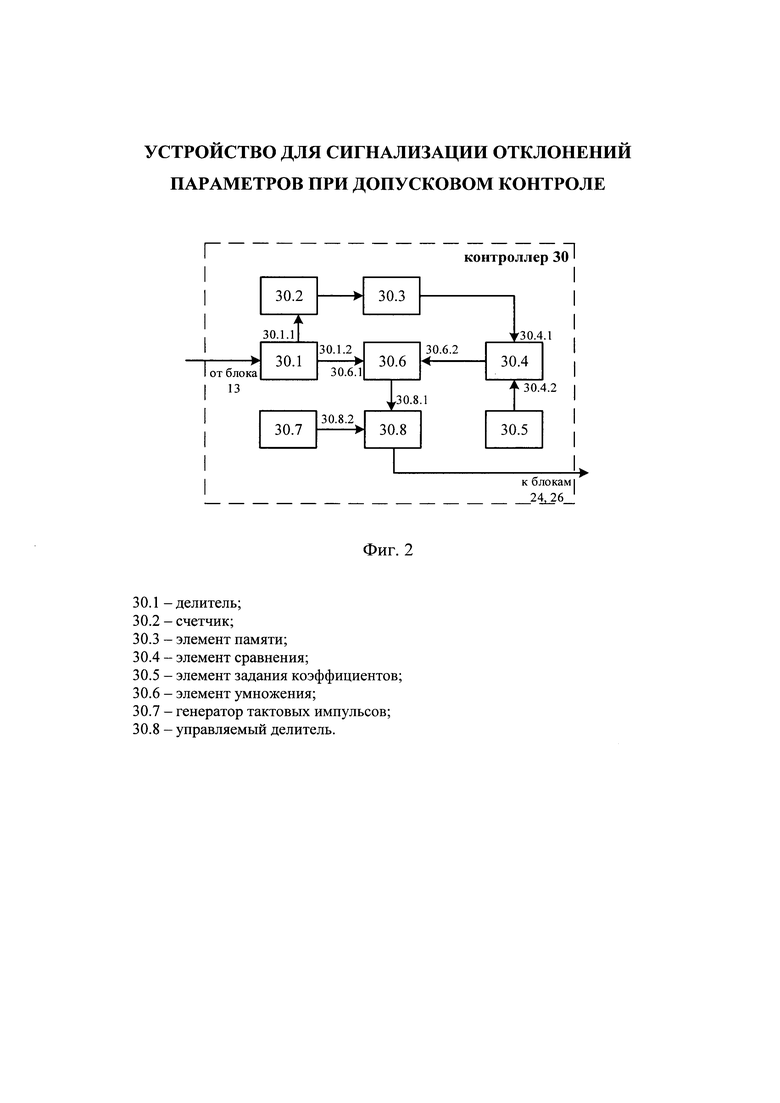

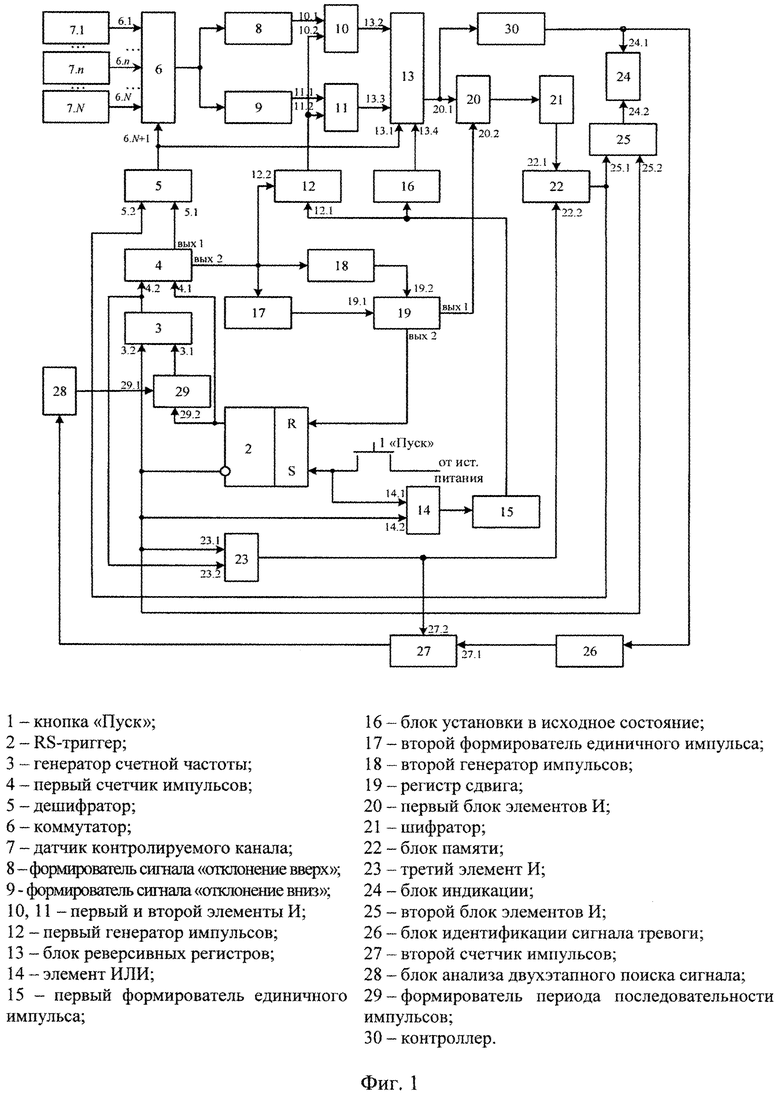

Заявленное устройствопоясняется чертежами, на которых показаны:

на фиг. 1 - структурная схема устройства для сигнализации отклонений параметра при допусковом контроле;

на фиг. 2 - функциональная схема контроллера;

на фиг. 3 - динамика скорости выхода контролируемого параметра за допустимые пределы: а) при отклонении «Вверх»; б) при отклонении «Вниз».

Заявленное устройство для сигнализации отклонений параметров при допусковом контроле, показанное на фиг. 1, содержит: кнопку «Пуск»1; RS-триггер 2; генератор счетной частоты 3; первый 4 и второй 27 счетчики импульсов; дешифратор 5; коммутатор 6; датчики контролируемых каналов 7.1, 7.2, …, 7.n, …, 7.N; формирователи сигнала «отклонение вверх» 8 и сигнала «отклонение вниз» 9; первый 10, второй 11 и третий 23 элементы И; первый 12 и второй 18 генераторы импульсов; блок реверсивных регистров 13; элемент ИЛИ 14; первый 15 и второй 17 формирователи единичного импульса; блок установки в исходное состояние 16; регистр сдвига 19; первый 20 и второй 25 блоки элементов И; шифратор 21; блок памяти 22; блок индикации 24; блок идентификации сигнала тревоги 26; блок анализа двухэтапного поиска сигнала 28; формирователь периода последовательности импульсов 29; контроллер 30.

При этом выходы датчиков контролируемых каналов 7.1, …, 7.n, …, 7.N соединены с соответствующими информационными входами (6.1, …, 6.n, …, 6.N) коммутатора 6, управляющий вход 6.N+1 которого соединен с выходом дешифратора 5, первый вход 5.1 которого соединен с первым выходом первого счетчика импульсов 4, объединенные входы формирователя сигнала «Отклонение вверх» 8 и формирователь сигнала «Отклонение вниз» 9 подключены к выходу коммутатора 6, первый контакт кнопки «Пуск» 1 подключен к источнику питания устройства, а второй - к первому входу 14.1 элемента ИЛИ 14 и S входу RS-триггера 2, прямой выход которого соединен с управляющим входом 4.1 первого счетчика импульсов 4 и вторым входом 29.2 формирователя периода последовательности импульсов 29, второй выход первого счетчика импульсов 4 подключен ко второму входу 12.2 первого генератора импульсов 12 и входам второго генератора импульсов 18 и второго формирователя единичного импульса 17, выход которого подключен к информационному входу 19.1 регистра сдвига 19, второй выход которого подключен к R входу RS-триггера 2, инверсный выход которого соединен со вторым входом 14.2 элемента ИЛИ 14, первым входом 23.1 третьего элемента И 23, управляющим входом 25.2 второго блока элементов И 25 и вторым входом 3.2 генератора счетной частоты 3, выход которого подключен к информационному входу 4.2 первого счетчика импульсов 4 и второму входу 23.2 третьего элемента И 23, выход которого соединен со вторым входом 27.2 второго счетчика импульсов 27 и с управляющим входом 22.2 блока памяти 22, выход которого подключен ко второму входу 5.2 дешифратора 5, выход которого подключен к первому управляющему входу 13.1 блока реверсивных регистров 13, суммирующий информационный вход 13.2 которого соединен с выходом первого элемента И 10, управляющий вход 10.1 которого подключен к выходу формирователя сигнала «Отклонение вверх» 8, вычитающий информационный вход 13.3 блока реверсивных регистров 13 соединен с выходом второго элемента И 11, управляющий вход 11.1 которого подключен к выходу формирователя сигнала «Отклонение вниз» 9, а информационные входы 10.2 и 11.2 первого 10 и второго 11 элементов И соединены с выходом первого генератора импульсов 12, первый вход 12.1 которого соединен с входом блока установки в исходное состояние 16 и подключен к выходу первого формирователя единичного импульса 15, вход которого соединен с выходом элемента ИЛИ 14, а выход блока установки в исходное состояние 16 подключен ко второму управляющему входу 13.4 блока реверсивных регистров 13, выход которого подключен к информационному входу 20.1 первого блока элементов И 20 и входу контроллера 30, выход которого подключен к первому входу 24.1 блока индикации 24 и соединен с входом блока идентификации сигнала тревоги 26, выход которого соединен с первым входом 27.1 второго счетчика импульсов 27, выход которого соединен с входом блока анализа двухэтапного поиска сигнала 28, выход которого соединен с первым входом 29.1 формирователя периода последовательности импульсов 29, выход которого подключен к первому входу 3.1 генератора счетной частоты 3, второй вход 24.2 блока индикации 24 соединен с выходом второго блока элементов И 25, информационный вход 25.1 которого подключен к выходу блока памяти 22, первый вход которого 22.1 соединен с выходом шифратора 21, вход которого подключен к выходу первого блока элементов И 20, управляющий вход которого 20.2 соединен с первым выходом регистра сдвига 19, тактовый вход которого 19.2 подключен к выходу второго генератора импульсов 18.

Кнопка «Пуск» 1 предназначена для подачи напряжения на RS-триггер 2 и включения устройства от источника питания.

RS-триггер 2 предназначен для запуска генератора счетной частоты 3.

Генератор счетной частоты 3 предназначен для формирования счетных импульсов с периодом τ, необходимых для опроса анализируемых каналов и вынесения решения о наличии сигналов тревоги в них.

Первый счетчик импульсов 4 предназначен для подсчета числа импульсов и присвоения им соответствующего номера, для последующего вынесения решения о наличии сигнала тревоги в анализируемом канале.

Дешифратор 5 предназначен для преобразования кодовой комбинации в определенное количество «единиц», пропорциональное числу импульсов (соответствующих номеров), т.е. подачи разрешающего сигнала на управляющий вход соответствующего из регистров блока 13.

Коммутатор 6 предназначен для поочередного подключения датчиков к формирователю сигналов «отклонение вверх» 8 либо формирователю сигналов «отклонение вниз» 9, в зависимости от поступающего на управляющий вход сигнала с дешифратора 5.

Датчики контролируемых каналов (7.1, …, 7.n, …, 7.N) предназначены для измерения (регистрации и передачи) физической величины параметра в различных технологических процессах.

Формирователь сигнала «отклонение вверх» 8 предназначен для сравнения значения параметра сигнала с уровнем X верхнего порога xi.

Формирователь сигнала «отклонение вниз» 9 предназначен для сравнения значения параметра сигнала с уровнем X нижнего порога xj.

Первый элемент И 10 предназначен для пропуска импульсов с выхода первого генератора импульсов 12 на суммирующий информационный вход одного из регистров блока реверсивных регистров 13, в случае, если X>xi.

Второй элемент И 11 предназначен для пропуска тактовых импульсов с выхода первого генератора импульсов 12 на вычитающий вход одного из регистров блока реверсивных регистров 13, в случае, если X<xj.

Первый генератор импульсов 12 предназначен для подачи на информационные входы первого и второго элементов И тактовых импульсов.

Блок реверсивных регистров 13 предназначен для записи определенного количества логических единиц, начиная с первых триггеров данных регистров.

Элемент ИЛИ 14 предназначен для подачи напряжения с инверсного выхода RS-триггера 2 на вход первого формирователя единичного импульса 15.

Первый формирователь единичного импульса 15 предназначен для формирования единичного импульса.

Блок установки в исходное состояние 16 предназначен для установки в исходное состояние реверсивных регистров блока реверсивных регистров 13.

Второй формирователь единичного импульса 17 предназначен для формирования повторно единичного импульса, в зависимости от сигналов со счетчика импульсов 4 и первого генератора импульсов 12.

Второй генератор импульсов 18 предназначен для выработки сигнала и передачи его на тактовый вход регистра сдвига 19, в случае поступления сигнала со второго выхода первого счетчика импульсов 4 на вход генератора.

Регистр сдвига 19 предназначен для формирования «опрашивающих» импульсов, формируемых в результате взаимодействия выходного импульса, поступающего со второго генератора импульсов 18 и импульса, поступающего со второго формирователя единичного импульса 17.

Первый блок элементов И 20 предназначен для сопоставления «опрашивающих» импульсов, поступающих с выхода регистра сдвига 19 импульсам с различным числом логических единиц, поступающих с блока реверсивных регистров 13, в результате анализа триггеров.

Шифратор 21 предназначен для формирования информации (кодовой комбинации) о номерах датчиков, измеривших сигналы от максимального до минимального уровней.

Блок памяти 22 предназначен для записи информации (о номерах датчиков), поступающей с шифратора в ячейки памяти, а также доступа к записанной информации в ячейках памяти дешифратора 5.

Третий элемент И 23 предназначен для пропуска импульсов с выхода генератора счетной частоты 3 на управляющий вход блока памяти 22, предназначенных для обеспечения последовательного подключения ячеек памяти блока памяти 22 ко второму входу дешифратора 5.

Блок индикации 24 предназначен для отображения результата текущего контроля состояния каналов передачи информации, анализируемых на втором этапе, индикации номеров контролируемых каналов от датчиков 7.1, …, 7.n, …, 7.N.

Второй блок элементов И 25 предназначен для пропуска импульсов о номерах датчиков на блок индикации 24, в зависимости от сигнала с инверсного выхода RS-триггера 2.

Блока идентификации сигнала тревоги 26 предназначен для распознавания сигнала, который превысил заданный пороговый уровень.

Второй счетчик импульсов 27 предназначен для подсчета числа каналов, вероятность нахождения сигналов тревоги в которых максимальна, анализируемых на втором этапе контроля.

Блок анализа двухэтапного поиска сигнала 28 предназначен для осуществления выбора сигнала по управлению длительности предварительного этапа контроля.

Формирователь периода последовательности импульсов 29 предназначен для формирования периода следования Т (T>>τ), который равен времени, достаточному для полного анализа сигнала, измеряемого любым из датчиков 7.1, …, 7.n, …, 7.N.

Схемы построения логических элементов И (10, 11, 23), ИЛИ (14), блоков элементов И (20, 25), RS-триггера (2), счетчиков импульсов (4, 27), шифратора (21) и дешифратора (5), коммутатора (6), регистра сдвига (19) и блок реверсивных регистров (13) известны и описаны, например, в книге [1].

Схемы построения генераторов счетной частоты (3) и импульсов (12, 18); датчиков контролируемых каналов (7.1, …, 7.n, …, 7.N); формирователей сигналов (8, 9), единичных импульсов (15, 17) и периода последовательности импульсов (29); блоков памяти (22), индикации (24), идентификации сигнала тревоги (26), установки в исходное состояние (16) и анализа (28) могут быть реализованы различными способами, например, как описано в книгах [2, 3].

Контроллер 30 предназначен для периодичного контроля наблюдаемых изменяющихся параметров объекта контроля. Он может быть реализован различным способом, например, как показано на фиг. 2.

Контроллер 30 состоит из делителя 30.1, счетчика 30.2, элементов памяти 30.3, сравнения 30.4, задания коэффициентов 30.5, умножения 30.6, а также генератора тактовых импульсов 30.7 и управляемого делителя 30.8.

При этом вход делителя 30.1 является входом контроллера 30, первый выход 30.1.1 делителя 30.1 соединен с входом счетчика 30.2, выход которого соединен с входом элемента памяти 30.3, выход которого соединен с первым входом 30.4.1 элемента сравнения 30.4, второй вход которого 30.4.2 соединен с выходом элемента задания коэффициентов 30.5, а выход соединен со вторым входом 30.6.2 элемента умножения 30.6, первый вход которого 30.6.1 соединен со вторым выходом 30.1.2 делителя 30.1, а выход соединен с первым входом 30.8.1 управляемого делителя 30.8, второй вход которого 30.8.2 соединен с выходом генератора тактовых импульсов 30.7, а выход является выходом контроллера 30.

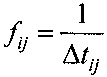

Делитель 30.1 предназначен для получения частоты опроса сигнала (заявки)  для Δtij времени, необходимого для достижения параметра сигнала допустимого предела, где i=1, 2, …, Y - принимаемые им значения при отклонении вверх, a j=1, 2, …, М - принимаемые им значения при отклонении вниз (фиг. 3).

для Δtij времени, необходимого для достижения параметра сигнала допустимого предела, где i=1, 2, …, Y - принимаемые им значения при отклонении вверх, a j=1, 2, …, М - принимаемые им значения при отклонении вниз (фиг. 3).

Счетчик 30.2 предназначен для подсчета сигналов с быстроменяющимися параметрами.

Элемент памяти 30.3 предназначен для запоминания очередного результата суммирования сигналов с быстроменяющимися параметрами.

Элемент сравнения 30.4 предназначен для сравнения абсолютных значений времени выхода сигналов различных приоритетов за допустимые уровни.

Элемент задания коэффициентов 30.5 предназначен для подачи постоянных значений (констант) пороговых уровней на элемент сравнения 30.4.

Элемент умножения 30.6 предназначен для перемножения сигнала, полученного в процессе деления с делителя 30.1, и результата сравнения абсолютных значений времени выхода сигналов различных приоритетов за допустимые уровни с элемента сравнения 30.4.

Генератор тактовых импульсов 30.7 предназначен для генерации сигнала задающего последовательность обработки информации, и синхронизации работы узлов устройства.

Управляемый делитель 30.8 предназначен для формирования импульсов управления периодичностью контроля различных параметров объекта.

Схемы построения делителя 30.1, счетчика 30.2, элемента сравнения 30.4, элемента умножения 30.6 и управляемого делителя 30.8 известны и описаны, например, в книге [1].

Схемы построения генератора тактовых импульсов 30.7, а также элементов памяти 30.3 и задания коэффициентов 30.5 могут быть реализованы различными способами, например, как описано в книгах [2, 3].

Заявленное устройство для сигнализации отклонения параметров при допусковом контроле работает следующим образом.

При нажатии кнопки «Пуск» 1 (см. фиг. 1) на S вход RS-триггера 2 подается напряжение и RS-триггер 2 переводится в состояние логической единицы. Напряжение с прямого выхода RS-триггера 2 через формирователь периода последовательности импульсов 29 подается на первый вход генератора счетной частоты 3 и управляющий вход первого счетчика импульсов 4 для обеспечения его функционирования. С выхода генератора счетной частоты 3 через формирователь периода последовательности импульсов 29 на информационный вход первого счетчика импульсов 4 поступают импульсы с периодом τ, который намного меньше времени, необходимого для окончательного вынесения решения о наличии сигнала тревоги в анализируемом канале.

Сигнал, соответствующий номеру поступающего импульса, с первого выхода первого счетчика импульсов 4 через дешифратор 5 подается на управляющий вход коммутатора 6 для поочередного подключения датчиков 7.1, …, 7.n, …, 7.N к формирователям сигналов 8 и 9 соответственно «Отклонение вверх» и «Отклонение вниз». Измеренный одним из датчиков 7.1, …, 7.n, …, 7.N сигнал с уровнем X сравнивается с параметром сигнала верхнего порогового уровня xi в формирователе сигнала «Отклонение вверх» 8 и с параметром сигнала нижнего порогового уровня xj в формирователе сигнала «Отклонение вниз» 9.

В случае, если Х>xi, то с выхода формирователя сигнала «Отклонение вверх» 8 сигнал открывает первый элемент И 10 для поступления импульсов с выхода первого генератора импульсов 12 на суммирующий информационный вход одного из регистров блока реверсивных регистров 13; при X<xj сигнал с выхода формирователя сигнала «Отклонение вниз» 9 открывает второй элемент И 11 для обеспечения прохождения тактовых импульсов с генератора импульсов 12 на вычитающий информационный вход одного из реверсивных регистров блока реверсивных регистров 13; если xi≤X≤xi, то на выходах формирователей сигнала «Отклонение вверх» 8 и «Отклонение вниз» 9 сигналы отсутствуют. При этом к выходу элементов И 10 или элементов И 11 подключается тот регистр блока реверсивных регистров 13, номер которого соответствует номеру анализируемого датчика 7.n. Это обеспечивается за счет подачи разрешающего сигнала на управляющий вход соответствующего из регистров блока реверсивных регистров 13 с выхода дешифратора 5.

Исходное состояние реверсивных регистров блока реверсивных регистров 13 обеспечивается при нажатии кнопки «Пуск» 1 и подаче напряжения через элемент ИЛИ 14 на вход первого формирователя единичного импульса 15. Импульс с выхода формирователя единичного импульса 15 поступает на вход блока установки в исходное состояние 16, который обеспечивает запись в реверсивные регистры блока реверсивных регистров 13 определенного количества логических единиц, начиная с первых триггеров данных регистров. Кроме того, импульс с формирователя единичного импульса 15, подаваемый на первый вход первого генератора импульсов 12, обеспечивает его включение.

Если импульсы с первого генератора импульсов 12 поступают на суммирующий информационный вход (в случае Х>xi), то число логических единиц в соответствующем реверсивном регистре блока реверсивных регистров 13 увеличивается, если импульсы поступают на вычитающий информационный вход (при X<xj), то число логических единиц в регистре блока реверсивных регистров 13 уменьшается, при соотношении xj≤Х≤xi число логических единиц не изменяется (так как в этом случае оба элемента И 10 и 11 будут закрыты). Таким образом, к концу первого этапа контроля во всех реверсивных регистрах блока реверсивных регистров 13 будет записано количество логических единиц, пропорциональное уровням сигналов на выходе соответствующих датчиков 7.1, …, 7.n, …, 7.N.

После подсчета n-го импульса первым счетчиком импульсов 4 с его второго выхода поступит сигнал на второй вход первого генератора импульсов 12 для его остановки, а также на входы второго формирователя единичного импульса 17 и второго генератора импульсов 18. Выходной импульсо второго формирователя единичного импульса 17 поступает на информационный вход регистра 19 сдвига в виде логической единицы, которая при подаче на тактовые входы данного регистра импульсов с выхода второго генератора импульсов 18 продвигается по триггерам регистра 19.

Опрашивающие импульсы с выхода триггеров регистра сдвига 19 последовательно поступают на управляющий вход первого блока элементов И 20, информационный вход которого соединен с выходами триггеров соответствующих реверсивных регистров блока реверсивных регистров 13. Опрос регистров блока реверсивных регистров 13 начинается с анализа состояния последних триггеров одновременного для всех регистров блока реверсивных регистров 13, затем анализируются предпоследние триггеры регистров блока реверсивных регистров 13 и т.д. На шифратор 21 через блок элементов И 20 вначале поступит импульс с того реверсивного регистра блока реверсивных регистров 13, в триггерах которого наибольшее число логических единиц, что соответствует максимальному уровню сигнала из числа измеренных на первом этапе контроля.

С выхода шифратора 21 на вход блока памяти 22 вначале поступает и записывается в первую ячейку памяти информация о номере того датчика 7.n, который измерил сигнал с максимальным уровнем. Во вторую ячейку блока памяти 22 записывается номер датчика 7.n, измерившего сигнал с несколько меньшим уровнем сигнала, и т.д. Таким образом, первый этап контроля заканчивается ранжировкой номеров канальных датчиков 7.1, …, 7.n, …, 7.N в блоке памяти 22 в зависимости от вероятности нахождения сигналов тревоги в контролируемых каналах.

При прохождении единичного импульса через все триггеры регистра сдвига 19 на втором его выходе появляется сигнал, который поступает на R вход RS-триггера 2 и перебрасывает данный триггер в состояние логического нуля. Первый счетчик импульсов 4, подключенный к прямому выходу RS-триггера 2, выключается. Кроме того, напряжение с инверсного выхода RS-триггера 2, подаваемое через элемент ИЛИ 14 на первый формирователь единичного импульса 15, обеспечивает формирование единичного импульса, включающего первый генератор импульсов 12 и устанавливающего (с помощью блока установки в исходное состояние 16) реверсивные регистры блока реверсивных регистров 13 в исходное состояние.

Напряжение с инверсного выхода RS-триггера 2 подается также на второй вход генератора счетной частоты 3. С выхода генератора счетной частоты 3 через открытый элемент И 23 на управляющий вход блока памяти 22 поступают импульсы, период следования Т (T>>τ) которых равен времени, достаточному для полного анализа сигнала, измеряемого любым из датчиков 7.1, …, 7.n, …, 7.N. Данные импульсы обеспечивают последовательное подключение ячеек памяти блока 22 ко второму входу дешифратора 5, обеспечивая при этом контроль состояния тех каналов, вероятность нахождения сигналов тревоги в которых максимальна.

По аналогии с первым этапом контроля коммутатор 6 осуществляет подключение датчиков 7.1, …, 7.n, …, 7.N к формирователям сигналов «отклонение вверх» 8 и «отклонение вниз» 9. При этом в первую очередь подключается датчик, номер которого записан в первую ячейку памяти блока 22, так как в сигнале с его выхода наибольшая вероятность тревожной информации, затем к формирователям сигналов «отклонение вверх» 8 и «отклонение вниз» 9 подключается датчик, номер которого записан во второй ячейке блока памяти 22, и т.д.

В формирователях сигналов «отклонение вверх» 8 и «отклонение вниз» 9 осуществляется сравнение уровней X измеренных сигналов с пороговыми уровнями: верхним xi и нижним xj. Если Х>xi, то с формирователя сигнала «Отклонение вверх» 8, сигнал, подаваемый на управляющий вход элемента И 10, обеспечит прохождение тактовых импульсов с выхода первого генератора импульсов 12 на суммирующий информационный вход одного из реверсивных регистров блока реверсивных регистров 13. Число логических единиц при этом в регистре блока реверсивных регистров 13 будет увеличено на число поступивших тактовых импульсов. Выбор реверсивного регистра, соответствующего номеру анализируемого канала, обеспечивается за счет подачи сигнала на первый управляющий вход блока реверсивных регистров 13 с выхода дешифратора 5, на второй вход которого поступает информация с выхода блока памяти 22.

При X<xj сигнал, подаваемый с формирователя сигнала «Отклонение вниз» 9 на управляющий вход элемента И 11, обеспечит уменьшение числа логических единиц в регистре блока реверсивных регистров 13 на число тактовых импульсов, поступающих с первого генератора импульсов 12 на вычитающий вход реверсивного регистра блока реверсивных регистров 13.

Тактовые импульсы, в соответствии со скоростью изменения параметра, с блока реверсивных регистров 13 поступают в делитель 30.1 (см. фиг. 2) контроллера 30. Результаты расчета  с первого выхода делителя 30.1 поступают на вход счетчика 30.2, в котором в течение периода T0 осуществляется подсчет

с первого выхода делителя 30.1 поступают на вход счетчика 30.2, в котором в течение периода T0 осуществляется подсчет  .

.

По окончании длительности периода T0 результат суммирования с счетчика 30.2 подается на элемент памяти 30.3. При этом счетчик 30.2 обнуляется и готов к приему очередной информации.

Выход элемента памяти 30.3 подключен к первому входу элемента сравнения 30.4, осуществляющего сравнение абсолютных значений времени выхода сигналов различных приоритетов за допустимые уровни (см. фиг. 3). Сравнение указанных значений показывает, что чем меньше времени до достижения допустимого предела контролируемым параметром сигнала, тем выше его приоритет. На второй вход элемента сравнения 30.4 поступает сигнал с элемента задания коэффициентов 30.5. Элемент умножения 30.6 управляется выходом элемента сравнения 30.4, соединенного со вторым входом элемента умножения 30.6, на первый вход которого подается со второго выхода делителя 30.1 текущее значение величины  .

.

Результаты расчета с выхода элемента умножения 30.6 подаются на информационный вход 30.8.1 управляемого делителя 30.8 для формирования импульсов управления периодичностью контроля различных параметров, а на его управляющий вход 30.8.2 с выхода генератора тактовых импульсов 30.7 подается управляющий сигнал, задающий последовательность обработки информации, и синхронизации работы блоков устройства. Таким образом, контроллер 30 позволяет обеспечивать контроль динамики скорости выхода изменяемых параметров различных приоритетов за допустимые пределы уже на первом этапе контроля.

Результат текущего контроля состояния каналов, анализируемых на втором этапе, отражается в блоке индикации 24, первый вход которого подключен к выходу контроллера 30. Индикация номера контролируемых каналов (датчиков 7.1, …, 7.n, …, 7.N) обеспечивается за счет подачи информации на второй вход блока индикации 24 с выхода второго блока элементов И 25, информационный вход которого подключен к выходу блока памяти 22, а управляющий вход - к инверсному выходу RS-триггера 2.

Таким образом, на втором этапе контроля в первую очередь анализируется состояние тех каналов, вероятность нахождения сигналов тревоги в которых максимальна (по результатам первого этапа контроля). Количество каналов, анализируемых на втором этапе контроля, подсчитывает второй счетчик импульсов 27, информационный вход которого подключен к выходу третьего элемента И 23. Сигнал тревоги идентифицируется блоком идентификации сигнала тревоги 26 (например, в случае превышения заданного порогового уровня), с выхода которого на управляющий вход второго счетчика импульсов 27 поступает сигнал для его остановки. Результат счета с выхода второго счетчика импульсов 27 подается на вход блок анализа двухэтапного поиска сигнала 28. Блок анализа двухэтапного поиска сигнала 28 выбирает сигнал по управлению длительностью первого этапа, подаваемый на управляющий вход формирователя периода последовательности импульсов 29.

Чем большее количество каналов было просмотрено на втором этапе контроля до обнаружения сигнала тревоги, тем больше следует увеличить длительность первого (предварительного) этапа, чтобы повысить вероятность нахождения результата измерения в заданном допусковом интервале xj÷xi, а следовательно, вероятность присутствия сигнала тревоги в первом (после ранжировки) канале, номер которого записан в блоке памяти 22. Если второй этап регулярно ограничивается контролем только первого (после ранжировки) канала, то это может свидетельствовать об избыточно большой длительности первого этапа контроля.

Реализацию второго этапа контроля, в течение которого в первую очередь анализируется состояние тех каналов, в которых вероятность нахождения сигналов тревоги максимальна, т.е. находящемся в наихудших условиях (либо с минимальным значением допустимой вероятности ошибки pош.доп), можно представить математически.

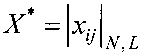

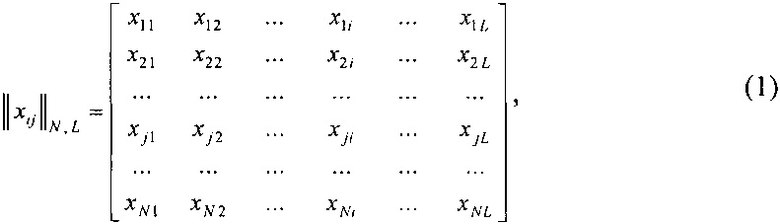

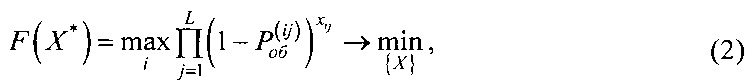

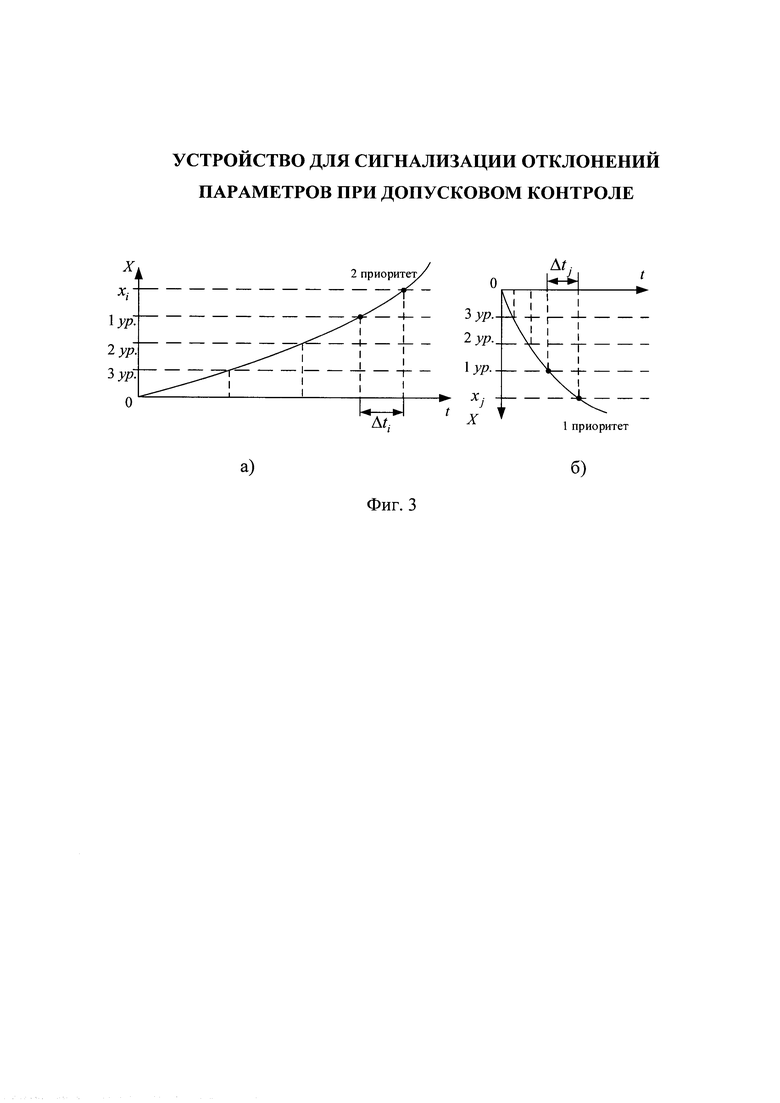

На множестве {X} требуется найти такую матрицу распределения сигналов тревоги среди каналов  , где

, где

для которой:

при условии, что распределению подлежат все L сигналов тревоги в N каналах, и каждый вариант тревоги (превышения параметром заданного уровня) может быть назначен в один канал ( - вероятность обслуживания (идентификации тревоги) сигналов по верхнему или нижнему пределу), то есть

- вероятность обслуживания (идентификации тревоги) сигналов по верхнему или нижнему пределу), то есть

При введении обозначения

решение задачи равносильно нахождению матрицы X*, такой что

Таким образом, заявленное устройство для сигнализации отклонений параметров при допусковом контроле, по сравнению с известным, позволит повысить быстродействие двухэтапного поиска сигнала тревоги (за счет определения приоритета поступившего сигнала) в системе многоканального контроля с изменяющейся погрешностью измерений путем периодичности контроля наблюдаемых изменяющихся параметров в зависимости от скорости их изменения Δtij и тем самым своевременно обнаружить предаварийную ситуацию различных объектов.

Литература

1. Шило В.Л. Популярные цифровые микросхемы: Справочник. 2-е изд. - Челябинск: Металлургия, Челябинское отд., 1989. - 352 с.

2. Титце У., Шенк К. Полупроводниковая схемотехника: в 2 т.: пер. с нем. - Т. 1. - М.: Додэка - XXI, 2008. - 832 с.

3. Титце У., Шенк К. Полупроводниковая схемотехника: в 2 т.: пер. с нем. - Т. 2. - М.: Додэка - XXI, 2008. - 942 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2820839C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2020 |

|

RU2787747C2 |

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2817045C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2022 |

|

RU2795501C1 |

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ | 2024 |

|

RU2826860C1 |

| Устройство для передачи информации | 1989 |

|

SU1736001A1 |

| Устройство для допускового контроля фазочастотных характеристик четырехполюсников | 1989 |

|

SU1661681A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| ДВУЗОННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2799658C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ | 2022 |

|

RU2793860C1 |

Изобретение относится к области релейной защиты и автоматики и может быть применено в системах многоканального контроля и телесигнализации для различных технологических процессов. Устройство сигнализации отклонений параметра при допусковом контроле состоит из: кнопки «Пуск»; RS-триггера; трех элементов И и одного элемента ИЛИ; двух блоков элементов И; генератора счетной частоты; двух счетчиков импульсов; шифратора и дешифратора; коммутатора; датчиков контролируемых каналов; формирователей сигналов «отклонение вверх» и «отклонение вниз»; формирователя периода последовательности импульсов; двух генераторов импульсов; двух формирователей единичных импульсов; регистра сдвига; блоков памяти, индикации, реверсивных регистров, установки в исходное состояние, идентификации сигнала тревоги, анализа двухэтапного поиска сигнала; контроллера. Новым в устройстве является контроллер, предназначенный для периодичного контроля наблюдаемых изменяющихся параметров объектов контроля и состоящий из делителя, счетчика, элемента памяти, элемента сравнения, элемента задания коэффициентов, элемента умножения, генератора тактовых импульсов, управляемого делителя, а также совокупности новых связей. Предлагаемое устройство позволит повысить быстродействие двухэтапного поиска сигнала тревоги в системе многоканального контроля путем периодичности контроля параметров в зависимости от скорости их изменения, а также адаптивного изменения длительности предварительного просмотра каналов на первом этапе поиска сигнала тревоги. 1 з.п. ф-лы, 3 ил.

1. Устройство для сигнализации отклонений параметра при допусковом контроле, содержащее N≥2 датчиков, выход каждого n-го, n=1, 2, …, N, из которых соединен с соответствующим n-м информационным входом коммутатора, управляющий вход которого соединен с выходом дешифратора, первый вход которого соединен с первым выходом первого счетчика импульсов, формирователь сигнала «Отклонение вверх» и формирователь сигнала «Отклонение вниз», объединенные входы которых подключены к выходу коммутатора, кнопку «Пуск», первый контакт которой подключен к источнику питания устройства, второй подключен к первому входу элемента ИЛИ и S входу RS-триггера, прямой выход которого соединен с управляющим входом первого счетчика импульсов и вторым входом формирователя периода последовательности импульсов, второй выход первого счетчика импульсов подключен ко второму входу первого генератора импульсов и входам второго генератора импульсов и второго формирователя единичного импульса, выход которого подключен к информационному входу регистра сдвига, второй выход которого подключен к R входу RS-триггера, инверсный выход которого соединен со вторым входом элемента ИЛИ, первым входом третьего элемента И, управляющим входом второго блока элементов И и вторым входом генератора счетной частоты, выход которого подключен к информационному входу первого счетчика импульсов и второму входу третьего элемента И, выход которого соединен со вторым входом второго счетчика импульсов и с управляющим входом блока памяти, выход которого подключен ко второму входу дешифратора, выход которого подключен к первому управляющему входу блока реверсивных регистров, суммирующий информационный вход которого соединен с выходом первого элемента И, управляющий вход которого подключен к выходу формирователя сигнала «Отклонение вверх», вычитающий информационный вход блока реверсивных регистров соединен с выходом второго элемента И, управляющий вход которого подключен к выходу формирователя сигнала «Отклонение вниз», а информационные входы первого и второго элементов И соединены с выходом первого генератора импульсов, первый вход которого соединен с входом блока установки в исходное состояние и подключен к выходу первого формирователя единичного импульса, вход которого соединен с выходом элемента ИЛИ, а выход блока установки в исходное состояние подключен ко второму управляющему входу блока реверсивных регистров, выход которого подключен к информационному входу первого блока элементов И, первый вход блока индикации соединен с входом блока идентификации сигнала тревоги, выход которого соединен с первым входом второго счетчика импульсов, выход которого соединен с входом блока анализа двухэтапного поиска сигнала, выход которого соединен с первым входом формирователя периода последовательности импульсов, выход которого подключен к первому входу генератора счетной частоты, второй вход блока индикации соединен с выходом второго блока элементов И, информационный вход которого подключен к выходу блока памяти, первый вход которого соединен с выходом шифратора, вход которого подключен к выходу первого блока элементов И, управляющий вход которого соединен с первым выходом регистра сдвига, тактовый вход которого подключен к выходу второго генератора импульсов, отличающееся тем, что дополнительно введен контроллер, вход которого соединен в выходом блока реверсивных регистров, а выход соединен с первым входом блока индикации.

2. Устройство по п. 1, отличающееся тем, что контроллер состоит из делителя, вход которого является входом контроллера, а первый выход соединен с входом счетчика, выход которого соединен с входом элемента памяти, выход которого соединен с первым входом элемента сравнения, второй вход которого соединен с выходом элемента задания коэффициентов, а выход соединен с вторым входом элемента умножения, первый вход которого соединен со вторым выходом делителя, а выход элемента умножения соединен с первым входом управляемого делителя, второй вход которого соединен с выходом генератора тактовых импульсов, а выход является выходом контроллера.

| Механическая тележка для штучных грузов | 1961 |

|

SU140746A1 |

| Баркас кожевенного производства | 1946 |

|

SU68736A1 |

| Устройство для сигнализации отклонений параметра при допусковом контроле | 1985 |

|

SU1357991A1 |

| US 20110260851 A1, 27.10.2011. | |||

Авторы

Даты

2017-04-28—Публикация

2016-03-21—Подача