прямые входы второго элемента И-НЕ; соединены соответственно с инверсным вь ходом второго триггера и прямым выходом первого триггера, прямые входы третьего элемента И-НЕ связаны соответственно с прямым выходом второго триггера и первым выходом результата контроля блока фиксации неисправности, выходы второго и третьего элементов И-НЕ блока управления соединены с соответствующими -входами второго элемента И, которого подключен к входу второго элемента задержки и является соотйетствукяцим входом i-ro анализатора.

11

второй выход генератора импульсов блока управления подключен к инверсному входу четвертого элемента И-НЕ, второй прямой вход которого связан с вторым входом первого элемента И-НЕ выход первого элемента задержки соединен с вторым входом первого элемента И, выход которого соединен с соответствующим входом i-ro анализатора , Информационный вход второго триггера связан с прямым выходом первого триггера , информационный вход которого, является входом логической .1 . блока управления,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1984 |

|

SU1236483A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1259270A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство для диспетчерской дуплексной связи | 1985 |

|

SU1293853A1 |

| Логический анализатор | 1989 |

|

SU1734093A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ, содержащее блок управления,и счетчик, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены m анализаторов, блок фиксации неисправности и блок индикации, каждый из .т анализаторов содержит первый И второй мультиплексоры, четыре триггера, блок управления содержит первый и второй триггеры, первый и второй элементы задержки, генератор импульсов, два элемента И, четыре элемента И-НЕ, причем группа входов и группа выходов контролируемого блока подключены соответственно к первым информационным входам первого и второго мультиплексоров каждого i-го анализатора

I ,

Изобретение относится к вычислительной технике и предназначено для выявления неисправностей типа постоянного О или постоянной 1 в любом цифровом блоке, например, блоке синтеза полного Л-елевизионного сигнала системы отображения информации (СОИ) метеорологической радиолокационной станции (МРЛ).

В составе такого блока можно вы- делить функционально законченные устройства синхронизации, оперативной и пюстоянной памяти отображаемой информации, генерации ввдеоимпульсов постоянной и переменной, графической и символьной информации, цифрового формирования и преобразования кодов координат маркера и формирования телевизионного сигнала.

Известно устройство для обнаружения неисправностей в подобном блоке, функционируницее по принципу тестового контроля и содержащее элементы ИЛИ, дешифратор, две группы схем сравнения группу элементов задержки, группу триггеров фиксации состояний, элементы И l .

Недостатком устройства является невозможность разделения синхронизирующих и вычислительных операций.

Наиболее близким по технической сущности к изобретению является устройство для контроля импульсов, содержащее элемент ИЛИ, входы которого подключены к выходам элементов И,

входы первого из которых через соответствующие элементы НЕ подключены к входам второго, генератор контрольного канала, формирователь импульсов мультиплексор и счетчик входом соединенный с выходом элемента ИЛИ, а выходами разрядов - с адресными входами мультиплексора, один из информационных входов которого подключен к выходу генератора контрольного канала, а остальные являются входами устройства, причем выход мультиплексора подключен к первому входу первого элемента И, вторым входом соединенного с выходом формирователя импульсов z.

Недостатками устройства являются низкое быстродействие (контролируемы сигналы блока проверяются последовательно) и недостаточная надежность контроля, так как отсутствует синхронизация между моментами появления сигналов на выходах коммутатора и формирователя импульсов. Это приводит к пропускам обнаружения неисправности.

Цель изобретения - повьппение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для контроля цифровых блоков, содержащее блок управления и счетчик, введены m аналзаторов, блок фиксации неисправности и блок индикации, каждый из m анализаторов содержит первьй и второй

31

мультиплексоры, четыре триггера, бло управления содержит первый и второй триггеры, первый и второй элементы задержки, генератор импульсов, два элемента И, четыре элемента И-НЕ, причем группа входов и группа выходо контролируемого блока подключены соответственно к первым информационным входам первого и-второго мультиплексоров каждого i-ro анализатора (Itiim), вторые информационные входы первого и второго мультиплексоров связаны с выходом прямого кода счётчика, входы сброса первогои второго триггеров i-ro анализатора связаны с выходом первого элемента И-НЕ блока управления, входы сброса третьего и четвертого триггеров i-ro анализатора соединены с выходом второго элемента задержки блока управления, установочные входы первого и второго триггеров i-ro анализатора связаны с третьим выходом первого элемента И блока управления, входы синхронизации первого и второго триггеров i-ro анализатора связаны с выходом четвертого элемента И-НЕ, входысинхронизации третьего и четвертого триггеров i-ro анализатора связаны соответственно с выходами первого .и второго мультиплексоров, выход второго элемента И блока управления подключен к счетному входу счетчика, выход переполнения которого соединен с входом первого элемента задержки блока управления и синхровходом блока фиксации неисправности, первый выход результата контроля которого подключен к первому прямому входу четвертого элемента И-НЕ блока управ ления, входы сигнала проверки и пуска устройства соединены соответственно . fc первым входом первого элемента И-НЕ М с первым входом элемента И блока управления, труппы первых и вторых выходов m анализаторов соединены соответственно с первой и второй группами входов блока индикации, выход обратного кода счетчика связан с третьим входом блока индикации, четвертый вход которого соединен с вторым выходом результата контроля блока фиксации неисправности, вход установки которого является входом установки устройства, нулевые входы первого и второго триггеров блока управления объединены и подключены к входу пуска устройст

ва, С-входы первого и второго триггеров объединены и связаны с первым выходом генератора импульсов и инверсными входами второго и третьего элементов И-НЕ, прямые входы второго элемента И-НЕ соединены соответственно с инверсным выходом второго триггера и прямым выходом первого триггера, прямые входы третьего элемента И-НЕ связаны соответственно с прямым выходом второго триггера и первым выходом результата контроля блока фиксации неисправности, выходы второго и третьего элементов И-НЕ блока управления соединены с соответствующими входами второго элемента И выход которого подключен к входу второго элемента задержки и является соответствующим входом i-ro анализатора, второй выход генератора импульсов блока управления подключен к инверсному входу четвертого элемента И-НЕ, второй прямой вход которого связан с вторым входом первого элемента И-НЕ выход первого элемента задержки соединен с вторым входом первого элемента И, выход которого соединен с соответствующим входом i-ro анализатора, информационный вход второго триггера связан с прямь1М выходом первого триггера, информационный вход которого является входом логической единицы блока управления.

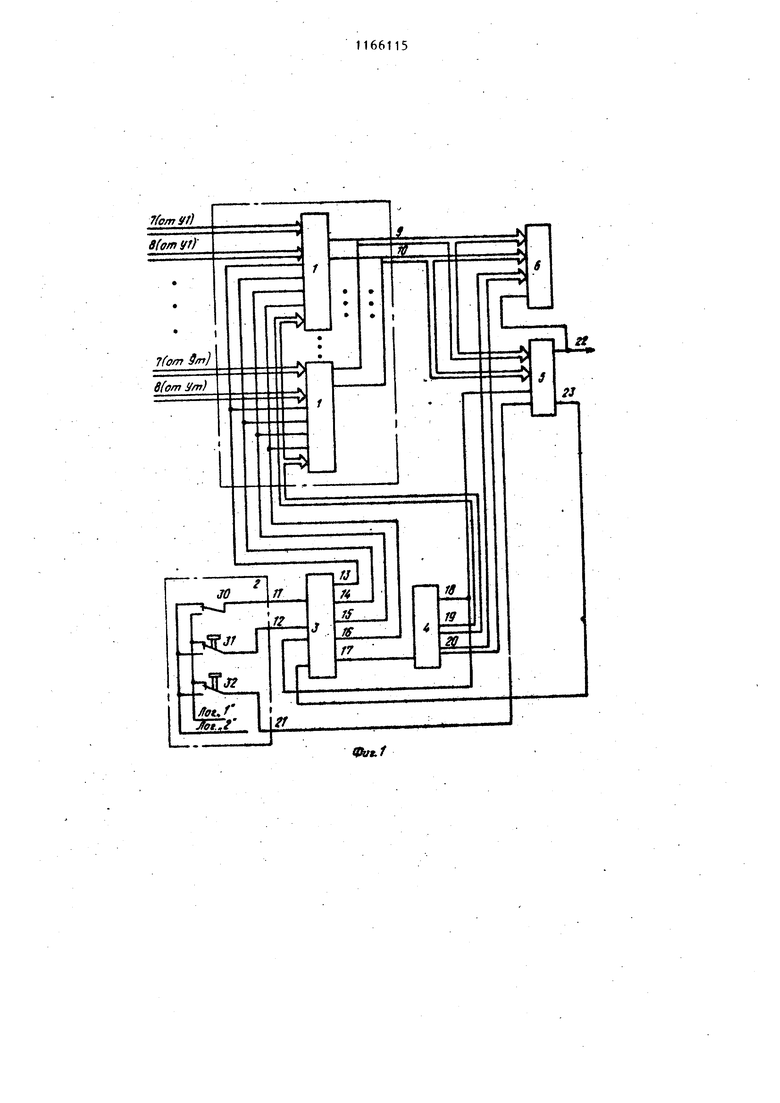

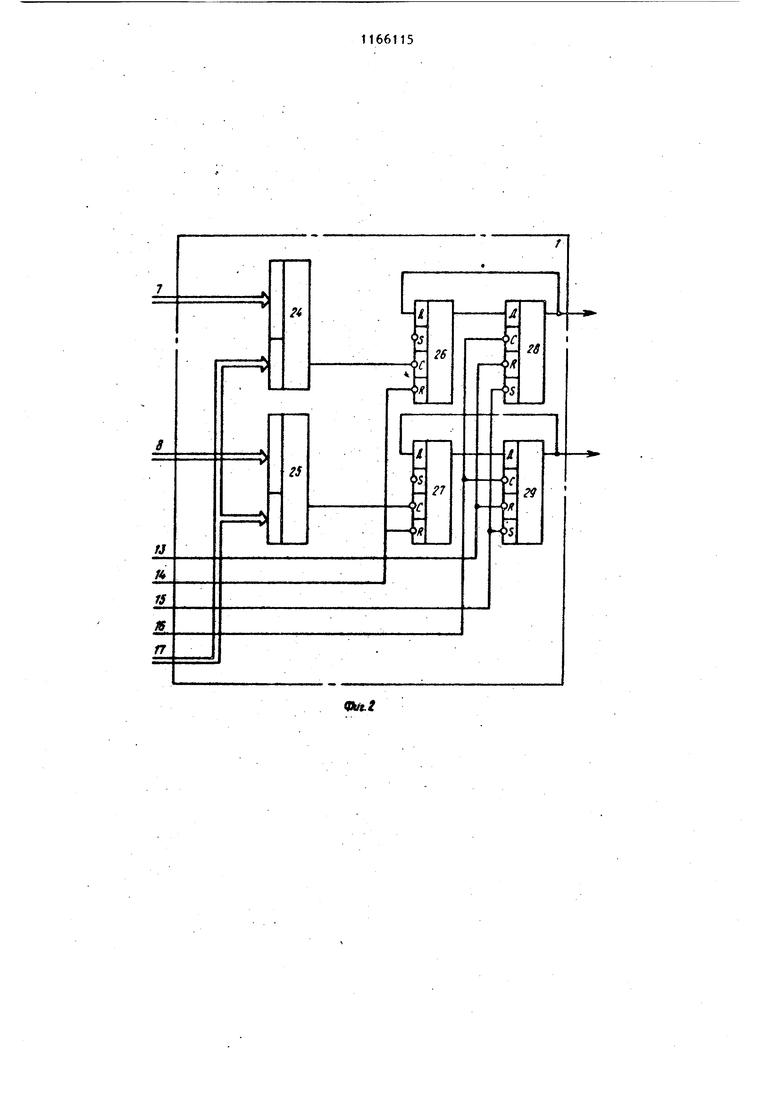

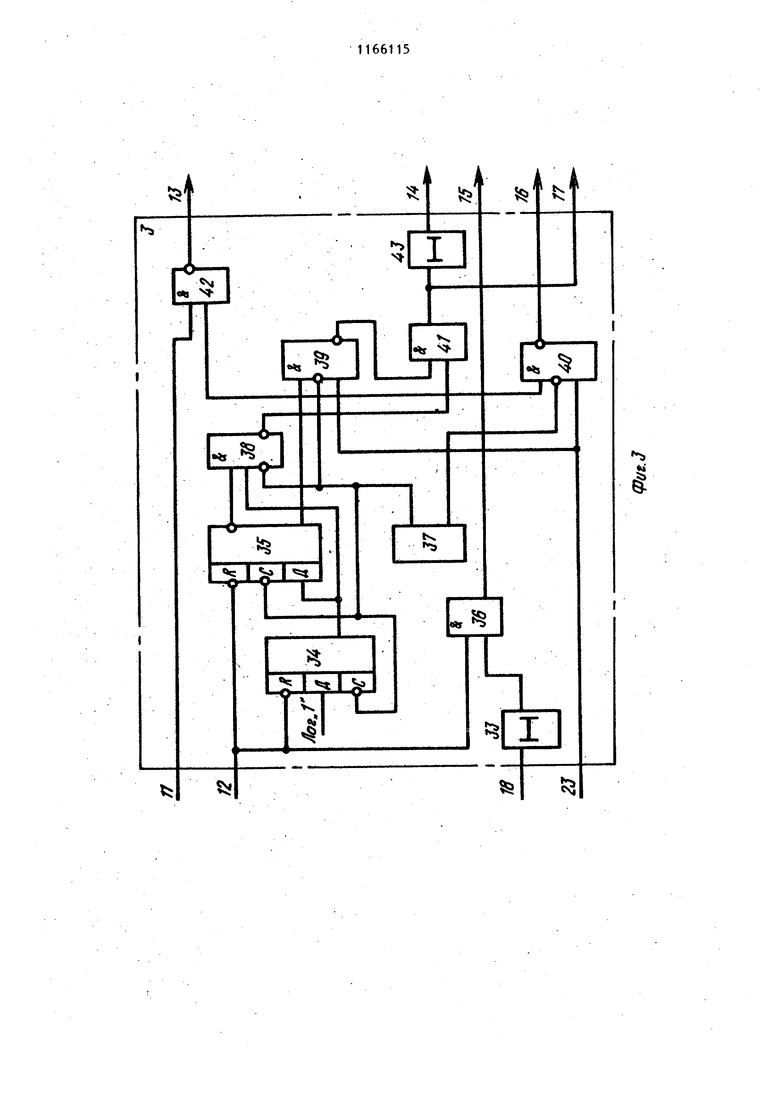

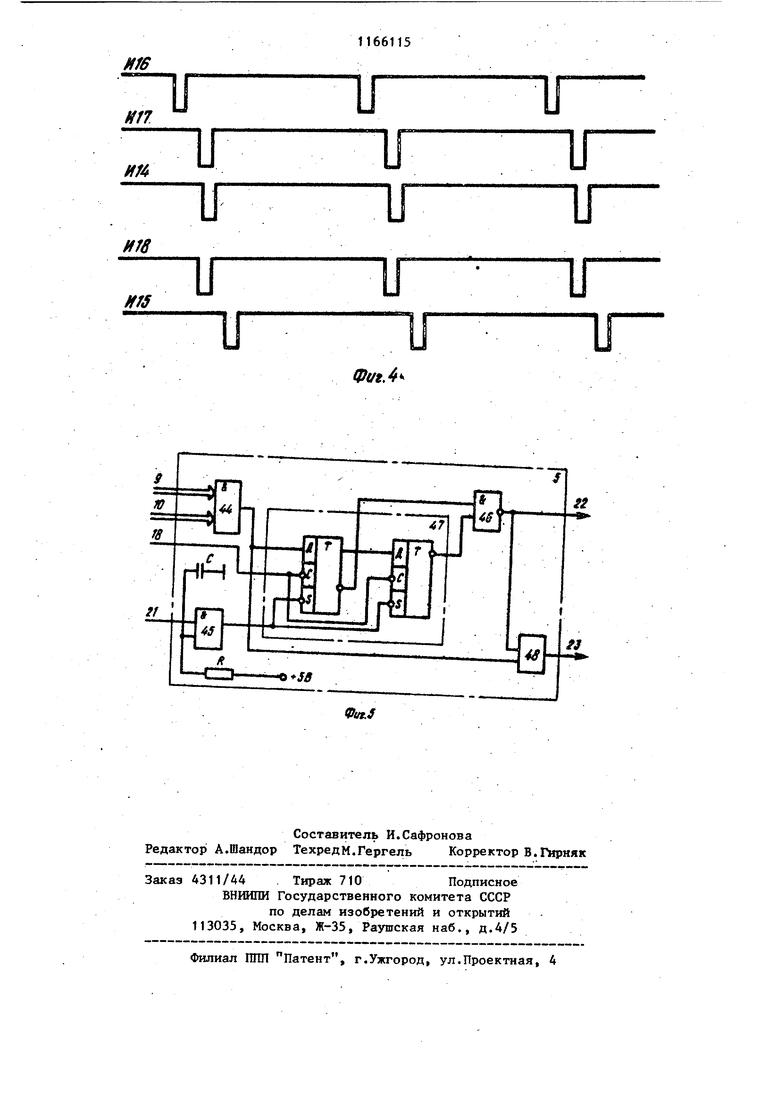

На фиг. 1 показана структурная схема устройства; на фиг. 2 - функциональная схема анализатора;.на фиг. 3 - функциональная схема блока управления; на фиг. 4 - временная диаграмма устройства; на фиг. 5 функциональная схема блока фиксации

неисправности. I - .

Устройство содержит группу m анализаторов 1, пульт 2 управления, блок 3 управления, счетчик 4, блок 5 фиксации неисправности, блок 6 индикации, шины входных 7 и выходных 8 : сигналов контролируемых узлов, шины 9 и 10 анализа входных и выходных сигналов, вход 11 сигнала проверки, вход 12 сигнала пуска, установочные выходы 13 -.15 и выходы 16 и 17 синхроимпульсов блока 3,выход 18 переполнения счетчика, выход 19 прямого и выход 20 обратного кода счетчика А, вход 21 установки, выходы 22 и 23 результирухицих сигналов, анализатор содержит мультиплексоры 24 и 25, триггеры 26 - 29, переключав

тель 30, кнопки 31 и 32 пульта управления, блок управления содержит первый элемент 33 задержки, триггеры 34 и 35, первый элемент И 36, генератор 37 импульсов, второй третий, четвертый элементы И-НЕ 38 - 40, второй элемент И 41 , первь1й элемент И-НЕ 42 второй элемент .43 задержки, блок фиксации неисправности содержит элементы И 44 - 46, регистр 47 элемент ИЛИ 48.

Устройство для контроля цифровых блоков работает следующим образом.

При подаче на вход устройства контроля питаницего напряжения регистр 47 блока 5 устанавливается в исходное состояние 11, и с элемента 48 блока 5 на блок 3 поступает сигнал , по которому блок 3 начинает вырабатывать установочные И 14, И 15, синхронизирующие И 16 ,и счетные И 17 импульсы отрицательной полярности. Счетчик 4 считает импульсы И 17 и выдает текущий код, поступающий на вход каждого из m анализаторов 1, по которому с помощью мультиплексоров 24 и 25 выбираются для каждого ФЗУ соответственно один из входных (т.е. один из Ф7) и один из выходных (т.е. один из Ф8) контро лируемых сигналов.

По импульсу И триггеры 28 и 29 анализатора 1 устанавливаются в 1 (импульсы И 15 формируются элементом 36 блока 3,объединяющим задержанный элементом 33 блока 3 импульс И 18 переполнения счетчика 4 и сигнал И 12 пуска от кнопки 31 пульта управления 2). Триггеры 26 и 27 анализатора 1 фиксируются в сое тоянии О импульсом И .

Импульсы И 14 и И 17 (фиг. 4) сдвнуты во времени относительно друг друга с помощью элемента 33 задержки блока 3, Переключение счетчика 4, а, следовательно, и сигналов на выходах мультиплексоров 24 и 25 анализатора осуществляется по положительному .фронту импульса И 17. Благодаря сдвигу между И 14 и И 17 триггеры 26 и 27 анализатора 1 фиксируются в состояние О во время переходных процессов в счетчике 4 и мультиплексорах 24 и 25.

После установки на выходе счетчика 4 очередного кода по сигналам с мультиплексоров 24 и 25 анализатора 1, поступающим на синхронизирующие входы триггеров 26 и 27 анализатора 1, триггеры 26 и 27 переключаются в 1, и по окончании импульса И 16 логическая 1 переписывается в триггеры 28 и 29 анализатора 1, что говорит об отсутствии неисправности типа логического О или логической 1 на соответствующих входах и выходах соответствующего ФЗУ (частота следования импульсов И 14, 16 и 17 значительно ниже частоты изменения контролируемых сигналов). В случае, если на выходе мультиплексора 24 или 25 анализатора 1 в течение периода импульсов И 16 держится постоянный уровень напряжения (логический О или логическая 1), триггер 26 или 27 анализатора 1 останется в состоянии О, и по импульсу И 16 логический О переписывается в триггер 28 (или 29), что говорит о наличии неисправности в i-м ФЗУ, причем, если в О устанавливается триггер 28, отсутствует входной сигнал i-ro ФЗУ, а если в О устанавливается триггер 29, не вырабатывается выходной сигнал i-ro ФЗУ.

Сигналы анализа.Ф 9и Ф 10 посту|Пают на блок 6, который содержит три линейки светодиодов и элемент индикации .

Сигналы анализа Ф 9 и Ф 10 поступают также на вход блока 5, где объединяются на 2т-входовом элементе И 44. При наличии неисправности, хотя бы в одном ФЗУ (т.е. при появлении сигнала неисправности на шинах 9 или 10) по окончании импульса И 18 в первый разряд регистра 47 блока 5 записывается О с выхода элемента И 44.

Для ТОГО) чтобы обеспечить запись в регистр 47 раньше, чем снимется сигнал неисправности с выхода группы анализаторов 1, импульсы И 18 и И 15 с помощью элемента 33 задержки .блока 3 сдвинуты во времени друг относительно друга не менее, чем на длительность импульса (фиг. 4). .

Элемент И 46 блока 5 выделяет.,состояние 00 регистра 47 и вьщает сигнал П22 общей неисправности на блок 6. Элемент 48 блока 5 выделяет момент появления сигнала неисправности в третьем цикле контроля, вырабатывая сигнал , который запрещает формирование импульсов И 14 17 в блоке 3. ,7 Импульсы И 17 поступают на счетчик 4 с задержкой, т.е. позднее импульса И 16, по которому в триггеры 28 и 29 переписывается информаци с триггеров 26 и 27 соответственно. Поэтому в счетчике 4 при П (т.е. при обнаружении неисправности содержится код, соответствующий номеру неисправного сигнала в i-M ФЗУ Импульсы И 16 и И 17 формируются соответственно с помощью элементов и 38, 39 41 блока 3 из двух послед вательностей импульсов отрицательной полярности, вырабатываемых гене ратором 37 блока 3 и сдвинутых во времени друг относительно друга более, чем на длительность импульса. После автоматического обнаружения неисправности кнопки 31 и 32 пульта 2 позволяют провести счетчик в очередное состояние. При этом по нажатию кнопки 32 пульта управления формируется сигнал , по которо му через элемент 45 блока 5 устанав ливается в исходное положение регистр 47 блока 5 и формируется сигнал . При нажатии кнопки.31 формируетс сигнал И , -устанавливающий в 1 триггеры 28 и 29 анализаторов 1. Поэтому счетчик 4 продолжит счет, начиная с того момента, где он был остановлен, до обнаружения следующе неисправности. Причем сигналом (при нажатой кнопке 31 пульта управ ления 2) триггеры 34 и 35 блока 3 фиксируются в состоянии О, блокируется прохождение сигнала проверки с переключателя 30 пульта управления 2 через элемент 42 блока 3 на установочные входы триггеров 28 и 29 анализаторов 1, С помощью сигнала при необходимости проверяется правильность функционирования устройства контроля. При установке переключателя 30 пульта 2 в положение проверка контроля, т.е. когда П11.1, в блоке 6 индицируются неисправности входных и выходных сигналов всех ФЗ и сигнал П22 общей неисправности. Работа анализаторов 1 после нажатия кнопки 31 пульта 2 организова на так, чтобы вывести триггеры 28 и 29 анализаторов 1 из состояния О С этой целью импульс И 16 поступает на их синхронизирующие входы только тогда, когда произойдет переключе158ние счетчика 4 в новое состояние, следующее за тем, при котором была обнаружена неисправность. По первомл импульсу с генератора 37 устанавливается в 1 триггер 34 блока 3, а с помощью элемента 38 блока 3 происходит выделение второго импульса, начиная с момента пуска, т.е. с момента переключения сигнала П12 из О в 1. Импульс с выхода элемента 38 через элемент 41 блока 3 поступает на вход счетчика 4, а через элемент задержки 43 на установочный вход триггеров 26 и 27 анализаторов 1. Так как триггер 35 блока 3 находится в состоянии О, то импульс И 16 формируется. После этого триггер 35 устанавливается в 1 и разрешает фopмиpoвa Jиe импульсов И 14, И 15, И 16, И 17, согласно фиг. 4, до появления сигнала на выходе блока 5, т.е. до обнаружения очередной неисправности в контролируемом блоке. Таким образом, с помощью кнопок 31 и 32 пульта 2 производится поиск неисправных сигналов ФЗУ блока с фиксацией порядковых номеров сигналов по коду счетчика 4 и определением номера неисправного ФЗУ по соответствующей индикации блока 6. Предлагаемое устройство с высокой степенью надежности контролирует любые динамические последовательности цифрового блока, минимальная частота изменения которых не менее, чем в 2 раза превьшает часто.ту тактовых импульсов контроля, вырабатываемых генератором 37 блока 3. Кроме того, устройство позволяет уменьшить время локализации неисправности за счет того, что индицируется не только номер неисправности сигнала, но и номер ФЗУ с указанием того, какой из Сигналов ФЗУ входной или выходной не изменяется. Технико-экономическая эффективность изобретения заключается в том, что по сравнению с известным предлагаемое устройство обладает более высоким быстродействием (примерно в m раз), а такжеповьшенными степенью надежности контроля (исключается пропуск обнаружения неисправности во время переходных процессов в устройстве контроля) и удобством в эксплуатации (уменьшается время окализации неисправности оператором) .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля синхронизаторов | 1978 |

|

SU730133A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля импульсов | 1980 |

|

SU949793A1 |

Авторы

Даты

1985-07-07—Публикация

1983-06-23—Подача