Изобретение относится к цифровым системам автоматики и вычислительно техники и может быть использовано для контроля и локализации неисправАостей логических схем этих, систем.

Известно устройство для анализа состояний логических узлов, содержащее регистр хранения состояний объекта, соединенный с входами поразрядных сумматоров по mod 2, выходы которых соединены с входами регистра результата, соединенного с блоком управления, а также дополнительно содержащее поразрядные узл анализа изменения состояний объекта и узел формирования кода адреса tU.

Однако известное устройство фиkсирует только абсолютные изменения состояний объекта, что не позволяет контролировать логические связи между элементами испытуемого узла данного объекта, проявляющиеся в процессе прохождения входной последовательности в изменении состояний элементов относительно друг друга Кроме того, известное устройство не может быть использовано в качестве самостоятельного диагностического усройства.

Наиболее близким к изобретению является устройство для анализа состояний логических схем, содержащее элемент индикации, первый и второй элементы ИМПЛИКАЦИЯ, соединеные первыми входами с первым входом устройства, вторыми входами - с вторым входом устройства, выходамис соответствующими первыми входами первого и второго триггеров, соединенных выходами, с первым и вторым входами элемента И соответственно, а также содержащее первый к второй формирователи, элемент ИЛИ и счетчрш соединенный выходами с входом элемента индикации, первым входом - с третьим входом устройства и с. вторыми входами первого и второго триггеров вторым входом - с выходом элемента ИЛИ, соединенного первым и вторым входами через первый и второй формирователи соответственно с первым и вторьтм входами элемента И, соединенного третьим входом с третьим .входом устройства, а выходом с третьими входами первого и второго триггеров 23.

Недостатком известного устройств является отсутствие возможности проверки групп логически связанных элементов испытуемой схемы.

Цель изобретения - повышение производительности устройства.

Поставленная цель достигается тем, что в устройство для контроля и локализации неисправностей логических схем, содержащее узел анализа и элемент индикации, причем уйел анализа содержит первый и

второй элементы ИМПЛИКАЦИЯ, первый и второй триггеры и элемент И, причем первый вход первого элемента ИМПЛИКАЦИЯ соединен с вторым входом второго элемента ИМПЛИКАЦИЯ и является первым входом узла анализа, вт|рой вход первого элемента ИМПЛИКАЦИ Соединен с первым входом второго элементаИМПЛИКАЦИЯ и является вторым входом узла анализа, вход Сброс устройства соединен с R входами первого и второго триггеров узла анализа, i -вход каждого из которых соединен с выходом соответствующего элемента ИМПЛИКАЦИЯ, единичные выходы первого и второго тригеров соединены с входами элементов И, выход которого является выходом узла анализа, введены (м-1) узлов анали:за, п элементов индикации, п элемен ов ИЛИ-НЕ и элемент И, причем первый информационный вход устройства соединен с первым входом первого узла анализа и с вторым входом п-го узла анализа, каждый 1 -и информационный вход устройства (.,3,,.., п. ) соединен с первым Входом i-го и с вторьтм входом ()узлов анализа, выход у-го узла анализа (J 1, 2, . . . , п -11 . соединен с первым входом j-ro, с вторым входо

(i +1) -го элементов ИЛИ-НЕ и с соответствующим входом элемента И, выход п-го узла анализа соединен с первым входом П-го, с вторым .входо первого элементов ИЛИ-НЕ и с соответствующим, входом элемента И, выход каждого элемента ИЛИ-НЕ соедине с входом соответствующего элемента индикации, R -входы .jjepBoro и второго триггеровузлов анализа, начиная со второго, соединены с входом Сброс устройства, выход элемента И соединен с входом (ri+1 -го элемента индикации.

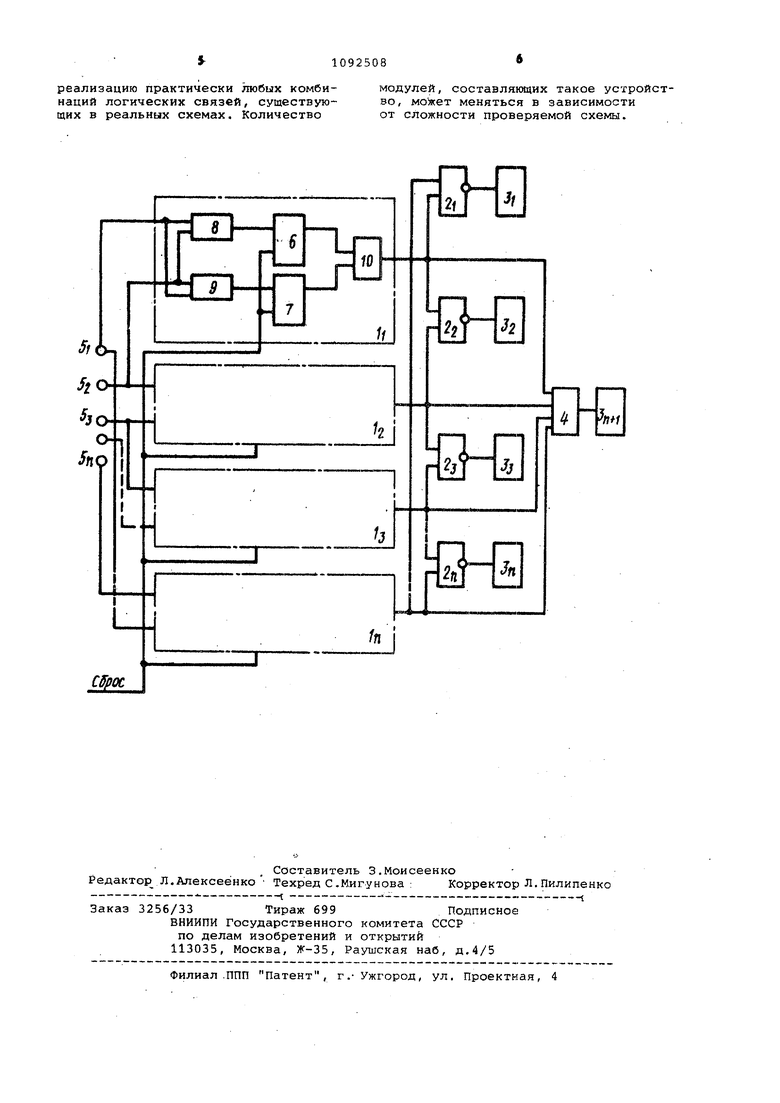

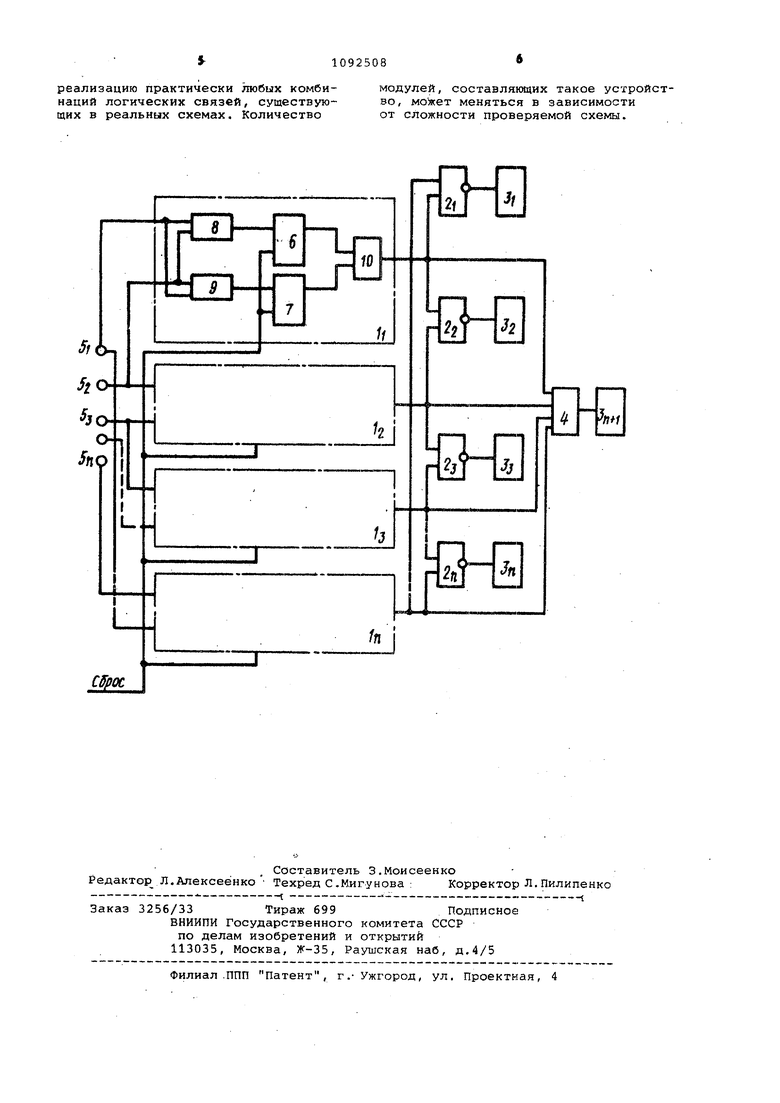

На чертеже приведена блок-схема устройства.

Устройство содержит (п-1 узлов 1 анализа, п элементов ИЛИ-НЕ 2,п элементов 3 индикации, элемент И 4, fi информационных входов 5, а каждый узел анализа Ъодержи.т RS -триггеры б и 7, элементы ИМПЛИКАЦИЯ 8 и 9 и элемент И 10.

В работе пре)лагаемого устройств используется то обстоятельство, что в каждом состоянии логической схемы определяемом текущим входным воздействием, устанавливаются логические связи между элементами как находящимися на линии распространения сигналов от входов схемы .к её выходам, так и межд,у элементами, в общем случае электрически не связанными. Эти связи существуют в рамках данной входной последовательности и заключаются во взаимном относительном изменении логических уровней на контрольных точках схемы. Послед нее означает, что если в какой-либо момент времени выходные сигналы двух, логических элементов были равн О или 1, то для того, чтобы логическая )Связь была зафиксирована, на входы схемы необходимо подать входную кодовую комбинацию, которая вызовет одновременное инвертировани , выходных сигналов этих элементов (1 и О соответственно). Набор соотношений описанного типа графически изображается в виде графа, содержащего вершины, изображающие контрольные точки проверяемой схемы связанные ребрами, представляющими логические связи, образующиеся в проверяемой схеме при подаче на ее входы некоторой последовательности кодовых комбинаций. Топологическая структура графа определяет структур устройства диагностики для данной схемы, т.е. количество устройств, контроля для локализации неисправностей и количество входов каждого из них. Устройство работает следующим образом. По тине Сброс подается сигнал, устанавливающий устройство в исходное состояние. Информационные входы 5 устройства подключаются к выбранным контрольным точкам проверяемой схемы, предварительно установленной в исходное состояние, если она посл довательностная. На входы проверяемой схемы подается последовательнос кодовых комбинаций. В качестве вход ных кодовых комбинаций может служить некоторое подмножество множества входных переменных, использу мых в режиме нормальной эксплуатаци схемы. В процессе работы при появлении, например, на входе 5-, устройства контроля сигнала логического О, а на входе 5 - сигнала логической 1, срабатывает элемент ИМПЛИКАЦИЯ 8 или 9 в зависимости от реализуемо им функции (у 2 + X,, ;. Это вызывает переброс в 1 триггера б или 7, что означает появление комби нации 01 на этих входах. При инвертировании сигналов на входах 5 и 5 устройства (т.е. при появле нии комбинации 10 срабатывает другой элемент ИМПЛИКАЦИЯ и связанный с ним -триггер. Это же справедливо для остальных входов устройств Входные кодовые комбинации, обеспечивающие эти переходы логических уровней, являются тестовыми для про верки схемы в соответствующих контрольных точках. Логическая 1 на выходе второго триггера является вторым разрёшйющим сигналом на входе элемента И 10, на выходе которого появляется сигнал, свидетельствующий, что логические уровни на выходах элементов схемы, к которым подсоединены входи 5 и 5 устройства, инвертировались относительно друг друга, т.е. логическАя связь зафиксирована. Появление единичных сигналов на элементах И 10 остальных узлов анализа приводит к срабатыванию Элемента И 4 и подключенного к его выходу элемента 3 индикации. Изменение логической функции, реализуемой каким-либо элементом проверяемой схемы, вызывает распределение логических уровней на элементах, контролируемых данным устройством, отличающееся от распреде;ления, зафиксированного для исправной схемы. Информация, получанная при рассмотрении изменений состояний элементов относительно друг друга позволяет обнаружить и локализовать неисправный элемент. Если неисправность элемента проверяемой схемы, выход которого используется, например, в качестве контрольной точки, к которой подключен вход 5., , проявляется в константе 1 на этом элементе, то взаимная инверсия сигналов на входах 5 -52 и 5 -5 не будетполучена и единичный сигнал на .выходах элементов И 10 соответствующих узлов анализа не появится, а следовательно, не сработает элемент И 4 и св.язанный с ним элемент 3 индикации. Это свидетельствует о наличии в испытуемой схеме неисправности. Вход уст ройства для контроля и локализации неисправностей, на котором проявилась неисправность,, указывается свечением элемента 3 индикации, связанного через элемент ИЛИ-НЕ 2 с выходами несработавмих узлов анализа (в данном случае 1 и 1р). Элемент 3 индикации однозначно укажет место проявления неисправности .. i Предлаз.-аемое устройство может быть использовано для контроля и локали- . зации неисправностей комбинационных и последовательных логических схем как при проектировании, так и в производственных условиях. Оно позволяет точно указать контакты испытуемой схемы, изменение логических уровней .на которьтх не соответствует аналогичной величине заведено исправной схемы при прогонке одной и той же входной последовательности. Объединение в блок нескольких таких устройств, каждое из которых выполнено в виде отдельного модуля, позволит организовать диагностическое устройство, обладающее большой гибкостью, широким диапазоном возможных применений и обеспечивающее

реализацию практически любых комбинаций логических связей, существующих в реальных схемах. Количество

модулей, составляющих такое устройство, меняться в зависимости от сложности проверяемой схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа состояний логических схем | 1980 |

|

SU951311A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Сигнатурный анализатор | 1986 |

|

SU1388869A1 |

| Многоканальный анализатор логических состояний | 1978 |

|

SU858210A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1141414A1 |

| Устройство для контроля блоков синхронизации | 1983 |

|

SU1134940A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Устройство для формирования тестов диагностики дискретных блоков | 1983 |

|

SU1149265A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ЛОКАЛИЗАЦИИ НЕИСПРАВНОСТЕЙ ЛОГИЧЕСКИХ СХЕМ, содержащее узел анализа и элемент индикации, причем узел анализа содержит первый и второй элементы ИМПЛИКАЦИЯ, первый и второй триггеры и элемент И, причем первый вход первого элемента ИМПЛИКАЦИЯ соединен с вторым входом второго элемента ИМПЛИКАЦИЯ и является перЕым ВХОДОМ узла анализа, второй вход первого элемента ИМПЛИКАЦИЯ соединен с первым входом второго элемента ИМПЛИКАЦИЯ и является вторым входом узла анализа, вход Сброс устройства соединен с R входами первого и второго триггеров узла анализа, S -вход каждого из которых соединен с выходом соответствующего 3JjeMeHTa ИМПЛИКАЦИЯ, едиSHbAiiij: -.л ничные выходы первого и второго триггеров соединены с входами элемента И, выход которого является выходом узла анализа, отличающееся тем, что, с целью повышения производительности, в устройство введены (,п-1) узлов анализа, п элементов индикации,п элементов ИЛИНЕ и элемент И, причем первый информационный вход устройства соединен с первым входом первого узла анализа и со вторым входом п-го узла анализа, каждый i-и информационный вход устройства (i 2 , 3 , . .., nj соединен с первым входом i-ro и с вторым в :одом (i-l|-ro узлов анализа, выход j -го узла анализа (j 1,2,..., n-l) соединен с первым входом ;-го, с (Л вторым входом (J+1) -го элементов ИЛИ-НЕ и с соответствующим входом элемента И, выход П-го узла анализа соединен с первым входом п-го, с вторым входом первого элементов ИЛИНЕ и с сортветствующим входом элемента И, выход каждого элемента ИЛИ-НЕ соединен.с входом соответствующего элемента индикации, R -входы первосо ю го и второго триггеров узлов анализу начиная со второго, соединены с входом Сброс устройства, выход элеСП мента И соединен с входом (h+1) -го элемента индикации. О 00

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для анализа состояний логических узлов | 1975 |

|

SU590744A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для анализа состояний логических схем | 1980 |

|

SU951311A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-15—Публикация

1982-07-30—Подача