(5) ДИСКРЕТНОЕ ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретное фазосдвигающее устройство | 1981 |

|

SU1003289A1 |

| Устройство для цифрового дифференцирования | 1975 |

|

SU608145A1 |

| Дискретное фазосдвигающее устройство | 1981 |

|

SU951591A1 |

| Интерполятор для систем программного управления | 1977 |

|

SU662913A1 |

| Устройство для определения спектральных коэффициентов разложения случайного процесса по функциям Хаара | 1980 |

|

SU935814A1 |

| Параллельный анализатор спектра | 1981 |

|

SU1068835A1 |

| Цифровой анализатор спектра | 1978 |

|

SU734579A1 |

| Счетчик реактивной энергии | 1988 |

|

SU1622828A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| Устройство регистрации сигналов акустической эмиссии | 1987 |

|

SU1516960A1 |

1

Изобретение относится к преобразовательной технике и может быть использовано в устройствах для регулиi рования фазы управлящих импульсов выпрямительно-инверторных преобраi зователей.

Известны дискретные фазосдвигающие устройства, содержащие нуль-орган, (Соединенный с элементом НЕ, генератор тактовых импульсов, соединенный через элемент НЕ со входом счетчика, выход которого соединен с первым входом блока сравнения кодов, второй вход которого соединен с р.е-ч гистром блока управления 1 J.

Недостатком известных устройств является невысокая плавность и томность регулировки выходного напряжения преобразователей, обусловленная нелинейной зависимостью между величиной управляющего кода и величиной выходного напряжения.

Наиболее близким по технической сущности к изобретению и достигаемому результату является дискретное фазосдвигающее устройство, содержащее нуль-орган, вход которого соединен с клеммой для подключения ис.точника синхронизации, а выход - со входом сброса счетчика импульсов, подсоединенного выходами к первым входам блока выделения большего из двух чисел, вторые входы которого соединены с клеммой для подключения источника управляюи4его тока, и генератор тактовых импульсов 27.

Данное устройство характеризует15 ,ся невысокой точностью регулирова-, , ния напряжения.

Цель изобретения - повышение плавности и точности регулирования вы20ходного напряжения.

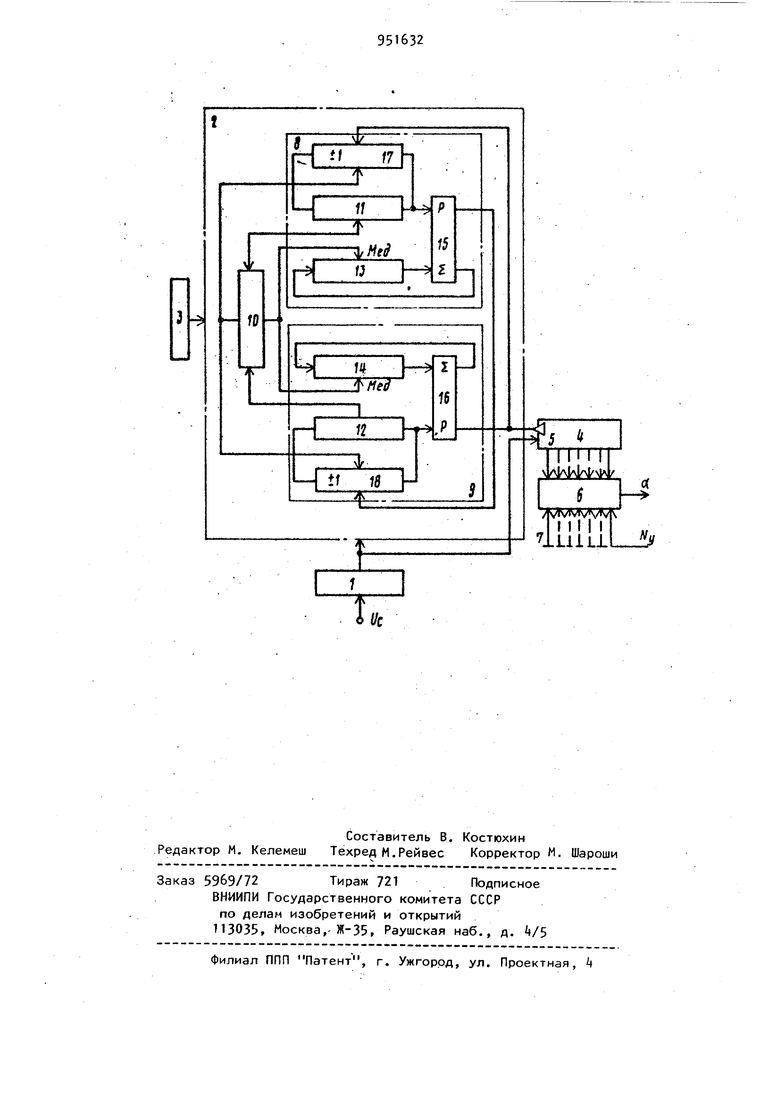

Поставленная цель достигается тем, что устройство снабжено цифровым дифференциальным анализатором. один из входов которого соединен с выходом генератора тактовых импульсов, другой вход - с выходом нуль-органа, а выход его соединен со счетным входом счетчика импульсов. Кроме того, цифровой дифференциальный анализатор выполнен на основе двух интеграторов и блока управления, входы которого соединены с выходами рабочих регистров обоих интеграторов и со входом генератора тактовых импульсов и выход - с управляющими входами регистров - накопителей обоих интеграторов, причем выход регистра-накопителя каждого интегратора соединен через соответствующий сумматор со своим входом, выход рабочего регистра каждого инте ратора соединен со вторым Р-входом соответствующего сумматора, выход ко торого соединен с управляющим входом противоположного элемента ±1, подсое диненного параллельно рабочему регистру соответствукхцего интегратора, а Р-выход второго сумматора одновременно соединен со счетным входом счетчика импульсов. На чертеже приведена принципиальная электрическая схема предлагаемог дискретного фазосдвигающего устройства. Устройство содержит нуль-орган 1 подсоединенный входом к клеммам для подключения к источнику напряжения синхронизации U., а выходом - ко вхо ду цифрового дифференциального анализатора 2. Генератор тактовых импульсов 3 подключен к другому входу цифрового дифференциального анализатора 2, выход которого соединен со входом счетчика h, имеющего вход сброса 5, соединенный с выходом нул органа 1. Выход счетчика k соединен с первым входом блока выделения бол .шего из двух чисел 6, на другой вхо которого подключен вход управляющего кода 7, а выход является выходом ус ройства. Цифровой дифференциальный анализатор 2 состоит из двух интеграторов 8, 9 и схемы управления ув личением-уменьшением 10. Интеграто 8 и 9 в свою очередь, состоят из ра бочих регистров 11 и 12, регистров накопителей 13 и , сумматоров 15 16 и схем ±1 17 и 18. Р-выход ка дого интегратора соединен с входом схемы t1 другого. На другие входы схем i1 17 и 18 нагружен выход блока управления увеличением-уменьшением 10. Устройство работает следующим образом. В момент перехода синхронизирующего напряжения через нуль на выходе нуль-органа 1 появляется импульс, которым приводятся в исходное состояние все регистры цифрового дифференциального анализатора 2 и счетчик 4, Генератор 3 задает работу цифрового дифференциального анализатора 2. В исходном состоянии в рабочем регистре 11 интегратора 8 записано число , где п - разрядность счетчика 4, в регистры накопители 13 и 1 записаны машинные единицы M(.. 2 , а значение кода в рабочем регистре 12 равно нулю. Содержимое рабочих регистров 11 и 12 интеграторов 8 и 9 складывается сумматорами 15 и 16 с содержимым регистров-накопителей 13 и If. Результат сложения передается в регистры-накопители 13 и 1. Импульс переполнения на Р-выходе интегратора 8 через блок управления увеличениемуменьшением ,10 и блок ±1 18 приводит к увеличению на единицу содержимого рабочего регистра 12 интегратора 9 а импульс переполнения на Р-Выходе интегратора 9 через блок управления увеличением-уменьшением, 10 и блок i1 17 приводит к уменьшению на единицу, содержимого рабочего регистра 11 интегратора 8. Когда рабочие регистры интеграторов обменяются содержимь1м, изменяется сигнал на выходе блока управления увеличением-уменьшением 10 и в регистры-накопители 13 и снова записываются машинные единицы . Импульс переполнения на Р-выходе интегратора 8 приводит через схему 1-1 18 к уменьшению на единицу содержимого рабочего регистра 12 интегратора 9, а импульс переполнения на Р-выходе интегратора 9 через схему 41 на единицу увеличивает содержимое рабочего регистра 11 интегратора 8. Восстановление содержимого рабочих регистров 11 и 13 совпадает с приходом следующих импульсов с нульоргана 1, после чего процесс повторяется. Такой алгоритм работы цифрового дифференциального анализатора 2 обеспечивает появление на его выходе импульсов заполнения счетчика 1 с частотой . Тогда количество импульсов, поступивших с выхода цифрового дифференциального анализатора 3 на счетчик k к моменту времени tut определяется из uut . , .ot jAV M-tdi A -cost / --A() о .. к моменту формирования фазы управляющего импульса оС количество импульсов, поступивших на счетчик k Mj A(1-cos ot) , отсюда n Мг ч oL arccos U -д- ) A среднее значение напряжения u,) |-COSO t ГОУССО ( NjL/A) оAT Если обозначить H объем счетчика и учесть, что А равно половине объем счетчика, то , II - 4U i:N-N 3 - . Формирование фазы управляющего импульса происходит в момент совпаде ния значений управляющего кода и к да в счетчике 4, определяемого кол чеством поступивших на счетчик и пульсов М Nj,. Использование предлагаемого изо ретения обеспечивает получение линейной зависимости между средним в ходным напряжением преобразователя значением управляющего кода, что п вышает точность и плотность регули вания выходного напряжения. Формула изобретения 1. Дискретное фазосдвигающее ус ройство для управления тиристорами выпрямительно-инверторных преобразователей, содержащее нуль-орган, ВХОД которого соединен с клеммой для подключения источника синхронизации, и выход - со входом сброса счетчика импульсов, подсоединенного выходами к первым входам блока выделения большего из двух чисел, вторые входы которого соединены с клеммой для подключения источника управляющего кода, и генератор тактовых импульсов, отличающееся тем, что, с целью повышения плавности и точности регулирования выходного напряжения, оно снабжено цифровым дифференциальным анализатором, один из входов которого соединен с выходом генератора тактовых импульсов, другой вход - с выходом нуль-органа, а выход его соединен со счетным входом счетчика импульсов. 2. Устройство по п.1, о т л и чающееся тем, что в нем цифровой дифференциальный анализатор выполнен на основе двух интеграторов и блока управления, входы которого соединены с выходами рабочих регистров обоих интеграторов и со входом генератора тактовых импульсов и выход - с управляющими входами регистров-накопителей обоих интеграторов, причем выход регистра-накопителя каждого интегратора соединен через соответствующий сумматор со своим входом, выход рабочего регистра каждогэ интегратора соединен со вторым Р-входом соответствующего сумматора, выход которого соединен с управляюи им входом противоположного элемента irl, подсоединенного параллельно рабочему регистру соответствующего интегратора, а Р - выход второго сумматора одновременно соединен со счетным входом счетчика импульсов. Источники информации, принятые во внимание при экспертизе . 1.Авторское свидетельство СССР № 664783, кл. Н 02 Р 13/16, 19792.Авторское свидетельство СССР № 660162, кл. Н 02 Р 13/16 1979.

I Ус

Авторы

Даты

1982-08-15—Публикация

1981-01-04—Подача