С 5) ДИСКРЕТНОЕ ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретное фазосдвигающее устройство | 1981 |

|

SU951632A1 |

| Адаптивный статистический анализатор | 1980 |

|

SU877564A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| Устройство для вычисления средне-КВАдРАТичЕСКОгО зНАчЕНия | 1979 |

|

SU849229A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Интерполятор для систем программного управления | 1977 |

|

SU662913A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ КОРРЕКЦИИ ПОГРЕШНОСТИ ЧАСТОТЫ ТАКТОВОГО ГЕНЕРАТОРА МИКРОКОНТРОЛЛЕРА (ВАРИАНТЫ) | 2008 |

|

RU2390786C1 |

Изобретение относится к преобразовательной технике и может быть использовано для регулирования фазы управляющих импульсов инверторов,

нагруженных на сеть переменного тока.

Известны дискретные фазосдвигающие устройства, содержащие нуль-орган, вход кЬторого подключен к источнику напряжения синхронизации, а выход подключен к элементу запрета, генератор тактовых импульсов, счетчик тактовых импульсов, подключенный к вУходу элемента запрета и включающий в себя шину сброса, подключенную к выходу нуль-органа,блок вьщеления большего из двух чисел, входы которого соединены с шиной управляющего кода и выходом счетчика тактовых импульсов, а выход подключен к выходной клемме устройства 13.

Недостатками известных устройств являются невысокая плавность и точность регулирования выходного напря жения.

Наиболее близким к предлагаемому является дискретное фазосдвигающее устройство, содержащее нуль-орган, подсоединенный своим входом к клемме для подключения источника напряжения синхронизации, а выходом - к первому цифрового дифференциального анализатора и к шине сброса счетчика

10 импульсов,выходы которого соединены с входами блока выделения большего из двух чисел,и генератор тактовых импульсов, выход которого подключен ,5 к второму входу цифрового дифференциального анализатора Г21..

Недостатками данного устройства являются невысокая плавность и точ20ность регулирования выходного напряжения.

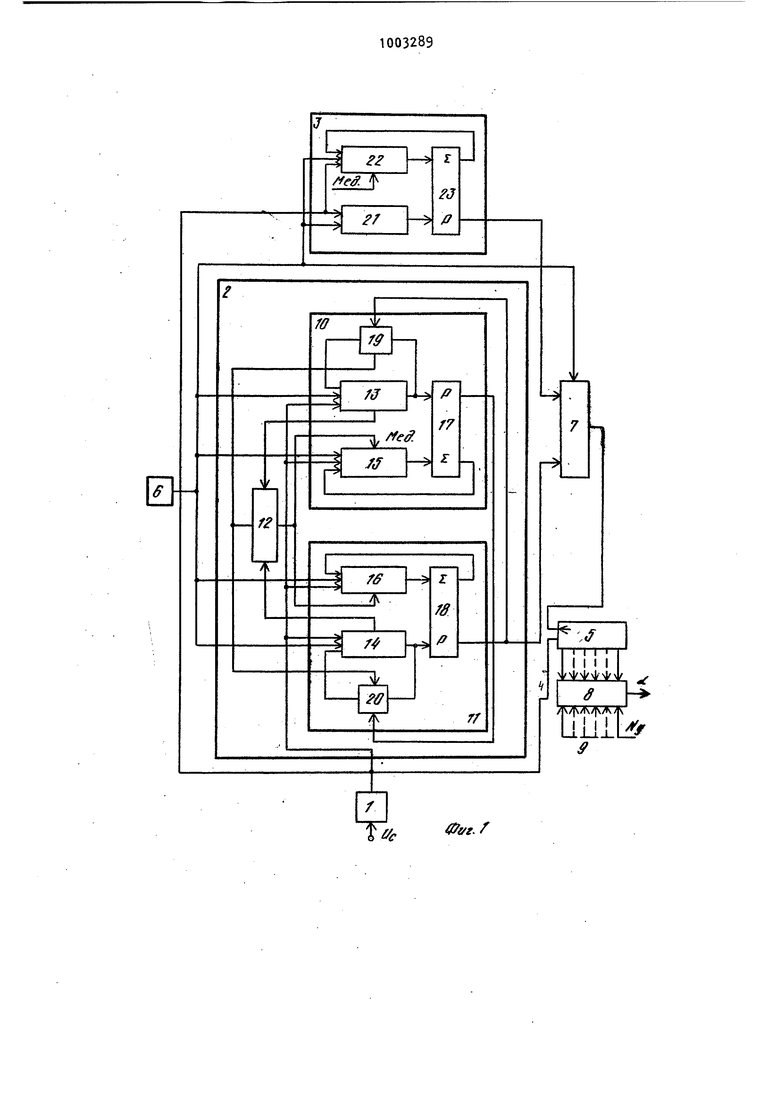

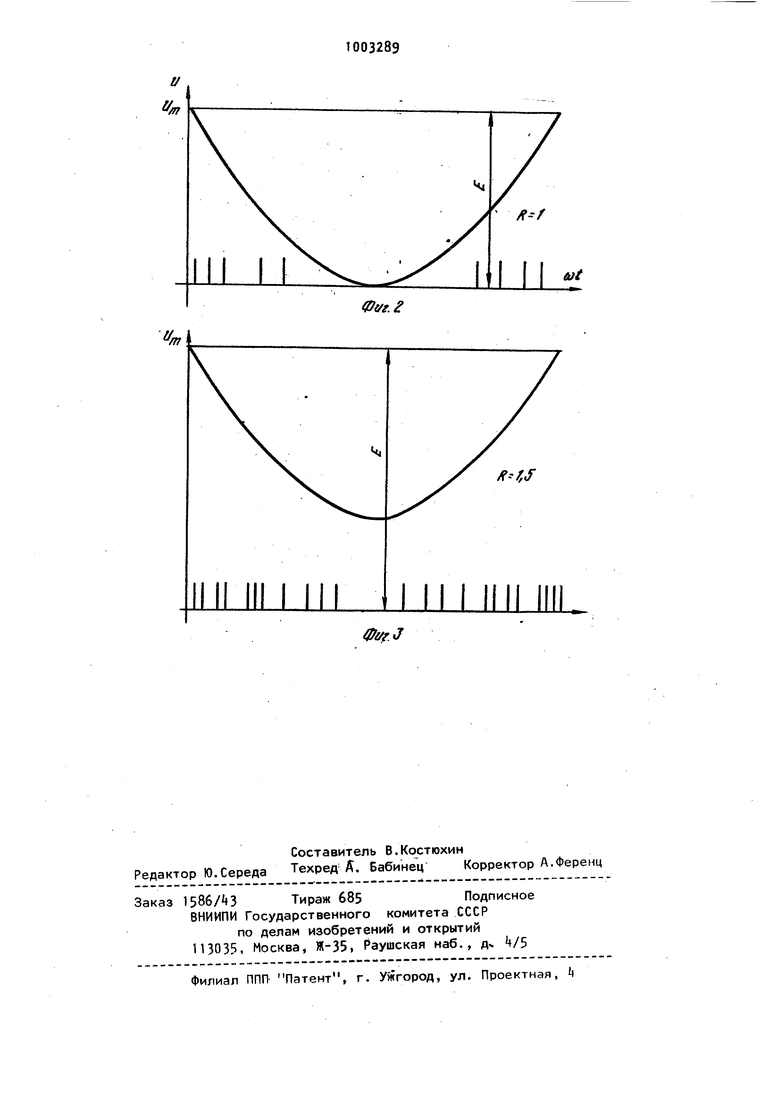

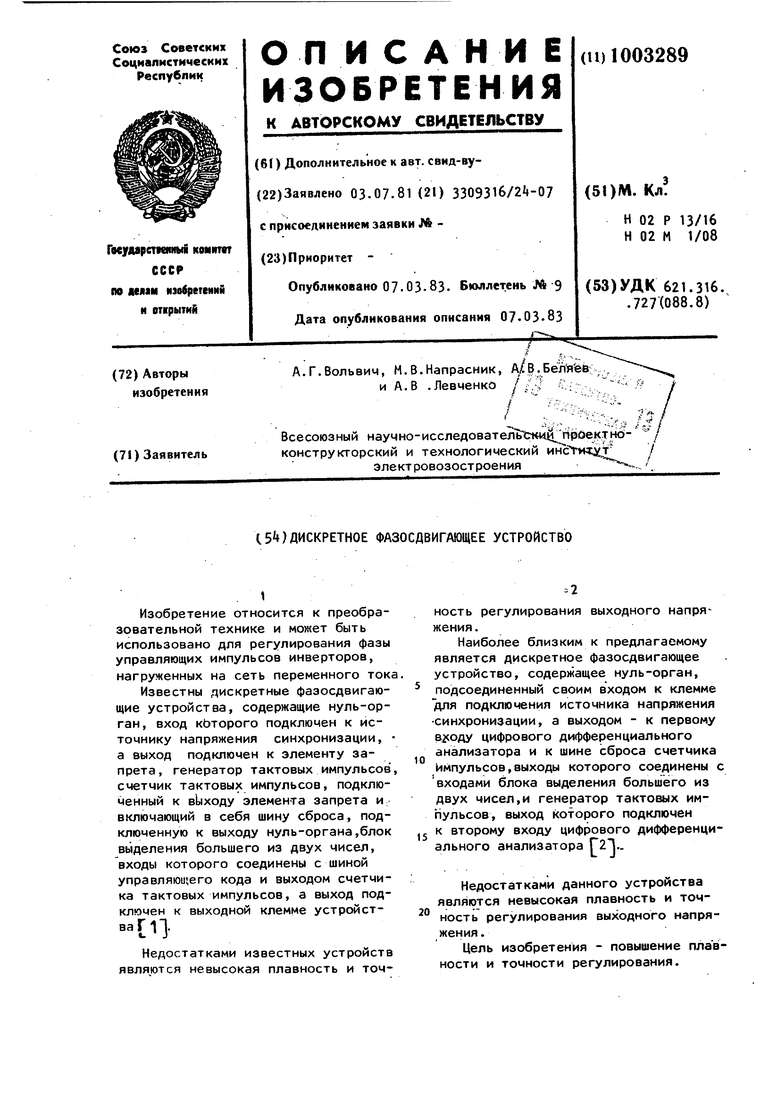

Цель изобретения - повышение плавности и точности регулирования. Поставленная цель достигается тем что устройство снабжено дополнительным интегратором и блоком вычитания, .входы которого подключены соответственно к выходу дополнительного интегратора и к выходу цифрового дифференциального анализатора, выход блока вычитания подключен к счетному входу счетчика импульсов, причем вход дополнительного интегратора под ключен к выходу нуль-органа, а управ ляющие входы дополнительного интегра тора и блока вычит.ания подключены к выходу генератора тактовых импульсов На фиг.1 представлена блок схема предлагаемого фазосдвигающего устройства; на фиг.2 - распределение управляющихимпульсов по полупериоду напряжения сети при соотношении ЭДС инвертора Е и максимального значения напряжения Uy сети, фиг.З распределение управляющих импульсов по полупериоду напряжения сети при соотношении Е|и 1,5. Фазосдвигающее устройство содержит нуль-орган 1, подключеннь1Й своим входом к источнику Up напряжения синхронизации, а выходом - к первому входу цифрового дифференциального анализатора 2, к входу интегратора 3 и к шине сброса счетчика 5 импульсов, генератор 6 тактовых импульсов, подключенный к второму входу цифрового дифференциального анализатора 2, к другому входу интегратора 3 и к входу блока 7 вычитания. К другим входам блока 7 вычитания подключены интёграто-, ра 9 и выход цифрового дифференци-i ального анализатора 2, а выход блока вычитания подключен к счетному входу счетчика 5- Выход счетчика 5 импульсов подключен к первому входу блока 8 выделения большего из двух чисел, к другому входу которого подключена шина управляющего кода 9. Цифровой дифференциальный анализа тор 2 состоит из двух интеграторов 10 и 11 и блока 12 управления. Интеграторы 10 и 11 в свою очередь состо ят из рабочих регистров 13 и 14, регистров-накопителей 15 и 16, сумматоров ;17. и 18 и схем i1, 19 и 20. Выход о каждого интегратора соединен с входом элемента i1 друтого интегратора. Другие входы элементов t1 19 и50 соединены с выхо дом блока 12 управления..Интегратор 3 состоит из рабочего регистра 21, регистра-накопителя 22 и сумматора 23- Устройство работает следующим образом. В момент перехода напряжения сети через нуль на выходе нуль-органа 1 появляется импульс, по которому приводятся в исходное состояние все регистры цифрового дифференциального анализатора 2, интегратора 3 и счетчик 5 импульсов. Генератор 6 тактовых импульсов тактирует работу цифрового дифференциального анализатора 2, интегратора 3 и блоке 7 вычитания. В исходном состоянии в рабочем регистре 13интегратора 10 записано число 2 fj где ,Vi - разрядность цифрового дифференциального анализатора 2, в регистры-накЬпители 15, 16 и 22 интеграторов 10,11 и 3 записаны машинные единицы Hgg. 2, значение кода в рабочем регистре 14 интегратора 11 равно нулю, а в рабочий регистр 21 интегратора 3 заносится число 2 R, где R Е(. Содержимое рабочих регистров 13, 14и 21 интеграторов 10,11 и 3 складывается сумматорами 17, 18 и 23 с содержимым регистров-накопителей 15 16 и 22. Результат сложения помещается в регистры-накопители 15)1б и 22. Появление импульса переполнения на выходе р, интегратора 10 посредством блока 12 .управления и блока il 20 приводит к увеличению на единицу содержимого рабочего регистра 14 интегратора 11, а появление импульса переполнения на выходе р интегратора 11 посредством блока 12 управления и блока ±1 19 приводит к уменьшению на единицу содержимого рабочего регистра 13 интегратора 10. Когда рабочие регистры 13 и 14 интеграторов 10 и 11 обменяются содержимым, изменится сигнал на выходе блока 12 управления, и в регистры-накопители 15 и 16 снова запишутся машинные единицы Mg 2 , После этого, появление импульса переполнения на выходе р интегратора 10 будет приводить через блок ±1 20 к уменьшению на единицу содержимого рабочего регистра 14 интегратора 11, а появление импульса переполнения на выходе р интегратора 11 черёё блок ;1 будет на единицу увеличивать содержимое рабочего регистра 13 интегратора 10. Восстановление содержимого рабочих регистров 13 и 1 совпадает с приходом следующего импульса с нуль-органа 1, после чего процесс повторяется. Импульсы с выхода цифрового дифференциального анализатора 2 поступают .в блок 7 вычитания, где вычитаются из импульсов переполне ния с выхода р интегратора 3. Если импульс с цифрового диф ференциального анализатора 2 приходит в блок 7 вычитания в отхутствие импульса переполнения с интегратора 3 то он вычитается из следующего импульса переполнения интегратора ,3{Описанный выше алгоритм работы ци рового дифференциального анализатора 2 обеспечивает появление на его выходе импульсов с частотой , где f - частота тактового генератора. . Частота тактового генератора .6 f определяется из условия синхронной работы цифрового дифференциального анализатора с напряжением сети. Для этого необходимо, чтобы в течение полупериода напряжения сети с выхода цифрового дифференциального ана лизатора поступило число импульсов, равное объему регистров цифрового дифференциального анализатора, т.е. 2 . Поэтому

т|а

Tli

ir

5АИС1;Ш:- |-С05СУ4.(. irH. Г

отсюда

Частота импульсов переполнения с выхода интегратора J

Ч -и и 0 I

поэтому счетчик 5 заполняется часто,той

г i . 2.% R: - 51мш1 Я-2Г

ц.

51У1 u;-t R-eihOit)..

Тогда количество импульсов, поступивших с выхода блока 7 вычитаФормирование фазы управляющего импульса происходит в момент совпадения значения управляющего кода и значения кода в счетчике 5 определяемого количеством поступивших на счетчик 5 импульсов N Nj. Таким образом, обеспечивается линейная зависимость между средним выходным напряжением инвертора и значением управляющего кода.

Использование в изобретении дополнительного интегратора и блока вычитания для заполнения счетчика дискретного фазосдвигающего устройства обеспечивает линейную зависимость между значениями управляющего кода и выходным напряжением инвертора, в результате чего повышается точность и плавность регулировки выходного напряжения. ия на счетчик 5 импульсов к моменту ремени t, определится в виде 2 a;CR-si«u/t)d-t 2a;|R.t 2 4RCAjbcosa;t-i). К моменту формирования фазы упавляющего импульса ot количество мпульсов, поступивших на счетчик 5 N -a CRd cosd-l), тсюда Ndl тр А среднее значение напряжения 1C UCP Т J CE-Uw, f-F m-UtviSiMoui )d(ju-t(Riwt Ы- . j- я|.лЮ - -C05U;t i;- r ClCR-l-M-coscl) v . №RH-. )- . (2 -VR-2 -Na). Обозначая объем регистров цифового дифференциального анализатора и интегратора 3 N 2, имеем (). Формула изобретения Дискретное фазосдвигающее устройство, содержащее нуль-орган, подсоединенный входом к клемме для подключения источника напряжения синхронизации, а выходом - к первому входу цифрового дифференциального анализатора и к шине сброса счетчика импульсов, выходы которого соединены с входами блока выделения большего из двух чисел, и генератор тактовых импульсов, выход которого подключен ко второму входу цифрового Дифференциального анализатора, отличаю щ е е с я тем, что, с целью повьииения плавности и точности регулирования выходного напряжения, оно снабжено дополнительным интегратором и блоком вычитания, входы которого под ключены соответственно к оыходу дополнительного интегратора и к выходу цифрового дифференциального анализатора, выход блока вычитания подключен к счетному входу счетчика импульсов, причем вход дополнительного интегратора подключен к выходу нульоргана, а управляющие входы дополнительного интегратора и блока вычитания подключены к выходу генератора тактовых импульсов. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР If 660162, кл. Н 02 Р 13/16, 1979. . 2. Авторское свидетельство СССР по заявке N° 3231717/2 -07, кл. Н 02 Р 13/16, .01.81.

г/г.

Авторы

Даты

1983-03-07—Публикация

1981-07-03—Подача