1 ..,

Изобретение относится к области цифровой вычислительной техники и может быть применено при построении цифровых интегрирующих машин с одноразрядными приращеяяями, которые часто называют цифровыми дифференциальными анализаторами (ЦДЛ).

Известно устройство цифрового дифферендировгння 1, в котором-на входы нуль-органа (следящего интегратора) подаются с противоположным и знаками приращения df дифференцируемой функции f и приращения , получаемые на выходе, на вход подинтегральной функции которого поступают выходные импульсы нуль-органа df, а на вход переменной интегрирования - прнращения dx аргумента X, по которому требуется дифференцировать функцию .

Эта схема проста и строится из широко применяемых блоков (интегратор, следящий интегратор), но в ней погрешности формирования производной f могут достигать юсьма больших значений.

Наиболее близким по технической сущности к предложенному устройству является yctройство цифрового дифференцирования {2, содержащее три цифровых интегратора, блок управлення, счетчик и делитель, прнчем выход первого цнфрового интегратора соединен с пер:

вым входов нуль-органа, .второй вход которого к выходу второго цнфрового ий- тегратора, третий вход-к выходу делителя ц первому входу счетчика, четвертый - к третьего цифрового интегратора, а выход нуль-органа - к первому входу третьего цифрового интегратора, второй вход которого соедини с выходом счетчика, и первому входу второго цифрового Интегратора.

Недостатком известного устройства являет 19ся низкая точность.

Целью изобретения является повышение ТОчностн цифрового дифференцирования не путем усреднения влияния, либо частичной ком-. пенсации возникающих погрешностей, а на ос ; нове возможно более полного исключения нх 5 основных схемных нсточннков.

Srite досТнгаетбя тем, что в него введены два узла формнровання пачек импульсов, при- чем входы обоих узлов формирования пачек

11 импульсов соединены с выходом делителя а первые выходы, обоих узлов формирования пачек импульсов подключены ко входу делителя, второй выход первого узла формнрования пачек импульсов соединен со входом nepaoto Цифрового интегратора, а второй выход второго узла формнрования паМек импульсов подключен ко второму входу второго цифрового интегратора и второму входу счетчика.

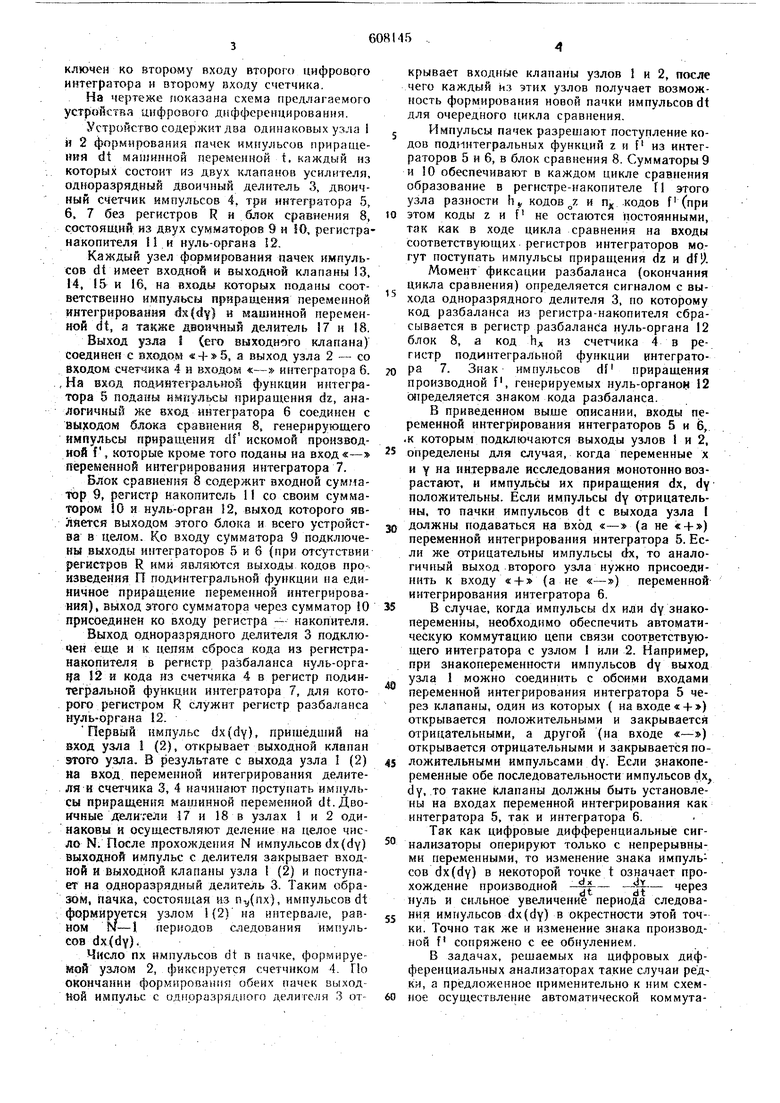

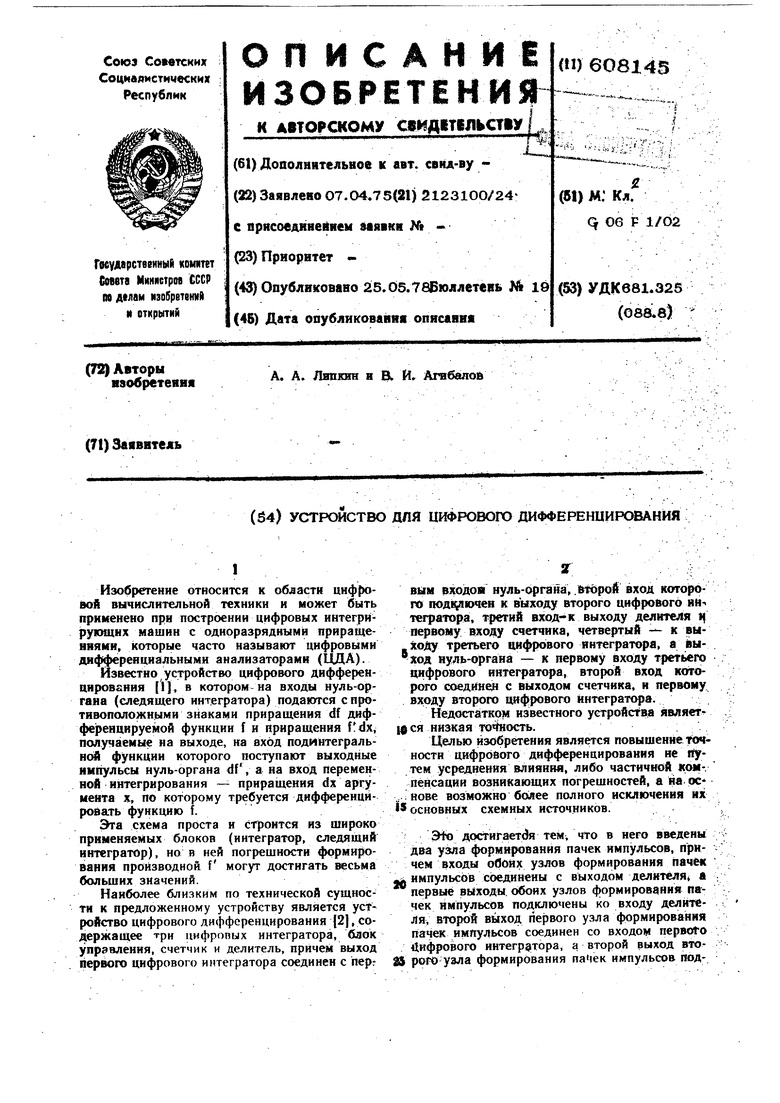

На чертеже показана схема предлагаемого устройства цифрового дифференцирования.

Устройство содержит два одинаковых узла I я 2 формирования пачек импульсов приращения dt машинной переменной t. каждый из которых состоит из двух клапанов усилителя, одноразрядный двоичный делитель 3, двоичный счетчик импульсов 4, три интегратора 5, 6. 7 без регистров R н блок сравнения 8, состоящий из двух сумматоров 9 н 10, регистранакопителя 11 и нуль-органа 12.

Каждый узел формирования пачек импульсов dt имеет входной и выходной клапаны 13, 14, S и 16, на входы которых поданы соответственно импульсы приращения переменной интегрирования dsldy) н машинной переменной dt, а также двоичный делитель 17 и 18.

Выход узла I (его выходного клапана) соединен с входом , а выход узла 2 - со входом счетчика 4 и входом «- интегратора 6. , На вход подинтегральиой функции интегратора 5 поданы импульсы гфиращения dz, аналогичный же вход интегратора 6 соединен с выходом блока сравнения 8, генерирующего импульсы приращения df искомой производной f, которые кроме того поданы на вход«- переменной интегрирования интегратора 7.

Блок сравнения 8 содержит входной сумматор 9, регистр накопитель 11 со своим сумматором 10 и нуль-орган 2, выход которого является выходом этого блока и всего устройства в целом. Ко входу сумматора 9 подключены выходы интеграторов 5 и б (при отсутствии регистров R ими являются выходы кодов про-, изведеняя П подинтегральной функции на единичное приращенне переменной интегрирования), выход этого сумматора через сумматор 10 присоединен ко входу регистрй - накопителя.

Выход однора.чрядного делителя 3 подключен еще и к nemJM сброса кода из регистранакопителя в регистр разбаланса нуль-орга1}а 2 и кода из счетчика 4 в регистр подинтегральной функции интегратора 7, для которого регистром R служит регистр разба ганса иуль-органа 12.

Первый импульс dx(dY), пришедший на вход узла 1 (2), открывает выходной клапан этого узла. В результате с выхода узла I (2) на вход, неременной интегрирования делите. ля н счетчика 3, 4 начинают прступать импульсы приращения машинной переменной dt. Двоичные делители 17 и 18 в узлах I и 2 одинаковый осуществляют деление на целое число N. После прохождения N импульсов dx{dY) выходной импульс с делителя закрывает входной и выходной клапаны узла (2) и поступает на одноразрядный делитель 3. Таким образом, пачка, состоящая из п-у(пх), импульсов dt формируется узлом {2) на интервале, равном isf-i периодов следования импульсов dx(dY)

Число пх импульсов dt в пачке, формируемой узлом 2, фиксируется счетчиком 4. окончании формирования обеих пачек выходНой импульс с одярразрядиого делителя 3 OTкрывает входные клапаны узлов 1 и 2, после чего каждый из этих узлов получает возможность формирования новой пачки импульсов dt для очередного 1икла сравнения. J Импульсы пачек разрешают поступление кодов подиитегральных функций z и f из интеграторов 5 и 6, в блок сравнения 8. Сумматоры 9 и 10 обеспечивают в каждом цикле сравнения образование в регнстре-накопителе Г этого узла разности h,, кодовых и п .кодов f (при

этом коды г и f не остаются постоянными, так как в ходе цикла сравнения на входы соответствующих регистров интеграторов могут поступать импульсы приращения dz и dfp. Момент фиксации разбаланса (окончания Цикла сравнения) определяется сигналом с выхода одноразрядного делителя 3, по которому код разбаланса из регистра-накопителя сбрасывается в регистр разбаланса нуль-органа 12 блок 8, а код h, из счетчика 4 в регистр подинтегральной функции интегратора 7. Знак импульсов df приращения производной f, генерируемых нуль-органов 12 Определяется знаком кода разбаланса.

В приведенном выше описании, входы переменной интегрирования интеграторов 5 и 6, .к которым подключаются выходы узлов 1 и 2,

5 определены для случая, когда переменные х и у на интервале исследования монотонно возрастают, и импульсы их приращения dx, dy положительны. Если импульсы dy отрицательны, то пачки импульсов dt с выхода узла 1

0 должны подаваться на вход «- (а не « + ) переменной интегрирования интегратора 5. Если же отрицательны импульсы d, то аналогичный выход второго узла нужно присоединить к входу « + (а не «-) переменной интегрирования интегратора 6.

В случае, когда импульсы dx или dy знакопеременны, необходимо обеспечить автоматическую коммутацию цепи связи соответствующего интегратора с узлом 1 или 2. Например, при знакопеременности импульсов dy выход узла можно соединить с обоими входами переменной интегрирования интегратора 5 через клапаны, один из которых ( на входе «-f) открывается положительными и закрывается отрицательными, а другой (на входе «-) открывается отрицательными и закрывается по5 ложительными импульсами dy. Если знакопеременные обе последовательности импульсов dx, dy, то такие клапаны должны быть установлены на входах переменной интегрирования как интегратора 5, так и интегратора 6.

Так как цифровые дифференциальные сиг° налнзаторы оперируют только с непрерывными переменными, то изменение знака импульсов dx(dY) в некоторой точке t означает проjitdx

хождение производной

через dt

dt

Нуль и сильное увеличение периода следова5 ния импульсов dx(dY) в окрестности этой точки. Точно так же и изменение знака производной f сопряжено с ее обнулением.

В задачах, решаемых на цифровых дифференциальных анализаторах такие случаи редки, а предложенное применительно к ним схем0 вое осуществление автоматической коммутации цепей с помощью клапанов, устанавливаемых на входах переменной интегрирования интегратора 5 или (и) 6, тривиально. Импульсы df с выхода нуль-органа 12 поступают не только на вход регистра подынтегральной функции интегратора 6, но и на вход «- переменной интегрирования интегратора 7; благодаря чему из кода, хранящегося в регистре разбаланса нуль-органа, каждый раз вычитается код п . После обнуления содержимого регистра разбаланса генерация импульсов df прекращается. Таким образом, числоAf импульсов df, поступающих в результате цикла сравнения в pefHcrp подинтегральной функ ции интегратора б компенсирует ту ощибку в значении производной V, которая имела место в этом цикле, и, будучи п, ,раз переданной в регистр - накопитель, определила сформированный в нем код разбаланса. Впрочем, в действительности вероятность обнуления регистра нуль-органа 12 весьма мала, так как ошибка Af, как и само истинное значение функции f, за время цикла сравнення не остается постоянной. Поэтому код разбаланса в общем случае не кратен значению n« . Однако это приводит лишь к тому, что после выработки значения Af с избытком в одну единицу знак содержимого регистра разбаланса начинает изменяться с каждой машинной итерацией, и с той же частотой происходит пульсация единицы в младшем разряде регистра подинтегральной функции интегратора 6, что практически равнозначно обнулению регистра разбаланса и постоянству кода f. Обновление последнего (изменение на величину А f) начинается сразу после сигнала об окончании цикла сравнения и завершается либо на интервале между двумя последовательными циклами, либо в начале очередного цикла сравнения. Естественно, что и в этом цикле сравнения код разбаланса в регистре-накопителе узла 8 из-за переменности производной f в общем случае окажется опять ненулевым. Легко видеть, однако, что при достижении истинного значения Р он будет весьма мало отличаться от нулевого. В самом деле, если бы цикл сравнения начался в момент одиовремевного поступления приращений dx н dy закончился через промежуток времени Т4 - в момент следующего одновременного поступления импульсов dx и dy и каждый импульс dy вызывал бы при этом выдачу на сумматор блока сравнения кода z, а 1 аждый импульс dx - кода ), то при истинном значеиии последнего в результате этого цикла в регистре-накопителе действительно образовался бы нулевой код разбаланса. При таких условиях за время Тр прощло бы П у импульсов dy, следующих с периодом Tt и пд импульсов dx, следующих с периодом Tj. , т. к. имело бы место ТдП Ti откуда Но в предложенной схеме числа п, и п импульсов dt в пачках, формируемых узлами 1,2 и также управляющих поступлением кодов z и (-f) в блок сравнения 8, определяются как v-CN-D 1-, 1м .(N-1)1, где Т„, - период следования машинных итераций (импульсов dt). Таким образом, и идееь имеет место то же соотношение -. -СЫ IY . tj-y 1 . Заметим, что это соотнои сние не является вполне точным, потому что значения периодов Т, н TY за время цикла сравнения Tt не остаются постоянными. И дело здесь не только и не столько в нзменении производных от X иУ за малое время Т, сколько в особенностях работы цифровых дифференциальных анализаторов. Ведь даже в том случае, если приращения dx(dy) формируются цифровым интегратором, в регистре подинтегральной функции которого хранится постоянный код, а на вход переменной интегрирования пос-, тупают импульсы dt приращения мащинной переменной, последовательные значения Т (Ту), измеряемые числом периодов Тн , часто отличаются друг от друга на единицу, потому что коэффициент заполнения регистра подинтегральной функция не представляется простой дробьюхвида . При достаточно больших значениях отношений и -Lr (которые всегда являются 1 и1 м целыми числами) это не имеет существенного значения и делителями 17 и 18 узлов I и 2 целесообразно реализовать число N 2. ffo при малых значениях н может Гг Тм . оказаться выгодным увеличить это число во избежание частых появлений поправок Af с чередующимися знаками в значения искомой производной f. Правда, с возрастанием N снижается частота обновления значения производной f. Поэтому выбор величины N должен в каждом случае сообразоваться как со значениями отношений 1 и - так и с ожидаемой скоростью изменения функции f, в соответствии с чем в делителях 17 и 18 узлов 1 и 2 иадле-. жит предусмотреть обратные связи между их выходами и входами их двоичных разрядов. подключаемые нужным образом тумблерами. Эффект повышения точности выполнения операции дифференцирования предлагаемым устройством, по сравнению с прототипом и другими известными его модификациями, определяется применением блока сравнения, в котором правильность полученного значения производной проверяется на основе сопоставления полных, а не квантованных изменений соответствующих интегралов (переносом регистров из интеграторов в блок сравнения), рациональной организацией циклов сравнения с помощью узлов 1 и 2, и, наконец, использованием интегратора 7 для определеиия опгибки Af в значении производной f. имевшей место в проведенном цикле сравнения, и её .|{емёДЛ&{Ной компенсаций. Последнее обстоя1ждьсгйо приводит к устранению неизбежных для прйтотипд колебаний формируемой функций f относительно ее истинного значения f, период и амплитуда которых тем больше, чем упомяяутое в начале описания запаздывание в определении отклонения f-f. Эффект повышения точности дифференцирования возрастает с увеличением отно „(. Т Ту т шейий « -. ( -ffr (гдец, |у, IM - периоды следования импульсов приращения соответственно перемеииых интегрироВйИия X,Y и машинной переменной t,. Предлагаемое устройство строится из стаидартных элементов и может быть быстро создаио влюбом предприятии, занимающемся разработкой и изготовлением цифровой вычислиtiejibMoft техники ив частности машииы типа цифрового дифференциального анализатора. Формула изобретения Устройство |Цифрового днфференцироНАтя, с6дер 1ащее;Три цифровых интегратора;-блок сравнения, счетчик и делитель, причём выход первого цифрового интегратора соег-Ifдинен с первым входом нуль-органа, второй вход которого подключен к выходу второго цифрового интегратора, третий вход - к выходу делителя и первому входу счетчика, четвертый к выходу третьего цифрового иитегратора, а выход иуль-оргаиа-к первому входу третьего цифрового интегратора, второй вход которого соедииен с выходом счетчика, и первому входу второго цифрового Интегратора, отличающееся тем, что, с целью повышения точности, в него введейы два узла формирования пачек импульсов, причем входы обоих узлов формирования пачек импульсов соедииеиы с выходом делителя, а первые выходы обоих узлов формирования пачек импульсов подключены ко входу делителя, второй вЫ; ход первого узла формирования пачек импульсов соединен со входом первого цифрового иитегратора, а второй выход .второго узла формирования пачек импульсов подключеи ко второму входу второго цифрового итегратора и второму входу счетчика. Источники информации, принятые во виимаиие при экспертизе: . Майоров В. Ф. Электрониые цифровые интегрирующие машииы, Машгиз, М., 1962. 2. Авторское свидетельство СССР № 404095, кл. Q 06 J 1/02, 08.09.72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1976 |

|

SU651371A1 |

| Устройство для решения задач оптимального управления | 1985 |

|

SU1270779A1 |

| Устройство для задания скорости в системах числового программного управления | 1984 |

|

SU1259213A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1968 |

|

SU213416A1 |

| АВТОРУЛЕВОЙ, РЕАЛИЗУЮЩИЙ ПРОПОРЦИОНАЛЬНО- ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ ЗАКОН УПРАВЛЕНИЯ | 1968 |

|

SU213943A1 |

| Устройство задания скорости в системах числового программного управления | 1984 |

|

SU1211695A1 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| Автосчислитель | 1979 |

|

SU836525A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ПРОЦЕССОМ ВЫРАЩИВАНИЯ МОНОКРИСТАЛЛОВ ИЗ РАСПЛАВА | 1990 |

|

RU2023768C1 |

Авторы

Даты

1978-05-25—Публикация

1975-04-07—Подача