1

Изобретение относится к технике передачи дискретных сигналов и может использоваться при приеме биполярных многоуровневых сигналов.

Известно устройство для приема биполярных многоуровневых сигналов, содержащее блок формирования тактовых импульсов, первый выход которого подключен к входу блока памяти, выход которого соединен с первым входом блока перемно-,д жения сигналов, и последовательно соединенные компаратор и регистр, к второму входу которого подключен второй выход блока формирования тактовых импуль.COBjl .15

Однако известное устройство имеет низкую верность приема и узкий динамический диапазон пршгамаемых сигналов.

Цель изофетешш - повышение верное- 20 ти приема и расширение динамического диапазона принимаемых сигналов.

Поставленная цель достигается тем, . что в устройство для приёма- биполярных

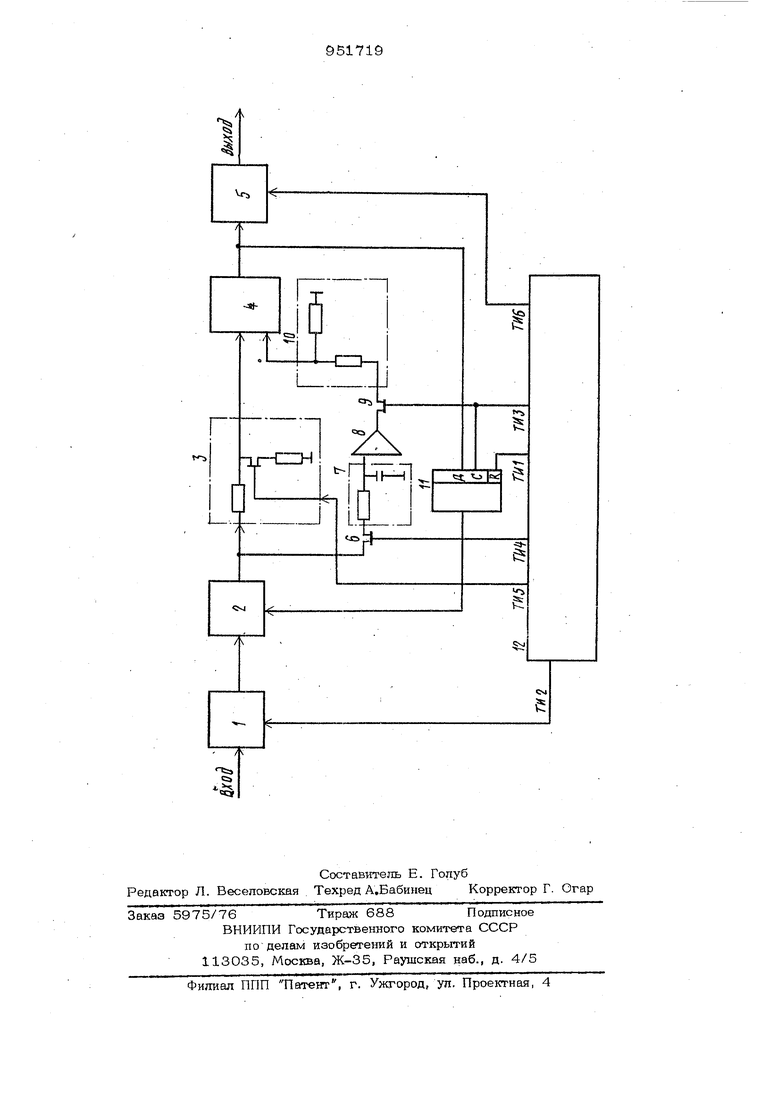

многоуровневых сигналов введены два ключа, интегратор, буферный усилитель, триггер и резистивный делитель, вькод которого подключен к первому входу компаратора, выход которого соединен с первым входом триггера, второй вход которого соединен с первым входом первого ключа и с третьим выходом блока формирования тактовых импульсов, четвертый выход которого подключен к третьему входу триггера, выход которого соединен с вторым входом блока перемножения сигналов, выход которого подключен к первым входам управляемого делителя и второго ключа, второй вход и выход которого соединены соответственно с пятым выходом блока формирования тактовых импульсов и входом интегратора, выход которого через буферный усилтггель соединен с вторым входом первого ключа, выход которого подключен к входу резистивного делителя, а шестой выход блока формирования тактовых импульсов соединен с вторым входом управляемого делителя, выход которого подключен к второму входу компаратора. На чертеже представлена структурная схема предложенного устройства. Устройство для приема биполярных многоуровневых сигналов содержит блок 1 памяти, блок 2 перемножения сигнало управляемый делитель 3, компаратор 4, регистр 5, ключ 6, интегратор 7, буфер ный усилитель 8, ключ 9, резистивный делитель 10, триггер 11, блок 12 фор-мнрования тактовых импульсов. . Устройство работает следующим образом. В исходном состоянии ключи 6 и 9 закрыты, коэффициент передачи управляемого делителя 3 равен 1, триггер 11 тактовым и лryльcoм ТИ1 установлен в нулевое состояние, соответствующее наличию на его выходе логического нуля. Многоуровневый информационный сигнал поступает на первый вход бдока памяти 1, на Второй вход которого поступает с выхода блока 12 тактовая частота ТИ При поступлении импульса тактовой частоты ТИ2 в блоке 1 осуществляется стробирование входного сигнала и его запоминание. С выхода блока 1 сигнал поступает на первый вход блока 2 перемножения сигналов. При поступлении на его второй вход с триггера 11 логического нуля коэффициент передачи блока 2 равен 1, при поступлении логической единицы - минус 1. После установки триггера 11 в исходное положение с его выхода на второй вход блока 2 перемножения сигналов подается логический нуль и на выходе блока 2 устанавливается тот же сигнал, что и на входе. Так как в отсутствие тактового импульса ТИЗ ключ 9 закрыт, на первый вход компаратора 4 через резисторный делитель 10 подается нулевой пороговый уровень. С выхода блока 2 через управляемый дели тель 3, коэффициент передачи которого в отсупхггвие тактового импульса ТИБ равен 1, информационный сигнал- поступает на второй Вход компаратора 4, где осуществляется его сравнение с нулевым порогом. В результате этого сравнения определяется знак информационного сигнала, который записывае1ся под передний фронт импульса тактовой частоты ТИЗ в триггер 11. При отрицательном сигнале, поступающем с выхода блока 1 на вход блока 2 перемножения сигналов, в триггер 11 записывается логичес кий нуль, в результате чего устанавлива ется коэффициент передачи блока 2 перемножения сигналов равный 1. При этом на выходе блока 2 устанавливается отридательный уровень, равный входному . При положительном сигнале на входе блока 2 перемножения сигналов в триггер 11 записывается логическая 1, которая устанавливает коэффициент передачи блока 2. перемножения сигналов, равным -1, в результате чего и в этом случае на выходе блока 2 перемножеНяя сигналов устанавливается отрицательный уровень, по абсолютной величине равный входному. Таким образом, в блоке 2 перемножения сигналов осуществляется выпрямление сигнала в отрицательную область значений. В момент поступления тактовой частоты ТИ4 с задержкой относительно переднего фронта тактового импульса, ТИЗ ключ 6 открывается, заряжая через резистор конденсатор интегратора 7. Конденсатор хранит опорный сигнал для формирования порогов сравнения. Постоянная времени интегратора 7 выбирается таКИМ образом, чтобы при приеме случайной последовательности информационных символов колебания вьшрямленного значения принятого сигнала, усредненного интеГратором 7, относительно его среднеГО значения были бы незначительны. Далее опорный сигнал через буферный усилитель 8 и ключ 9, открытый импульсом тактовой частоты ТИЗ, поступает на резистивный делитель 10, с выхода которого уровень порога, пропорциональный среднему уровню опорного сигнала, поступает на первый вход компаратора 4, на второй вход которого через управляемый делитель 3 поступает стробированный сигнал с выхода блока 2. В компараторе 4 осуществляется сравнение отсчетного значения информационного си1 нала в момент стробирования и порогового сигнала на выходе резистивного делителя 10. Отнощение порога к средней величине модуля отсчетов информационного сигнала может варьироваться в широких пределах изменением коэффициентов передачи управляемого и резистивного делителей. В момент.поступления первого тактового импульса ТИб результат сравнения записывается в регистр 5. Для сравнения сигнала с другим порогом, т.е. при другой величине указанного отнощения, на управляемый делитель 3 с задержкой относительно первого импульса ТИ6 подается тактовый импульс ТИБ. Если для приня59

тия решения о переданном символе требуется провести сравнение сигнала с несколькими пороговыми значениями, то соответственно увеличивается число управляемых входов управпяемо.го делителя 3 и выходов блока формирования тактовых импульсов 12, при этом таютовые импульсы на различные управляемые входы управляемого делителя 3 должны подаваться со сдвигом во времени, и сравнение сигнала с различными порогами производится поочередно.

Результат сравнеггая с выхода компаратора 4 подается на вход регистра 5, на Второй вход которого поступает тактовая частота ТИ6 от блока 12, величина которой зависит от сравнений, которые необходимо провести. Результаты сравнения с выхода компаратора 4 записыиаются в различные элементы (Памяти. После получения сравнения со всеми требуемыми пороговыми значениями блоком 1 памяти фиксируется новое |информационное значение входного сигнала в момент поступления следующего импульса ТИ2.

В конце каждого интервала Т анализ тсчетного значения сигнала триггер 11 Ьновь устанавливается в исходное поло|жение тактовой частотой ТИ1.

Таким образом, предложенное устройство обеспечивает более высокую точност установки порогов сравнения, так как все необходимые для анализа принимаемого сигнала операции сравнения осуществляют на одном компараторе, при этом исключается дополнительная погрешность от взаимного разброса параметров компараторов; формирование опорного сигнала непосредственно из отсчетных значений информационного сигнала и отслеживание всех его изменений, что делает работу устройства практически независящей от изменений входного уровня сигнала в широком динамическом диапазоне и от колебаний и разфоса амплитудно-частотных Г характеристик каналов связи. Оба указан7196

ных фактора приводят к уменьшению вероятности ошибок при приеме данных.

Формула изобретения

Устройство для приема биполярных многоуровневых сигналов, содержащее блок формирования тактовых импульсов, первый выход которого подключен к входу блока памяти, выход которого соединен с первым входом блока перемножения сигналов, и последовательно соединенные компаратор и регистр, к второму входу регистра подключен второй выход блока формирования тактовых импульсов, отличающееся тем, что, d, целью повышения верности приема и расширения динамического диапазона принимаемых сигналов, введены два ключа, интегратор, буферный усилитель, управляемый делитель, триггер и резистивный делитель, выход которого подключен к первому входу компаратора, выход которого соединен с первым входом триггера, второй вход которого соединен с первым входом первого ключа и с третьим выходом блока формирования тактовых импульсов, четвертый выход которого подключен к третьему входу триггера, выход которого соединен с вторым входом блока перемножения сигналов, выход которого подключен к первым входам управляемого делителя и второго ключа, второй вход и выход которого соединены соответственно :с пятым выходом блока формирования тактовых импульсов и входом интегратора, выход которого через буферный усилитель соединен с вторым входом первого ключа, выход которого подключен к входу резистивного делителя, а шестой выход блока формирования тактовых импульсов соединен с вторым входом управляемого делителя, выход которого подключен к второму входу компаратора.

Источник 1 информации, принятые во внимание при экспертизе

1. Патент США № 3315252, кл. 340-347, 1967 (прототип).

f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема биполярных многоуровневых сигналов | 1986 |

|

SU1390802A2 |

| Устройство для приема биполярных многоуровневых сигналов передачи данных | 1973 |

|

SU586570A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460225C1 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2001 |

|

RU2187824C1 |

| Демодулятор сигналов амплитудной манипуляции | 2023 |

|

RU2808227C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ТАКТОВОГО СИНХРОСИГНАЛА ИЗ МНОГОУРОВНЕВОГО ЦИФРОВОГО СИГНАЛА | 1992 |

|

RU2033698C1 |

| Устройство для счета движущихся объектов | 1985 |

|

SU1312623A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

Авторы

Даты

1982-08-15—Публикация

1981-01-30—Подача