Изобретение относится к технике связи и может использоваться в высокоэффективных системах связи для восстановления временных характеристик многоуровневого цифрового сигнала электросвязи.

Известно устройство для регенерации цифрового сигнала, содержащее компаратор и тактовый генератор, выход которого подключен к входу делителя частоты, первый выход которого соединен с первым входом блока управления и с одним входом согласующего блока, а также два конденсатора, два ГЛИН и два коммутирующих диода, аноды которых подключены параллельно соответствующим первому второму ключам, а также соединены с входами компаратора и выводами конденсаторов, другие выводы которых соединены с выходами соответствующих ГЛИН, с выходами блока управления и с другими входами согласующего блока, причем выход компаратора подключен к входу ТГ через последовательно соединенные блок анализа сигналов, реверсивный счетчик, резистивную матрицу и ФНЧ, при этом выход СБ соединен через счетчик с вторым входом блока анализа сигналов, а входы управления первого и второго ключей соединены с первым дополнительным выходом БУ, второй дополнительный выход которого соединен с дополнительным входом компаратора.

Недостатком этого устройства являются ограниченные функциональные возможности, связанные с неспособностью выделить тактовый синхросигнал из многоуровневых цифровых сигналов электросвязи, которые могут иметь длительные последовательности одинаковых символов цифрового сигнала без возврата к нулю в каждом такте.

Целью изобретения является расширение функциональных возможностей за счет возможности выделения тактового синхросигнала из многоуровневых цифровых сигналов.

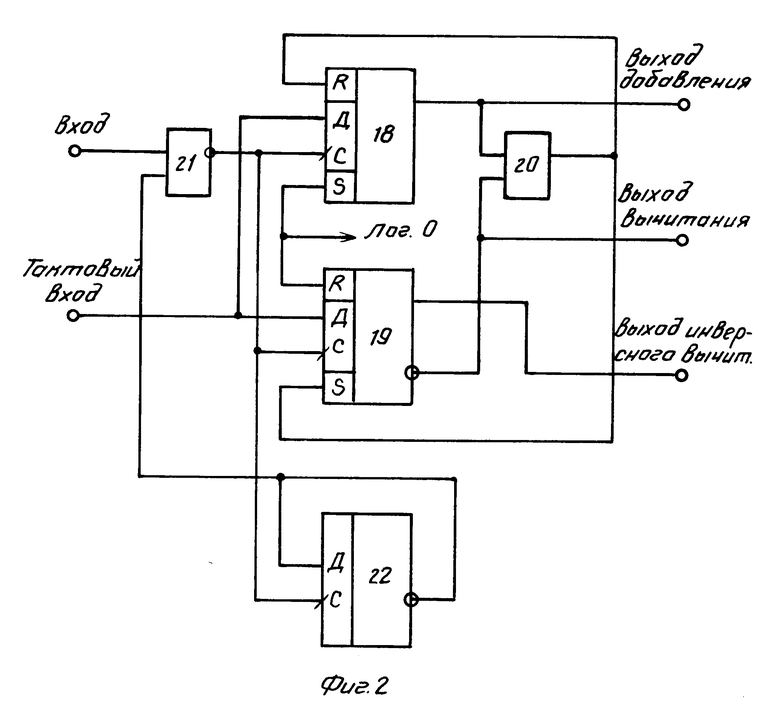

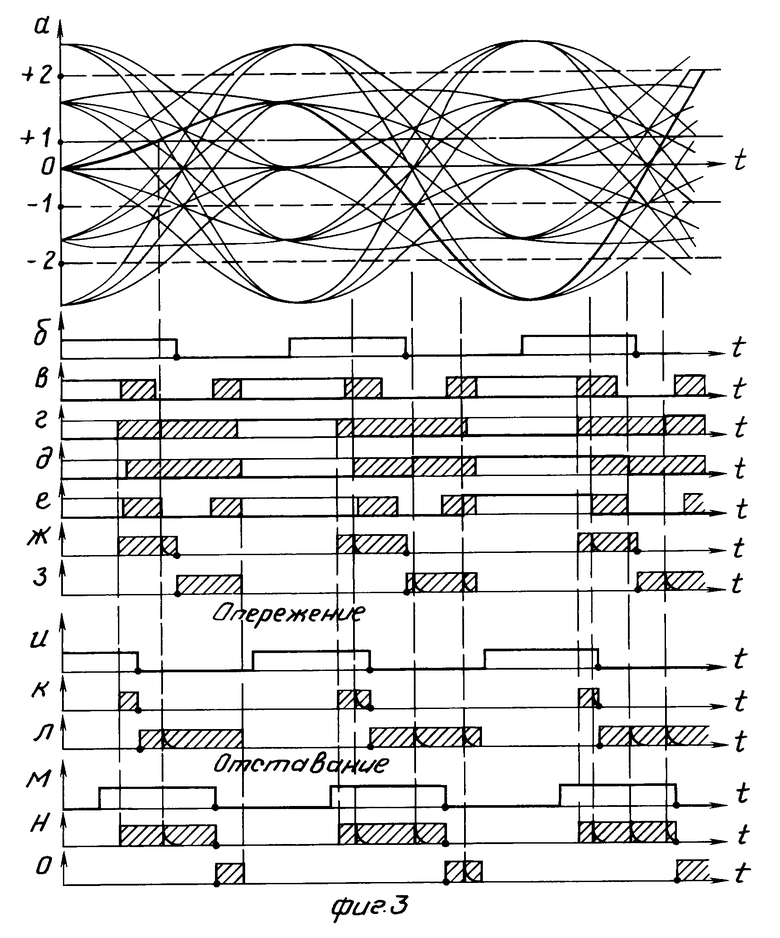

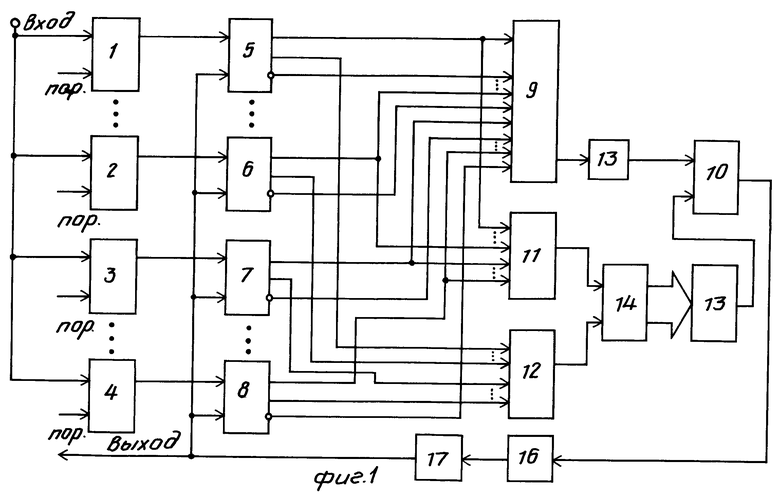

На фиг. 1 представлена структурная электрическая схема устройства для выделения тактового синхросигнала из многоуровневого цифрового сигнала; на фиг. 2 схема цифрового дискриминатора фазы такта; на фиг. 3 временная диаграмма работы устройства.

Устройство для выделения тактового синхросигнала из многоуровневого цифрового сигнала содержит 2n компараторов 1 4, 2n цифровых дискриминаторов 5 8 фазы такта, первый и второй сумматоры 9 и 10, первый и второй блоки 11 и 12 объединения, фильтр 13 нижних частот (ФНЧ), реверсивный счетчик 14, резистивную матрицу 15, тактовый генератор 16, делитель 17 частоты. Каждый цифровой дискриминатор фазы такта содержит первый и второй D-триггеры 18, 19, элемент ИЛИ 20, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 21, третий D-триггер 22.

Устройство для выделения тактового синхросигнала из многоуровневого цифрового сигнала работает следующим образом.

Многоуровневый цифровой сигнал (см. фиг. 3,а, на которой утолщенной линией изображена одна из возможных траекторий сигнала), имеющий "открытую" глаз-диаграмму, поступает на первый вход 2n компараторов 1 4. В 2n компараторах 1 4 происходит сравнение текущего значения входного цифрового сигнала и порогового напряжения, определенного для каждого компаратора. На выходах компараторов 1 4 формируются однополярные прямоугольные импульсы, длительность которых соответствует времени превышения напряжения многоуровневого цифрового сигнала порогового напряжения Uпор (см. фиг. 3,в, г, д, е, где в заштрихованной зоне для рассматриваемого многоуровневого сигнала может находиться фронт или срез однополярных импульсов).

Прямоугольные однополярные импульсы с выхода 2n компараторов 1 4 поступают соответственно на входы 2n цифровых дискриминаторов 5 8 фазы такта, на тактовые входы которых поступают регулярные тактовые синхроимпульсы с номинально частотой, равной тактовой частоте многоуровневого сигнала, и со скважностью равной 2, формируемые последовательно соединенными тактовым генератором 16 и делителем 17 частоты (см. фиг. 3, б, и, м).

Входом цифрового дискриминатора 5 8 фазы такта (см. фиг. 2) является первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21, выход которого соединен с C-входом третьего D-триггера, включенного по схеме делителя частоты (инверсный выход соединен с D-входом) и формирующего сигнал для второго входа элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21, на выходе которого будет формироваться фронт импульса (переход из состояния лог. 0 в лог 1) при поступлении на его первый вход фронта или спада импульса, формируемого соответствующим компаратором 1 4. Таким образом, сигнал компаратора 1 4 (см. фиг. 3,в, г, д, е) после прохождения элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21 будет иметь количество фронтов в два раза больше, причем по времени эти фронты будут соответствовать фронту и срезу исходного сигнала компаратора.

В момент поступления фронта сигнала с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21 на объединенные C-входы первого 18 и второго 19 D-триггеров в указанные триггеры записывается значение сигнала, имеющее место в данный момент на объединенных D-входах первого 18 и второго 19 D-триггеров и являющихся тактовым входом цифровых дискриминаторов 5 8 фазы такта.

Если в момент фронта импульса на C-входах первого 18 и второго 19 D-триггеров на объединенных D-входах данных D-триггеров имеется сигнал лог. "0", но нулевое состояние первого 1 D-триггера 18 не изменится, а на прямом выходе второго D-триггера 19, находящемся до этого в единичном состоянии, сформируется сигнал лог. "0". Сформировавшийся при этом на инверсном выходе второго D-триггера 19 сигнал лог. "1" (см. фиг. 3,з, л, о, заштрихована зона, в которой возможно появление импульса) поступит на второй вход элемента ИЛИ 20, на первом входе которого имеется сигнал лог. "0", и на выходе элемента ИЛИ 20 появится сигнал лог. "1", который установит посредством воздействия на S-вход второго D-триггера 19 в исходное состояние лог. "1" на прямом выходе. Таким образом, на прямом и инверсном выходах второго D-триггера 19, являющихся соответствующими выходами цифровых дискриминаторов 5 8 фазы такта, формируются короткие импульсы вычитания и инверсного вычитания.

Если в момент фронта импульса на C-входах первого 18 и второго 19 D-триггеров на объединенных D-входах данных D-триггеров имеется сигнал лог. "1", то единичное состояние второго D-триггера 19 не изменится, а на прямом выходе первого D-триггера 18, находящемся до этого в нулевом состоянии, сформируется сигнал лог. "1" (см. фиг. 3,ж, к, н, заштрихована зона, в которой возможно появление импульса), который, поступая на первый вход элемента ИЛИ 20, приведет к появлению на ее выходе сигнала лог. "1", который установит воздействием на R-вход первый D-триггер 18 в исходное состояние лог. "0" на прямом выходе. Таким образом, на прямом выходе первого D-триггера 18, являющемся выходом добавления цифровых дискриминаторов 5 8 фазы такта (см. фиг. 3,ж, к, н), формируются короткие импульсы добавления.

Таким образом, при появлении фронта или среза импульса на входе цифрового дискриминатора 5 8 фазы такта на его выходах добавления и вычитания будут появляться короткие импульсы (см. фиг. 3,ж, з, к, л, н, о). Причем импульс добавления будет появляться, если указанный фронт на первом входе цифрового дискриминатора 5 8 фазы такта возникает при наличии сигнала лог. "1" на тактовом входе цифрового дискриминатора 5 8 фазы такта, а импульс вычитания при наличии сигнала лог. "0" на тактовом входе цифрового дискриминатора 5 8 фазы такта.

Из глаз-диаграмм очевидно, что количество импульсов добавления и вычитания за время наблюдения будет равно на соответствующих выходах цифровых дискриминаторов 5 8 фазы тактов в том случае, если сигнал тактовой частоты с выхода делителя 17 частоты будет изменяться (переход из лог. "0" в лог. "1" или наоборот) в моменты времени, соответствующие середине "замытости" глаз-диаграммы (см. фиг. 3, ж, з), а при симметричности глаз-диаграммы и скважности синхроимпульса равной 2 фронт или срез тактового синхросигнала будет появляться в значащие моменты многоуровневого цифрового сигнала, т.е. в месте максимального раскрыва глаз-диаграммы. Это состояние свидетельствует о синхронизме.

При смещении во времени глаз-диаграммы относительно тактовых синхроимпульсов в пределах тактового интервала относительно положения при синхронном состоянии будет однозначно изменяться и соотношение количества импульсов на выходах добавления и вычитания цифровых дискриминаторов 5 8 фазы такта за время наблюдения (см. фиг. 3,к, л, н, о). Например, при отставании количество импульсов добавления увеличивается (фиг. 3,н), а количество импульсов вычитания уменьшается (см. фиг. 3,о), при опережении наоборот (см. фиг. 3,к, л).

При прекращении изменения многоуровневого цифрового сигнала (передача одного уровня, прекращение передачи информации, обрыва линии и т.п.) на выходах добавления и вычитания цифровых дискриминаторов 5 8 фазы такта прекращают появляться импульсы, что используется для прекращения подстройки частоты и фазы тактового генератора 16, т.е. автоматически обеспечивается режим "запоминания" частоты и фазы.

В динамическом режиме, когда многоуровневой цифровой сигнал принимает значения, соответствующие передаваемой информации, а тактовый синхросигнал формируется последовательно соединенным тактовым генератором 16 и делителем 17 частоты, поддержание требуемых временных соотношений между этими сигналами обеспечивается за счет управления частотой и фазой тактового генератора. Указанный сигнал управления получается посредством обработки сигналов с выходов цифровых дискриминаторов 5 8 фазы такта. Обработка сигнала обеспечивается по двум ветвям, в результате которой полученные сигналы суммируются во втором сумматоре 10, с выхода которого результирующий сигнал поступает на тактовый генератор 16.

В первой ветви, содержащей первый и второй блоки 11, 12 объединения, реверсивный счетчик 14 и резистивную матрицу 15 и являющейся по сути интегратором, построенным на базе реверсивного счетчика и обеспечивающим остатизм по фазе устройства, происходит интегрирование сигналов с выходов цифровых дискриминаторов 5 8 фазы тактов. Короткие импульсы добавления с выходов добавления 2n цифровых дискриминаторов 5 8 фазы тактов логически объединяются в первом блок 11 объединения, а короткие импульсы вычитания с 2n цифровых дискриминаторов 5 8 фазы тактов логически объединяются во втором блоке 12 объединения. С выхода первого блока 11 объединения импульсы добавления будут поступать на вход добавления реверсивного счетчика 14, увеличивая значение кодовой комбинации на его выходе, а с выхода второго блока 12 объединения импульсы вычитания будут поступать на вход вычитания реверсивного счетчика 14, уменьшая значение комбинации на его выходе. Первый и второй блоки 11, 12 объединения могут быть выполнены, например, в виде многовходового логического элемента ИЛИ. Кодовая комбинация с выхода реверсивного счетчика 14 посредством резистивной матрицы 15, подключенной к его выходу, преобразуется в соответствующий квантованный по уровню сигнал, который поступает на второй вход второго сумматора 10.

Во второй ветви, содержащей последовательно соединенные первый сумматор 9 и фильтр 13 нижних частот, выход которого подключен к первому входу второго сумматора 10, формируется сигнал пропорционального управления подстройки частоты и фазы тактового генератора 16, обеспечивая требуемые динамические свойства данной замкнутой системы автоматического регулирования.

Импульсы добавления и инверсного вычитания с соответствующих выходов добавления и инверсного вычитания 2n цифровых дискриминаторов 5 8 фазы такта поступают на 4n входов первого сумматора 9, в синхронном состоянии количество импульсов добавления и вычитания за время наблюдения одинаково. Импульсы вычитания снимаются с инверсного выхода, а импульсы добавления с прямого, и следовательно, взаимно компенсируются, в результате результирующий сигнал на выходе первого сумматора 9 будет соответствовать половинному значению размахов всех импульсов добавления и инверсного вычитания. Такое же значение сигнала на выходе первого сумматора 9 будет при прекращении изменений многоуровневого цифрового сигнала, т.е. в режиме "запоминания" частоты и фазы данная ветвь вносит такую же составляющую, как и при синхронном состоянии.

При смещении во времени глаз-диаграммы относительно тактовых синхроимпульсов в пределах тактового интервала относительно положения при синхронном состоянии будет однозначно изменяться и соотношение количества импульсов на выходах добавления и вычитания цифровых дискриминаторов 5 8 фазы такта за время наблюдения (см. фиг. 3,ж, з, к, л, н, о). Например, при отставании количество импульсов добавления увеличивается (см. фиг. 3, н), а импульсов вычитания уменьшается (см. фиг. 3, о), при опережении наоборот (см. фиг. 3, к, л). В этом случае при сложении импульсов добавления и инверсных импульсов вычитания в первом сумматоре 9 будет соответственно увеличиваться или уменьшаться постоянная составляющая его выходного сигнала, который, проходя через фильтр 13 нижних частот (в котором будут задерживаться нежелательные компоненты), воздействует на подстройку частоты и фазы тактового генератора 16.

Следует отметить, что сформированные сигналы в рассматриваемой первой и второй ветвях должны иметь такой закон изменения, чтобы компенсировать возникающее отклонение от синхронного состояния системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИЕМНИК ИМПУЛЬСНЫХ РАДИОСИГНАЛОВ И ИЗМЕРИТЕЛЬ УРОВНЯ ДЛЯ НЕГО | 1996 |

|

RU2097922C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| Устройство для синхронизации сигналов воспроизведения цифровой информации | 1986 |

|

SU1462413A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ТЕЛЕГРАФНЫХ РАДИОСИГНАЛОВ | 1990 |

|

RU2009615C1 |

| СЕЛЕКТИВНОЕ УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОДНОФАЗНЫХ ЗАМЫКАНИЙ В КАБЕЛЬНЫХ ЛИНИЯХ | 2002 |

|

RU2217769C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИЕМОПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2209524C2 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2002 |

|

RU2231912C2 |

| Цифровой фазовый детектор для синтезаторов частот | 1988 |

|

SU1539677A1 |

Использование: в технике связи, а именно в высокоэффективных системах связи для восстановления временных характеристик многоуровневого цифрового сигнала электросвязи. Сущность изобретения: устройство содержит 2n компараторов 1-4, 2n цифровых дискриминаторов 5-8 фазы такта, первый и второй сумматоры 9,10, первый и второй блоки 11,12 объединения, фильтр 13 нижних частот, реверсивный счетчик 14, резистивную матрицу 15, тактовый генератор 16, делитель частоты 17. Устройство позволяет выделить тактовый синхросигнал из многоуровневых цифровых сигналов, которые могут иметь длинные последовательности одинаковых символов цифрового сигнала без возврата к нулю. 1 з.п. ф-лы, 3 ил.

| Устройство для регенерации цифрового сигнала | 1981 |

|

SU1054911A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-04-20—Публикация

1992-05-21—Подача