выход опорного генератора подключен к опорному входу преобразователя

1125748

кода в число импульсов формирователя последовательности импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОНТРОЛЯ СИНХРОНИЗМА КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1993 |

|

RU2057395C1 |

| Устройство автоматической подстройки частоты | 1989 |

|

SU1698987A1 |

| Индикатор синхронизма цифровой системы фазовой автоподстройки частоты | 1987 |

|

SU1596282A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1693735A1 |

| Устройство для измерения преобладаний двоичных сигналов | 1986 |

|

SU1338102A2 |

| Цифровая система фазовой автоподстройки частоты | 1983 |

|

SU1149405A1 |

| Устройство синхронизации | 1979 |

|

SU773944A1 |

| Цифровое устройство фазовой синхронизации | 1985 |

|

SU1358103A1 |

| Устройство для синхронизации канала воспроизведения данных | 1989 |

|

SU1674245A1 |

УСТРОЙСТВО ЦИФРОВОЙ ФАЗОВОЙ АВТОПОДСТРОЙКЙ ЧАСТОТЫ, содержащее соединенные последовательно опорный генератор, блок добавления-вычитания импульсов, делитель частоты, цифровой фазовый детектор, другой вход которого является сигнальным входом устройства цифровой фазовой автоподстройки частоты, цифровой интегратор, вход опорной частоты которого подключен к опорному генератору, и сумматор, выходы которого подключены к дополнительным входам блока добавления-вычитания импульсов, а также блок усреднения, входы которого подключены к выходам цифрового фазового детектора, при этом блок усреднения выполнен в виде реверсивного счетчика, входы которого являются входами блока усреднения, первого ивторого Т-тригге,ров, первого и.второго элементов ,И, и-вход первого Т-триггера подключен к первому выходу реверсивного счетчика, выход Т-триггера подключен к одному входу первого элемента И, другой вход которого соединен с К входом второго Т триггера и одним входом блока усреднения. 3-вход второго Т-триггера подключен к второму выходу реверсивного счетчика, выход второго Т-триггера подключен к одному входу второго элемента И, другой вход которого соединен с К-входом первого Т-триггера и другим входом блока усреднения, отличающееся тем, что, с Целью уменьшения времени вхождения в синхронизм, между выходами Т-триггеров блока усреднения и вторыми входами сумматора включены тре- . тий и четвертый элементы И, вторые входы которых объединены, между выходами первого и второго элементов И блока усреднения и объединенными S вторыми входами третьего и четвертого элементов И включены последовательно элемент ИЛИ и формирователь последовательности импульсов, выполненный в виде последовательно соединенных пятого элемента И, вход которого является входом формирователя последовательности импульсов, счетчика, вход сброса которого является С входом обнул:ения устройства циф:д ч ровой фазовой автоподстройки частоты и преобразователя кодов в число им1 пульсов, выход которого является X) выходом формирователя последовательности импульсов, при этом неинверсные выходы всех регистров счетчика, кроме старшего, соединены с управляющими входами преобразователя кода в число импульсов, инверсный выход старшего разряда счетчика соединен с вторым входом пятого элемента И, установочный BXOJJ преобразователя кода в число импульсов соединен с входом формирователя последовательности импульсов, при этом

Изобретение относится к радиотехнике, а именно к устройствам синхронизации с цифровой фазовой автоподстройкой частоты, применяемым в аппаратуре связи, радионавигации и дру гих радиотехнических системах.

Известен дискретный синхронизатор, представляющий собой устройство цифровой- автоподстройки частоты, содержащее задаюпщй генератор, схему добавления-вычитания, управляемый делитель, схему вьщеления фазовых искажений, входное устройство, реверсивный счетчик, схему записи единиц с двумя выходами, схему авто сброса единиц, анализатор, сумматоры кольцевой регистр добавления и кольцевой регистр вычитания СО.

Недостатком этого устройства является большое время вхождения в синхронизм вследствие ряда причин. Анализатор зтого устройства позволяет обеспечить первоначальный ввод в синхронизм лишь по частоте путем измерения входной частоты и последующей подстройки управляемого делителя. Поскольку измерение частоты входного сигнала производится заполнением временного интервала входной частоты измерительными импульсами задающего генератора, то при малом соотношении сигяал/вгум достаточно трудно достичь точности анализа даже при многократном измерении. Ввод в синхронизм по фазе осзгществляется известным способом.

Наиболее близким к изобретению по технической сущности является устройство цифровой фазовой автоподстройки частоты, содержащее соединение последовательно опорный генератор, блок добавления-вычитания импульсов, делитель частоты, цифрово фазовый детектор, другой.вход которого является сигнальным входом устройства цифровой фазовой автоподстроки частоты, цифровой интегратор, вхо опорной частоты которого подключен к опорному генератору, и сумматор.

выходы которого подключены к дополнительным входам блока добавления-вычитания импульсов, а также блок усредусреднения, входы которого подключены к.выходам цифрового фазового детектора, при этом блок усреднения выпатнен в виде реверсивного счетчика, входы которого являются входами блока усреднения, первого и второго Т триггеров, первого и второго элементов И, J-вхо первого Т-триггера подключен к первому выходу реверсивного счетчика, вход первого Т-триггера подключен к одному входу первого элемента И, другой вход которого соединен с К-входом второго Т-триггера и одним входом блока усреднения. Э-вход второго Т-триггера подключен к второму выходу реверсивного счетчика, выход второго Т-триггера подключен к одному входу второго элемента И, другой вход к.оторого соединен с К-входом первого Т-триггера и другим входом блока усреднения С23.

Целью изобретения является уменьшение времени вхождения в синхронизм.

Поставленная цель достигается тем, что в устройстве цифровой фазовой автоподстройки частоты, содержащем соединенные последовательно опорный генератор, блок добавления-вычитания импульсов, делитель .частоты, цифровой фазовый детектор, другой вход которого является сигнальным входом устройства цифровой фазовой автоподстройки частоты, дафровой интегратор, вход опорной частоты которого подключен к опорному генератору, и сумматор, выходы которого подключены к дополнительным входам блока добавления-вычитания импульсов, а также блок усреднения, входы которого подключены к выходам цифрового фазового детектора, при этом блок усреднения выполнен в виде реверсивного счетчика, входы которого являются входами блока усреднения, первого и второго Т-триггеров первого и второго элементов И, J-вход первого Т-триггера полключен к первому

выходу реверсивного счетчика, выход первого Т-триггера подключен к одному входу первого элемента И, другой вход которого соединен с К-входом второго Т-триггера и одним входом блока усреднения. 3-вход второго Т-триггера подключен к второму выходу реверсивного счетчика, выход второго Т-триггера подключен к одному входу второго элемента И, другой йход которого соединен с Квходом первого Т-триггера и другим входом блока усреднения, между выходами Т-триггеров блока усреднения и вторыми входами сумматора включены третий и четвертый элементы И, вторые входы которых объединены, между выходами первого и второго элементов И блока усреднения и объединеными вторыми входами третьего и .четвертого элементов И включены последовательно элемент ИЛИ и формирователь последовательности импульсов, ,выполненный в виде последовательно соединенных пятого элемента И, вход которого является входом формирователя последовательности импульсо счетчика, вход сброса которого является входом обнуления устройства цифровой фазовой автоподстройки час тоты, и преобразователя кода в число импульсов, вькод которого является выходом формирователя последовательности импульсов, при этом инверсные выходы всех регистров счетчй ка, кроме старшего, соединены с управляющими входами преобразователя кода в число импульсов, инверсный выход старшего разряда счетчика соединен с вторым входом пятого элемента И, установочнь1й вход преобразователя кода в число импульсов соединен с входом формирователя последовательности импульсов, при этом выход опорного генератора подключен к опорному в5соду преобразователя кода в число импульсов формирователя последовательности импульсов.

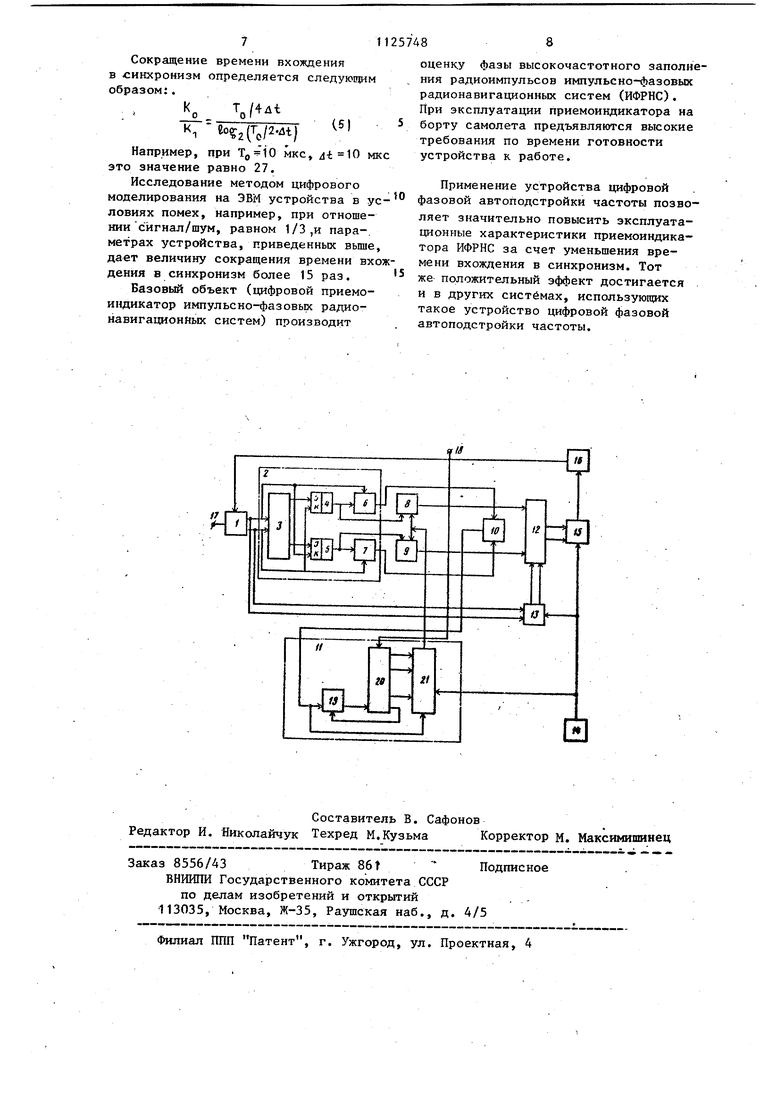

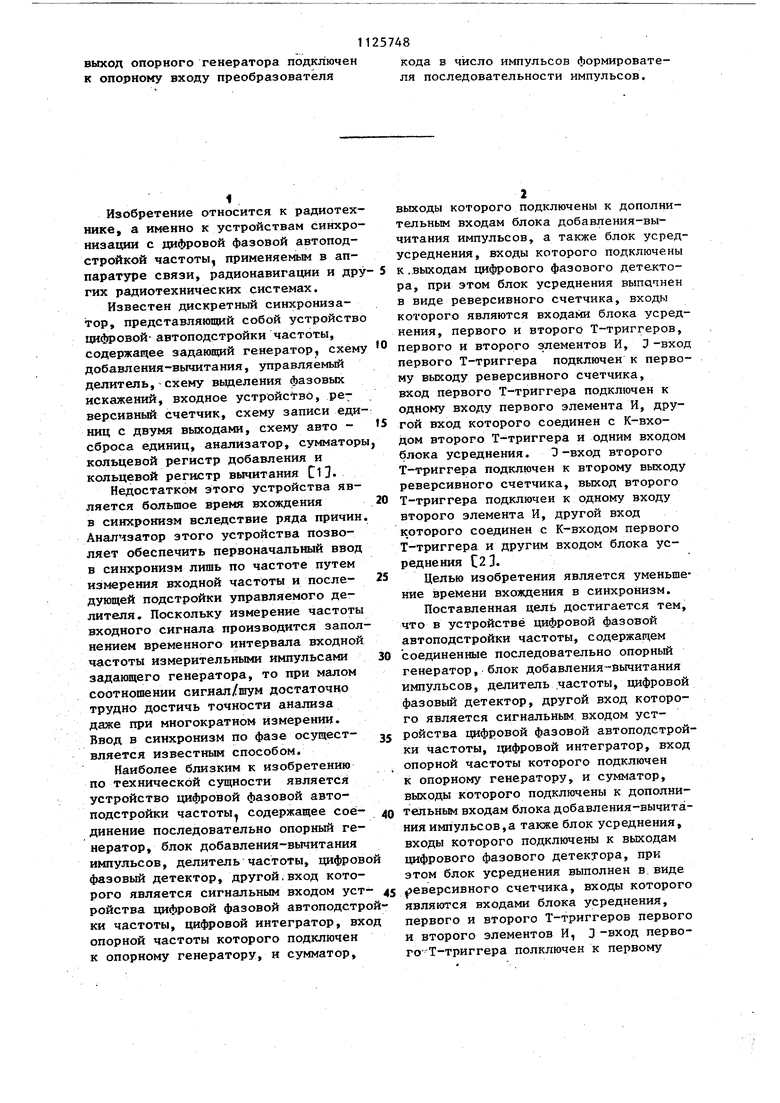

На чертеже представлена структурная электрическая схема устройства цифровой фазовой автоподстройки частоты.

Устройство содержит цифровой фазовый детектор 1, блок 2 усреднения, который выполнен в виде ревер-i сивного счетчика 3, первого 4 и второго 5 Т-триггеров, первого 6 и второго 7 элементов И, третий 8 и четвертый 9 элементы И, элемент ИЛИ 10, формирователь 11 последовательности импульсов, сумматор 12, цифровой интегратор 13, опорный генератор 14, блок 15 добавления-вычитания импульсов, делитель 16 частоты, сигнальный вход 17 и вход 18 обнуления устройства цифровой фазовой автоподстройки частоты.

Формирователь 11 последовательност импульсов содержит пятый элемент И 19 счетчик 20 и преобразователь 21 кода в число импульсов.

Устройство работает следующим образом.

В режиме синхронизма входной сигна поступает с сигнального входа 17 на вход цифрового фазового детектора 1, на второй вход которого поступает выходной сигнал делителя 16 частоты (выходной сигнал цифрового подстраиваемого генератора, образованного последовательным соединением опорного генератора 14, блока 15 добавлениявычитания импульсов и делителя 16 частоты)..

Сигналы рассогласования с выходов цифрового фазового детектора 1 поступают на входы цифрового интегратора 13 и реверсивного счетчика 3 блока 2 усреднения, а сигналы с выходов Т-триггеров 4 или 5 через элементы И 8 или 9 - на входы сумматора 12, на другие входы которого поступает импульс, с выхода цифрового интегратора 13. Суммарные последовательности импульсов с выходов сумматора 12 поступают на входы добавления и вычитания импульсов блока 15 добавления- вычитания импульсов в зависимости от знака частотного рассогласования входного и выходного сигналов на входе 1у1фрового фазового детектора 1 , В блоке 15 добавления-вычитания импульсов осуществляется исключение или добавление одного импульса в последовательность импульсов, поступаюи1их от опорного генератора 14 Таким образом, на каждый импульс с одного или другого выхода сумматора 12 выходной сигнал делителя 16 частоты сдвигается на дискрет фазы , dt с соответствующим знаком в сторо- ну уменьшения начального рассогласования.

В режиме ввода в синхронизм выходными сигналами цифрового интегратора 13 можно в первом приближении пренеб5речь в силу его большой постоянной времени. Импульсы переполнения блок 2 усреднения с выходов элементов И .6 и 7 поступают на входы элемента ИЛИ 10 и далее на вход формирователя 11 последовательности импульсов. Формирователь последовательности импульсов работает следующим образом. Импульсы с выхода пятого элемента И 19 поступают на счетчик 20, котсзрый имеет коэффициент счета М и далее на преобразователь 21 кода в число импульсов, Сигнал с ин версного выхода счетчика 20 формиро вателя 11 последовательностей импул сов разрешает прохождение импульсов с входа пятого элемента И 19 на счётный вход счетчика 20 через элемент И 19. Каждый из этих импульсов переключает счетчик 20, который управляет работой преобразователя 21 кода в число импульсов так, чтобы на первый импульс на вьсходе формирователя 11 .последовательности импульсов формировалось N импульсов, на второй импульс N/2 импульсов и т.д. При включении М-«-1 разряда счетчика 20 его инверсный выход зак вает пятый элемент И 19, и переключение счетчика 20 прекращается. Теперь на выходе формирователя 11 последовательности импульсов формируется импульс при поступлении на вход одного импульса. Таким образом, на каждый импульс переполнения блока 2 усреднения формируется последовательность импульсов с к личествам импульсов в 2 раза меньше чем предьщущие, и это продолжается до тех пор, пока количество импульсов в выходной последовательности формирователя 11 последовательности импульсов не станет равным единице. Затем в синхронизм входит петля сле жения по частоте, включающая цифровой интегратор t3, Число импульсов, формируемых на выходе формирователя 11 последовательности импульсов на первый сигнал переполнения блока 2 усреднения обеспечивает сдвиг выходной последо вательности делителя 16 частоты на Т-/4, т.е. 8 где TO - период выходной последовательности делителя 16 частоты/ М - дискрет фазы. При отсутствии помех на входе устройства цифровой фазовой автоподстройки частоты сокращение времени вхождения в синхронизм определяется аналитически. Поскольку априор1ное фазовое рассогласование является случай ной величиной, равномерно распределенной на интервале (0-Т/2), то среднее значение фазового рассогласования равно T ilS/i 2 - Для устранения такой расстройки необходимо подать на вход цифрового подстраиваемого генератора (на вход блока 15 добавления-вычитания импульсов) Кд импульсов, каждый из которых обеспечивает сдвиг фазы выходного сигнала цифрового подстраиваемого генератора на 4t. Это количество импульсов равно Т.е. совпадает с числом импульсов, определяемых формулой (1). В устройстве цифровой фазовой автоподстройки частоты формирователь 11 последовательности импульсов позволяет обеспечить сдвиг фазы выходного сигнала цифрового подстраиваемого генератора на каждый импульс переполнения на выходе блока 2 ус-т реднения сначала на , затем на Т и/8 и далее до 4% . Таким образом, функциональную зависимость числа импульсов, поступающих на вход цифрового подстраиваемого генератора, можно выразить следующим образом. К,Н2 4t / Как следует из формулы (4), чисо импульсов К такое, которое неободимо для устранения максимальной ервоначальной фазОвой расстройки, авной То/2, Тп/2. т.е. число импульсов «j не зависит- от величины перво ачальной фазовой расстройки. Сокращение времени вхождения в синхронизм определяется следующим образом:. Т /4At ЧгГс/ ) Например, при Тд-10 икс /i-t 10 ик это значение равно 27. Исследование методом цифрового моделирования на ЭВМ устройства в у ловиях помех, например, при отношении сигнал/шум, равном 1/3,и пара-, метрах устройства, приведенных вьпие дает величину сокращения времени вх дения в синхронизм более 15 раз. Базовый объект (цифровой приемоиндикатор импульсно-фазовьк радионавигационных систем) производит оценку фазы высокочастотного заполнения радиоимпульсов импульсно-фазовьк радионавигационных систем (ИФРНС). При эксплуатации приемоиндикатора на борту самолета предъявляются высокие требования по времени готовности устройства к работе. Применение устройства цифровой фазовой автоподстройки частоты позволяет значительно повысить эксплуатационные характеристики приемоиндикатора ИФРНС за счет уменьшения времени вхождения в синхронизм. Тот же положительный эффект достигается и в других системах, использующих такое устройство цифровой фазовой автоподстройки частоты.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дисретный синхронизатор | 1977 |

|

SU651446A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Шахгильдян В.В | |||

| и др | |||

| Системы фазовой автоподстройки частоты с элементами дискретизации | |||

| М., Связь, 1979, С.152, рис.4.29 (прототип). | |||

Авторы

Даты

1984-11-23—Публикация

1982-03-03—Подача