роля мпкропроЦессорньк блоков за счет возможности программирования алгоритмов контроля при различных сочетаниях временных параметров синхропоследова- тельностей объекта контроля. Перед началом проверки с помощью блока 12 ввода производится загрузка хранимых тестов в блок 10 памяти, модифицированной матрицы переходных вероятное- тей и кодов, из которых генерируется марковская последовате.пьность, - в память формирователя 9 псевдослучайной последовательности, кодов управления блоком 5 мультиплексоров - в блок 6 сверхоперативной памяти, программы cbop пlpoвcчния периодических воз- действш II меток времени - в память формирователя 7 синхросерий, программы проверки обьекта контроля - в па- мять блока 1 управления. Очередное входное вояде 1ствие формируется путем суперпозипии хранимого теста из блока 10 памяти, исевдослуча Чного тес- та от генератора 8 и очередного кода марковской последовательности от формирователя 9. Необходимый источник подключается к блоку 1 регистров через блок 5 мультиплексоров. При суперпозиции выбор соответствующих полей задается управляющими кодами из блока 6 сверхоперативной памяти. Сиг}1алы синхронизации с выхода формирователя 7 подаются на контролируемый микропроцессорный блок 3 и эталонный блок 2 через блок 1 регистров. Блок 4 сравнения выполняет сравнение откликов и выдает результаты сравнения на блок 13 вывода и блок 11 управления. Подача входных воздействий и опрос (откликов блоков 2 и 3 вьтолняются в моменты времени, задавае -1ые программой контроля из памяти формирователя 7 синхросерий. 2 з.п. ф-лы, 10 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство контроля микропроцессорных блоков | 1982 |

|

SU1042023A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Генератор испытательных последовательностей | 1987 |

|

SU1543396A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

Изобретение относится к вычислительной технике, в частности к средствам контроля цифровых объектов, и позволяет реализовать алгоритмы контроля независимо от особенностей временных диаграмм сигналов синхронизации и протоколов обмена объекта контроля. Цель изобретения - расширение функциональных возможностей устройства для контроля микропроцессорных блоков за счет возможности программирования алгоритмов контроля при различных сочетаниях временных параметров синхропоследовательностей объекта контроля. Перед началом проверки с помощью блока 12 ввода производится загрузка хранимых тестов в блок 10 памяти, модифицированной матрицы переходных вероятностей и кодов, из которых генерируется марковская последовательность, - в память формирователя 9 псевдослучайной последовательности, кодов управления блоком 5 мультиплексоров - в блок 6 сверхоперативной памяти, программы формирования периодических воздействий и меток времени - в память формирователя 7 синхросерий, программы проверки объекта контроля - в память блока 11 управления. Очередное входное воздействие формируется путем суперпозиции хранимого теста из блока 10 памяти, псевдослучайного теста от генератора 8 и очередного кода марковской последовательности от формирователя 9. Необходимый источник подключается к блоку 1 регистров через блок 5 мультиплексоров. При суперпозиции выбор соответствующих полей задается управляющими кодами из блока 6 сверхоперативной памяти. Сигналы синхронизации с выхода формирователя 7 подаются на контролируемый микропроцессорный блок 3 и эталонный блок 2 через блок 1 регистров. Блок 4 сравнения выполняет сравнение откликов и выдает результаты сравнения на блок 13 вывода и блок 11 управления. Подача входных воздействий и опрос откликов блоков 2 и 3 выполняются в моменты времени, задаваемые программой контроля из памяти формирователя 7 синхросерий. 2 з.п.ф-лы, 10 ил.

Изобретение относится к вычислительной технике, в частности к средствам автоматического контроля цифро- вых объектов, и может быть использовано для высокочастотной функциональ- ной проверки микропроцессоров, блоков ЭВМ, построенных на основе микропроцессоров и других схем большой стпени интеграции, целых микро-ЭВМ и прочих сложных устройств в процессе

их производства и эксплуатации. I

Целью изобретения является расширение функциональных возможностей ус ройства за счет возможности программирования алгоритмов контроля при различных сочетаниях временных параметров синхропоследовательностей объекта контроля.

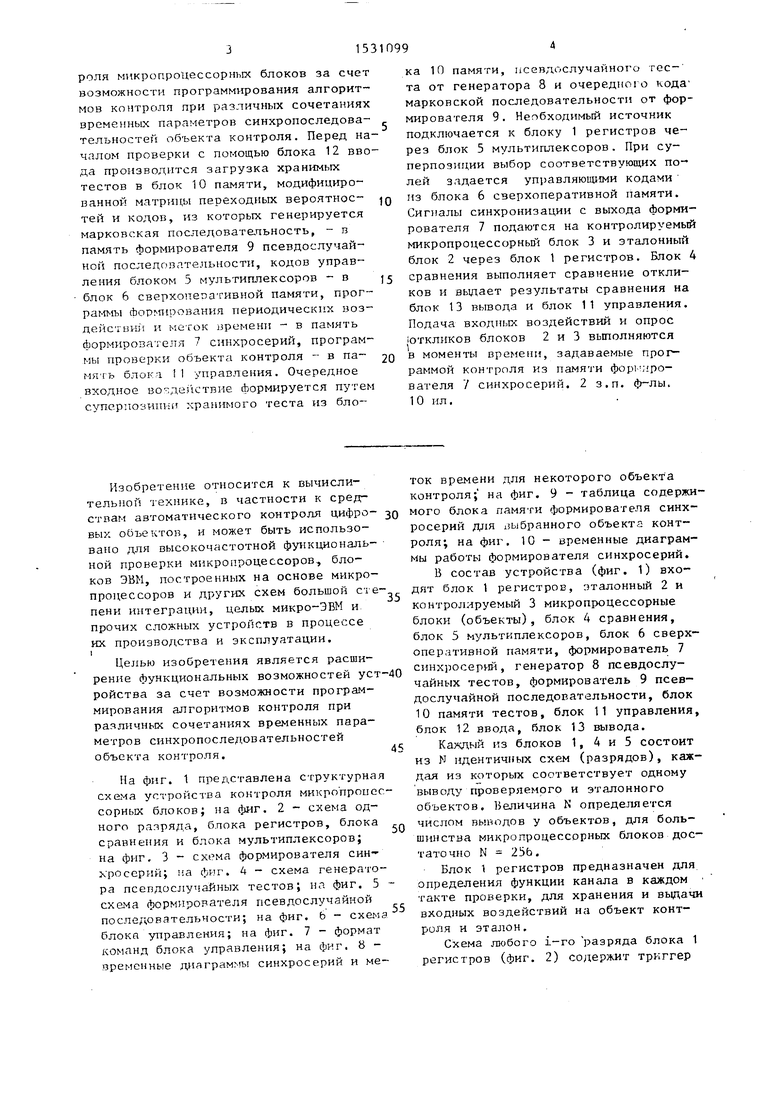

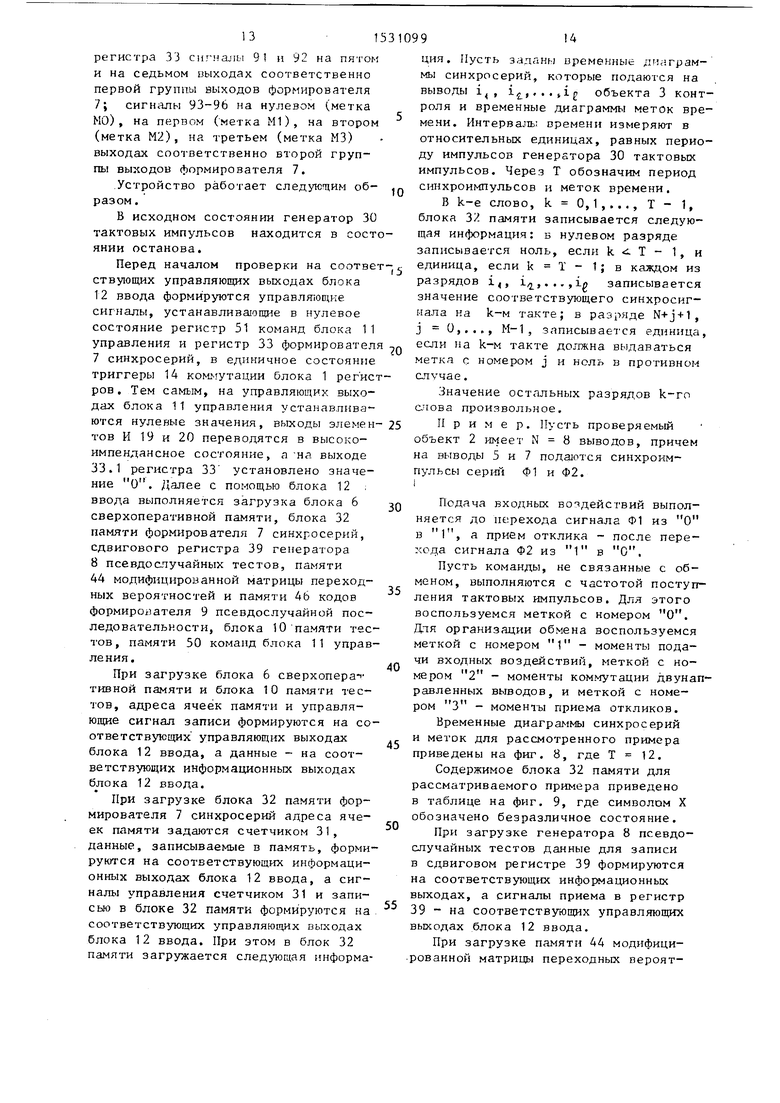

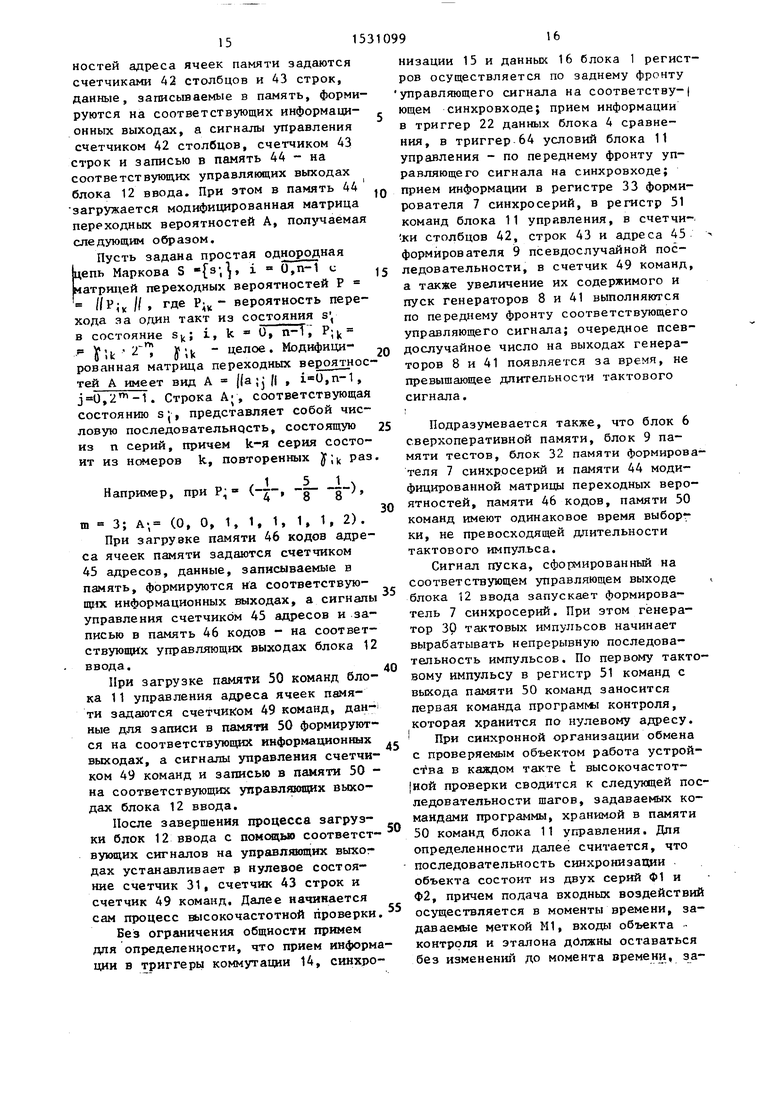

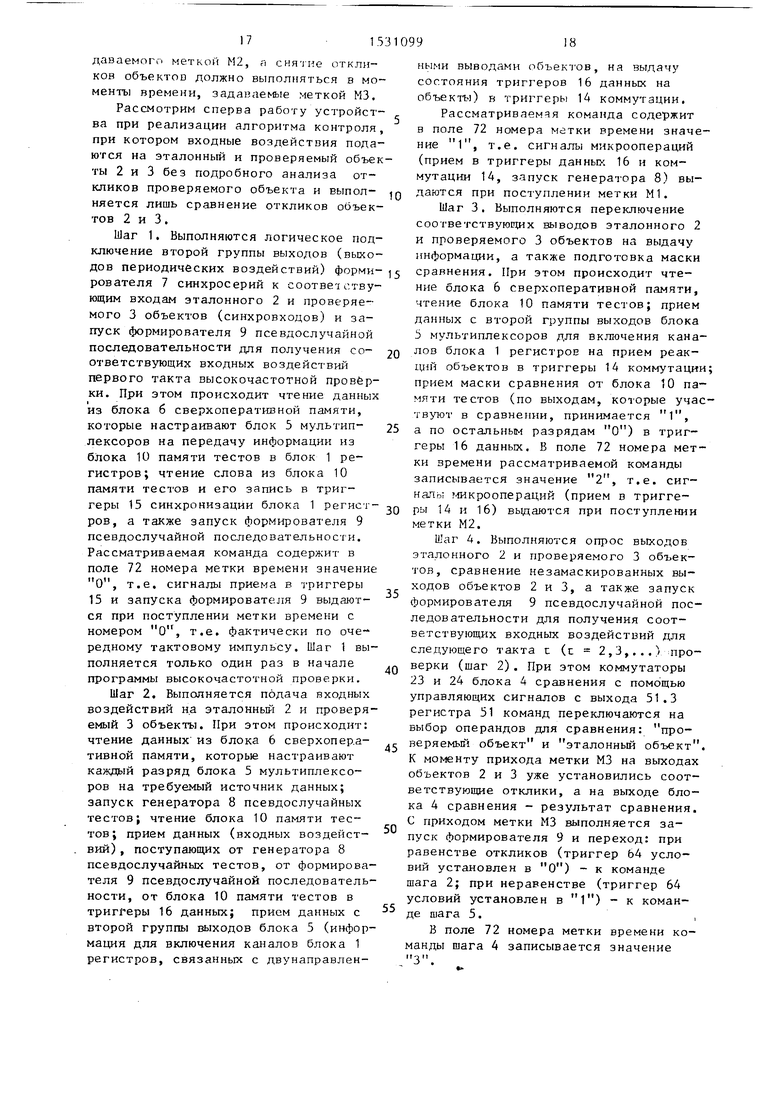

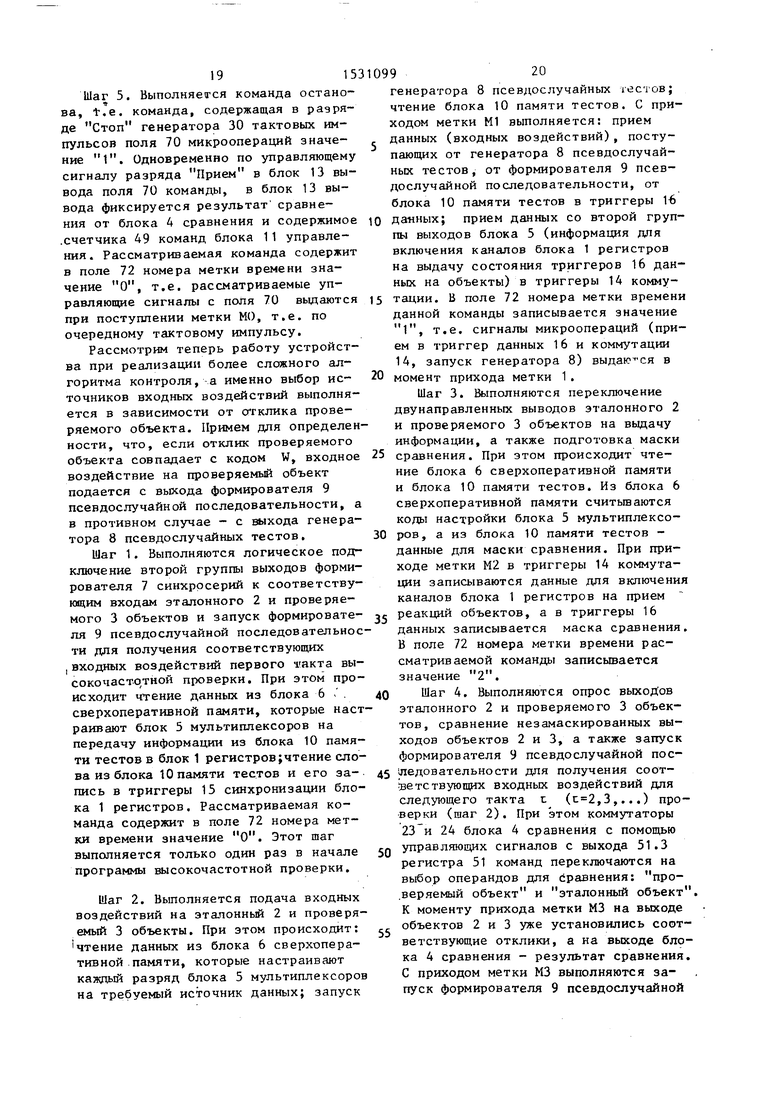

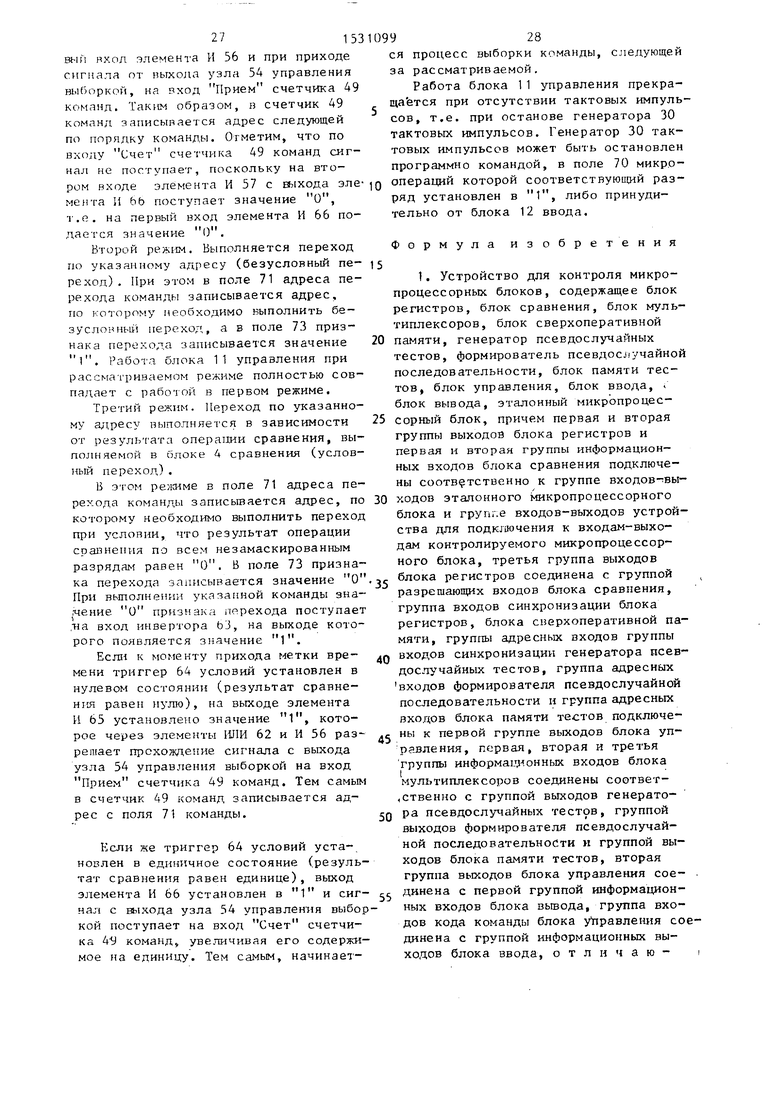

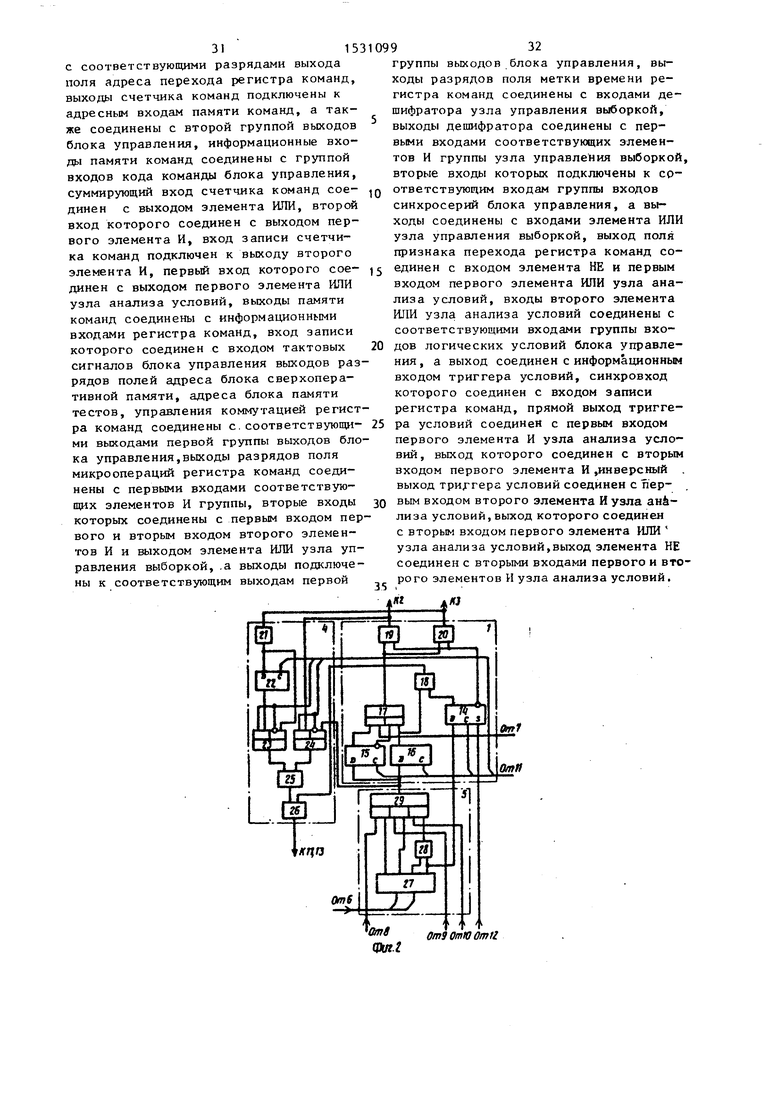

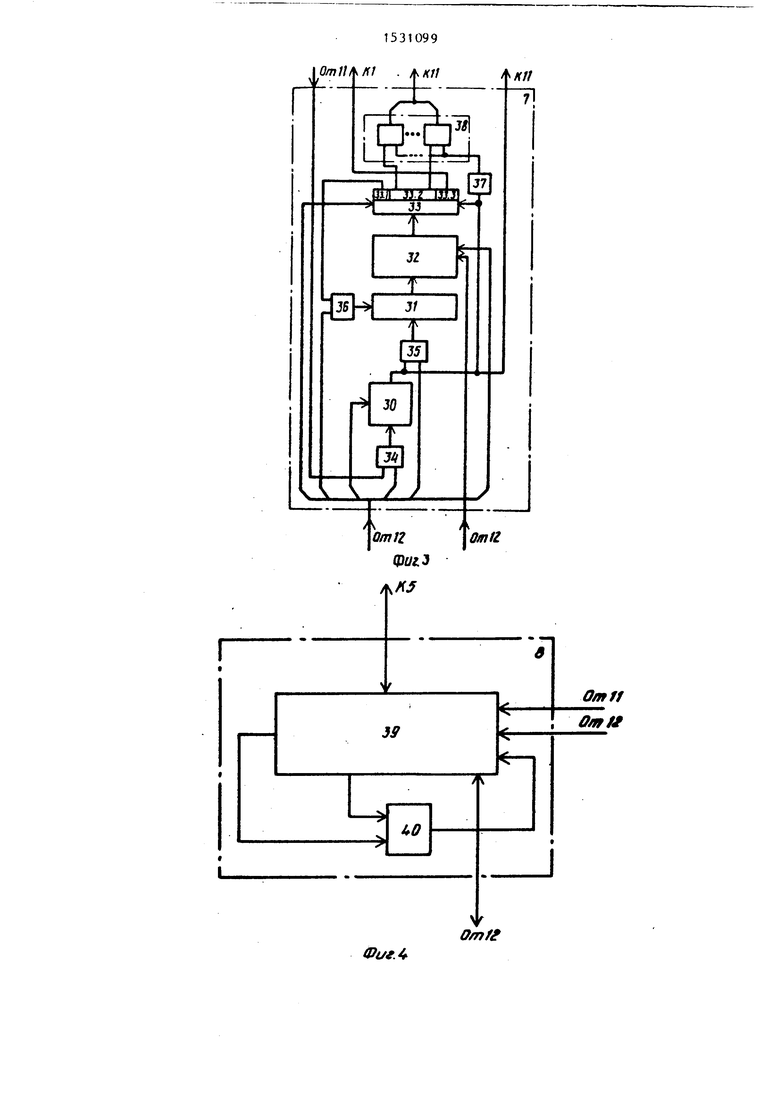

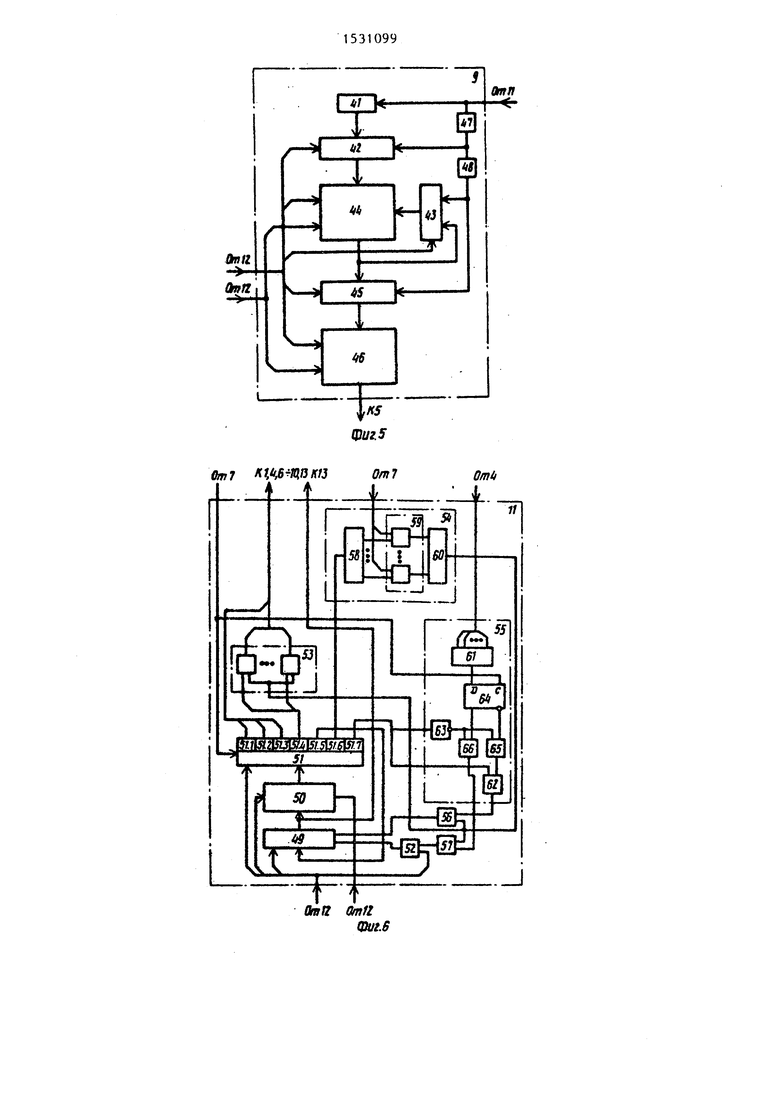

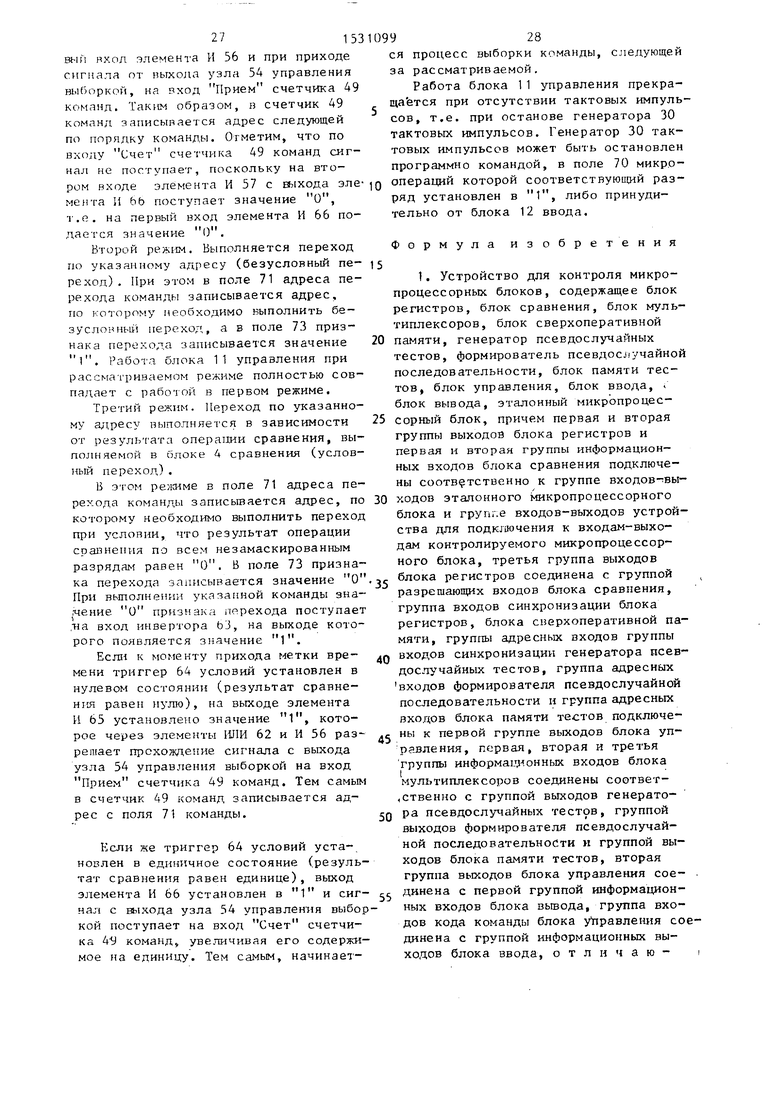

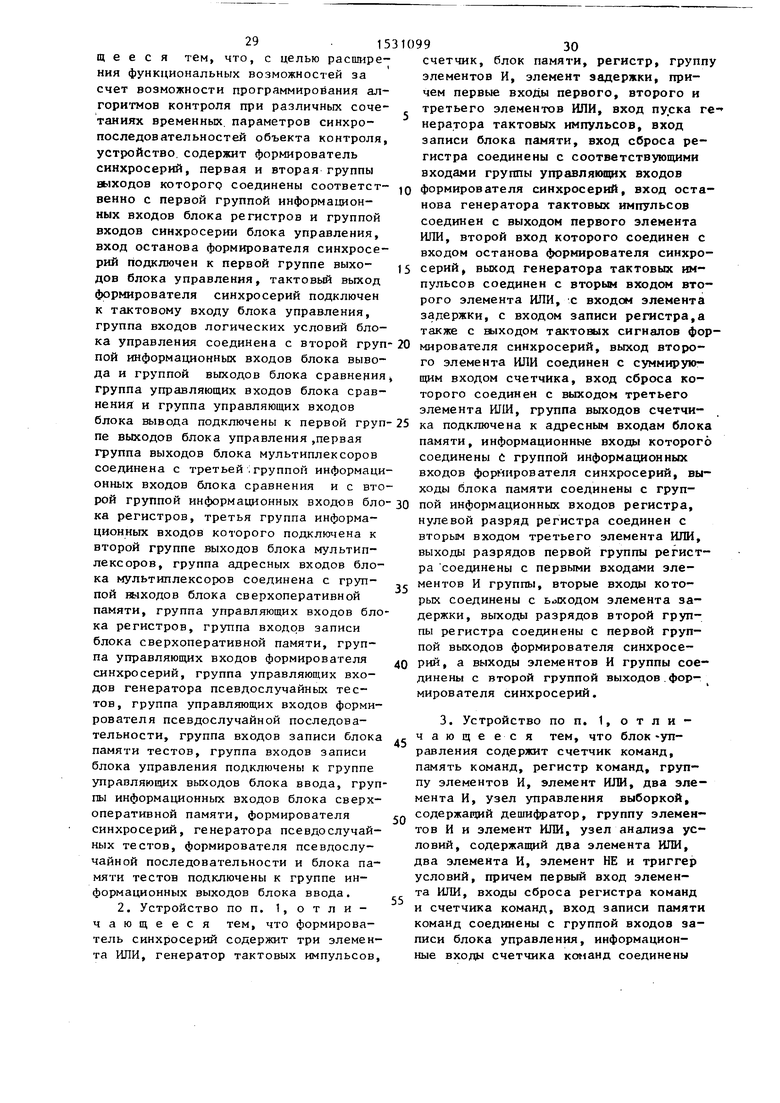

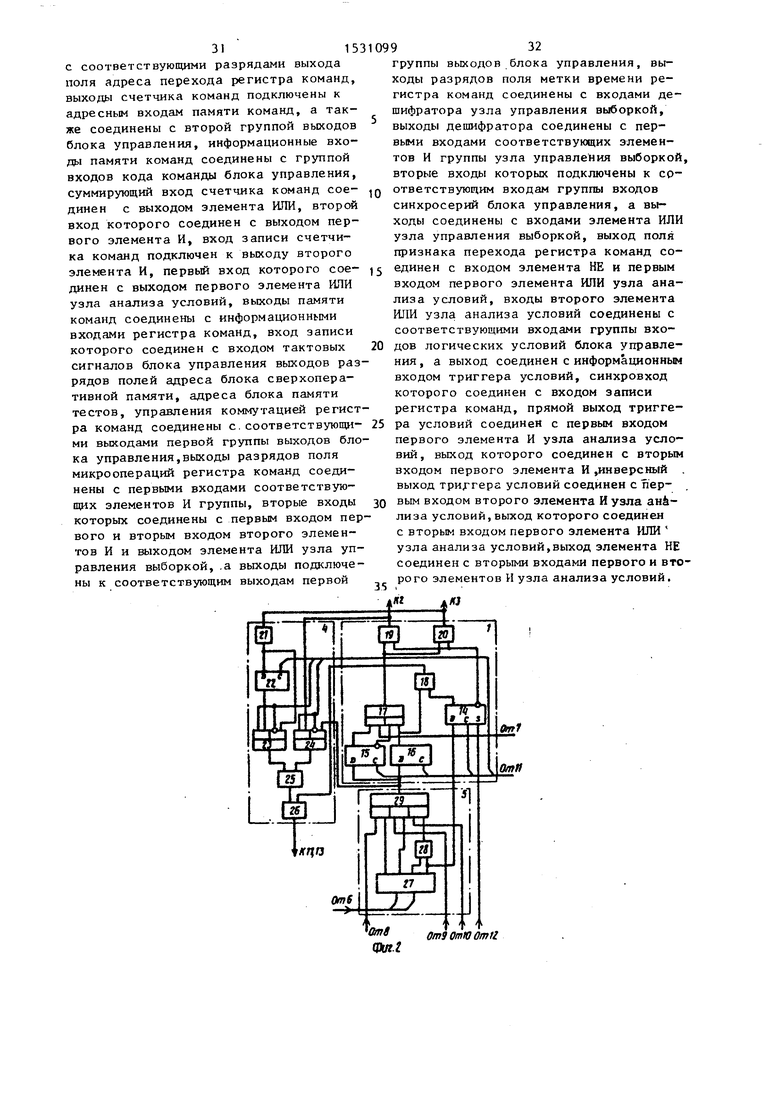

На фиг. 1 представлена структурная схема устройства контроля микропропес- сорных блоков; на фиг. 2 - схема одного разряда, блока регистров, блока сравнения и блока мультиплексоров; на фиг, 3 - схема формирователя синхросерий; на фиг. 4 - схема генератора псевдослучайных тестов; на фиг. 5 - схема формирователя псевдослучайной последовательности; на фиг. 6 - схема блока управления; на фиг. 7 - формат команд блока управления; на фиг. 8 - временные диаграм ы синхросерий и ме55

о

0

5

5

ток времени для некоторого объекта контроля; на фиг. 9 - таблица содержимого блока памяти формирователя синхросерий для выбранного объекта контроля; на фиг. 10 - временные диаграммы работы формирователя синхросерий.

В состав устройства (фиг. 1) входят блок 1 регистров, эталонный 2 и контролируемый 3 микропроцессорные блоки (объекты), блок 4 сравнения, блок 5 мультиплексоров, блок 6 сверхоперативной памяти, формирователь 7 синхросерий, генератор 8 псевдослучайных тестов, формирователь 9 псевдослучайной последовательности, блок 10 памяти тестов, блок 11 управления, блок 12 ввода, блок 13 вывода.

Каждый из блоков 1, 4 и 5 состоит из N идентичных схем (разрядов), каждая из которых соответствует одному выводу проверяемого и эталонного объектов. Величина N определяется числом выводов у объектов, для большинства микропроцессорных блоков достаточно N 235.

Блок 1 регистров предназначен для определения функции канала в каждом такте проверки, для хранения и выдачи входных воздействий на объект конт- роочя и эталон.

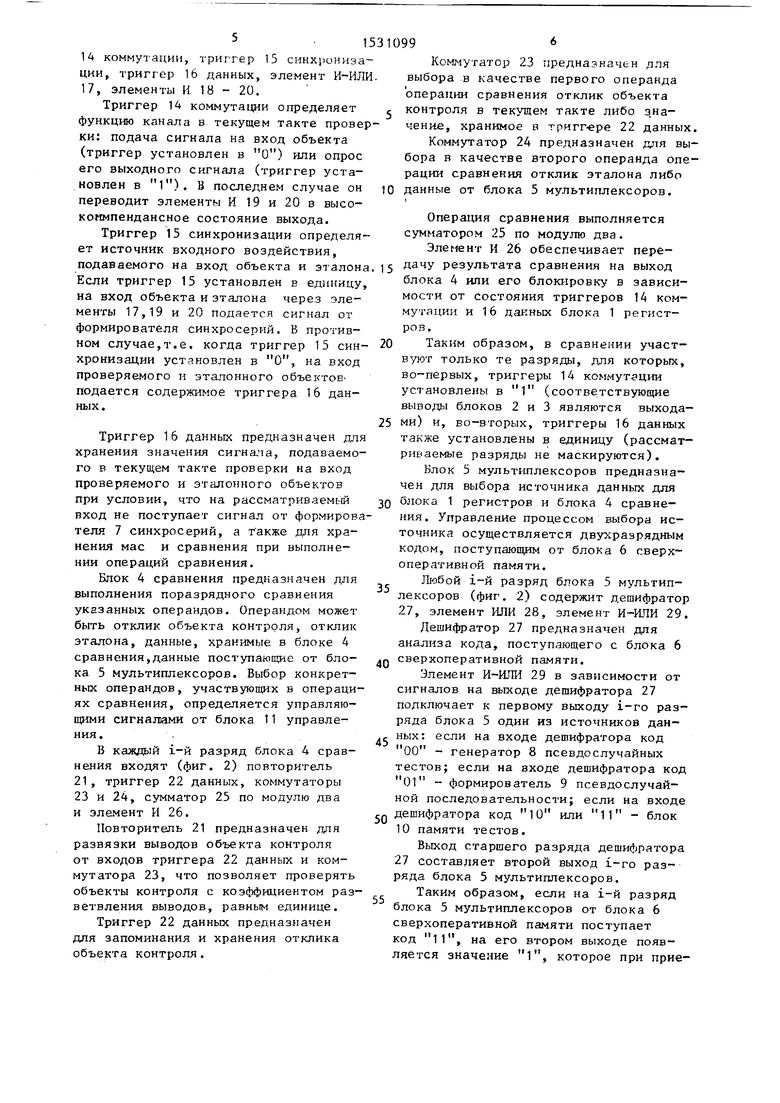

Схема любого i-ro разряда блока 1 регистров (фиг. 2) содержит триггер

51531099

коммутации, триггер 15 синхронизавыоп ко че

ции, триггер 16 данных, элемент И-ИЛ 17, элементы И 18 - 20.

Триггер 14 коммутации определяет функцию канала в текущем такте провеки: подача сигнала на вход объекта (триггер установлен в О) или опрос его выходного сигнала (триггер установлен в 1). В последнем случае он переводит элементы И 19 и 20 в высо- конмпендансное состояние выхода.

Триггер 15 синхронизации определяет источник входного воздействия, подаваемого на вход объекта и эталон Если триггер 15 установлен в едмиицу на вход объекта и эталона через элементы 17,19 и 20 подается сигнал от формирователя синхросерий. В противном случае,т.е. когда триггер 15 синхронизации установлен в О, на вход проверяемого и эталонного объектов подается содержимое триггера 16 данных.

Триггер 16 данных предназначен дл хранения значения сигнала, подаваемого в текущем такте проверки на вход проверяемого и эталонного объектов при условии, что на рассматриваемый вход не поступает сигнал от формировтеля 7 синхросерий, а т акже для хранения мае и сравнения при выполнении операций сравнения.

Блок 4 сравнения предназначен для выполнения поразрядного сравнения указанных операндов. Операндом может быть отклик объекта контроля, отклик эталона, данные, хранимые в блоке 4 сравнения,данные поступающие от блока 5 мультиплексоров. Выбор конкретных операндов, участвующих в операциях сравнения, определяется управляющими сигналами от блока 11 управления. .

В каждый i-й разряд блока 4 сравнения входят (фиг. 2) повторитель 21, триггер 22 данных, коммутаторы 23 и 24, сумматор 25 по модулю два и элемент И 26.

Повторитель 21 предназначен для развязки выводов объекта контроля от входов триггера 22 данных и коммутатора 23, что позволяет проверять объекты контроля с коэффициентом разветвления выводов, равным единице.

Триггер 22 данных предназначен для запоминания и хранения отклика объекта контроля.

Коммутатор 23 предназначен для выбора в качестве первого операнда операции сравнения отклик объекта контроля Б текущем такте либо з.на- чение, хранимое в тригг-ере 22 данных.

Коммутатор 24 предназначен для выбора в качестве второго операнда операции сравнения отклик эталона либо данные от блока 5 мультиплексоров.

5

0

0

Операция сравнения выполняется сумматором 25 по модулю два.

Элемент И 26 обеспечивает передачу результата сравнения на выход блока 4 или его блокировку в зависимости от состояния триггеров 14 коммутации и 16 дакньк блока 1 регистров.

Таким образом, в сравнении участвуют только те разряды, для которых, во-первых, триггеры 14 коммутащш ус7 ановлены в 1 (соответствующие выводы блоков 2 и 3 являются выхода- 5 ми) и, во-вторых, триггеры 16 данных также установлены в единицу (рассмат- риЕшемые разряды не маскируются).

Блок 5 мультиплексоров предназначен для выбора источника данных для блока 1 регистров и блока 4 сравнения. Управление процессом выбора источника осуществляется аз рядным кодом, поступаюощм от блока 6 сверхоперативной памяти.

Любой i-й разряд блока 5 мультиплексоров (фиг. 2) содержит дешифратор 27, элемент ИЛИ 28, элемент И-ИЛИ 29.

Дешифратор 27 предназначен для анализа кода, поступающего с блока 6 сверхоперативной памяти.

Элемент И-ИЛИ 29 в зависимости от сигналов на выходе дещифратора 27 подключает к первому выходу i-ro разряда блока 5 один из источников дан- ных: если на входе дешифратора код 00 - генератор 8 псевдослучайных тестов; если на входе дешифратора код 01 - формирователь 9 псевдослучайной последовательности; если на входе Q дешифратора код 10 или 11 - блок 10 памяти тестов.

Выход старшего разряда дешифратора 27 составляет второй выход i-ro разряда блока 5 мультиплексоров.

Таким образом, если на i-й разряд блока 5 мультиплексоров от блока 6 сверхоперативной памяти поступает код 11, на его втором выходе появляется значение 1, которое при прие5

0

ме в i-й триггер 14 коммутации через его инверсный выход переводит элементы И 19 и 20 в высокоимпендансное состояние выхода, т.е. i-й вывод объектов 2 и 3 рассматривается как выход. Одновременно по первому выходу 1-го разряда блока 5 мультиплексоров поступает информация от блока 10 памяти тестов, которая записывается в i-й триггер 16 данных блока 1 регистров.

Если же на i-й разряд блока 5 типлексоров поступают коды 00, 01 либо 10, на его втором выходе появляется значение О, которое при приеме в i-й триггер 14 коммутации через элементы И 19 и 20 разрешает прохождение сигнала с выхода 1-го триггера 16 данных на объекты 2 и 3, т.е. i-й вывод объектов 2 и 3 рассматривается как вход.

При этом сигнал с прямого выхода i-ro триггера 14 коммутации через элементы И 18 и 26 запре щает передачу результата сравнения по 1-му выводу (как уже было отмечено, этот вывод является входом проверяемого объекта) в блок 11 управления.

Если на i-й разряд блока 5 мультиплексоров поступает код 00, в i-й триггер.16 данных по первому выходу i-ro разряда блока 5 записывается информация с i-ro выхода генератора 8 псевдослучайных тестов; если на i-й разряд блока 5 мультиплексоров поступает код 01, в i-й триггер 16 данных записывается информация с i-ro выхода формирователя 9 псевдослучайной последовательности; если на i-й разряд блока 5 мультиплексоров поступает код 10, в i-й триггер 16 данных записывается информация с i-ro выхода блока 10 памяти тестов.

Таким образом, блок 5 мультиплексоров позволяет одновременно и независимо друг от друга передавать для каждого i-го разряда следующую информацию: по второй группе выходов - является i-й вывод эталонного 2 и проверяемого 3 объектов входом либо выходом; по первой группе выходов - если i-й вывод объектов 2 и 3 является выходом, передается информация о том, участвует ли данный выход в операции сравнения с эталоном (маска сравнения), если же i-й выход проверяемого объекта является входом, не

0

5

0

5

0

5

0

5

редается входное воздействие от выбранного источника.

Блок 6 сверхоперативной памяти предназначен для хранения кодов управления блоком 5 мультгшлексоров. Разрядность блока 6 сверхоперативной памяти равна 2 N, т.е. каждому разряду блока 5 мультиплексоров соответствует группа из двух разрядов блока 6 сверхоперативной памяти,

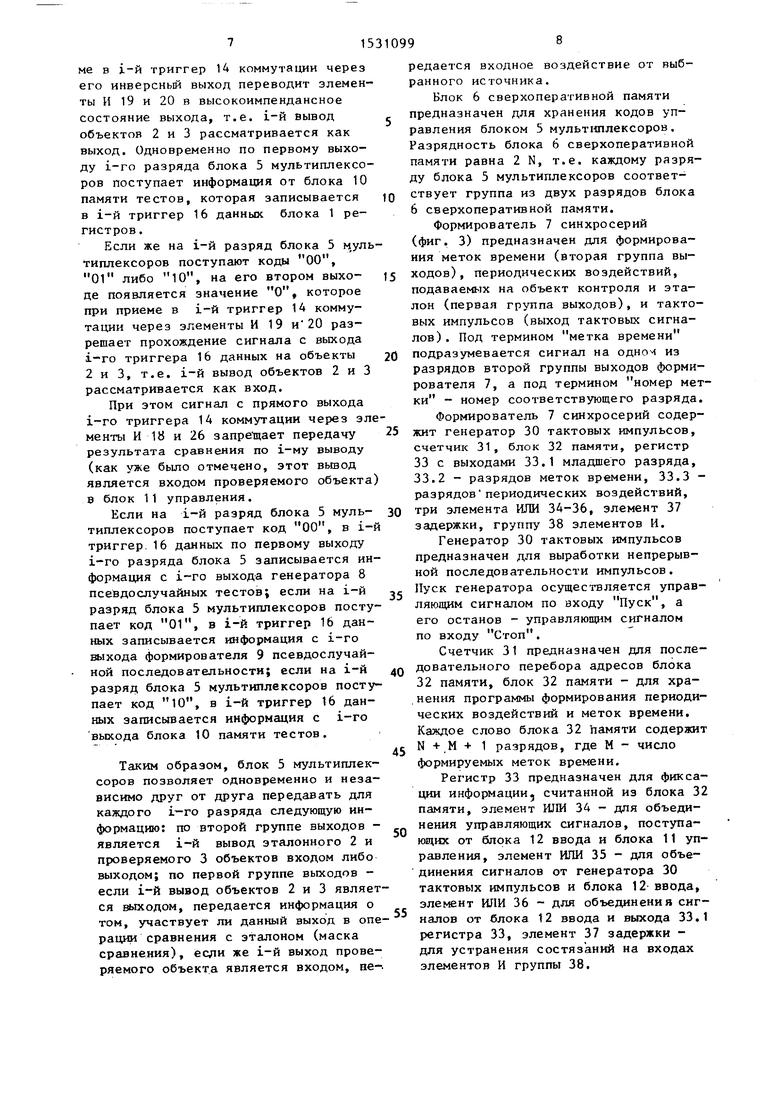

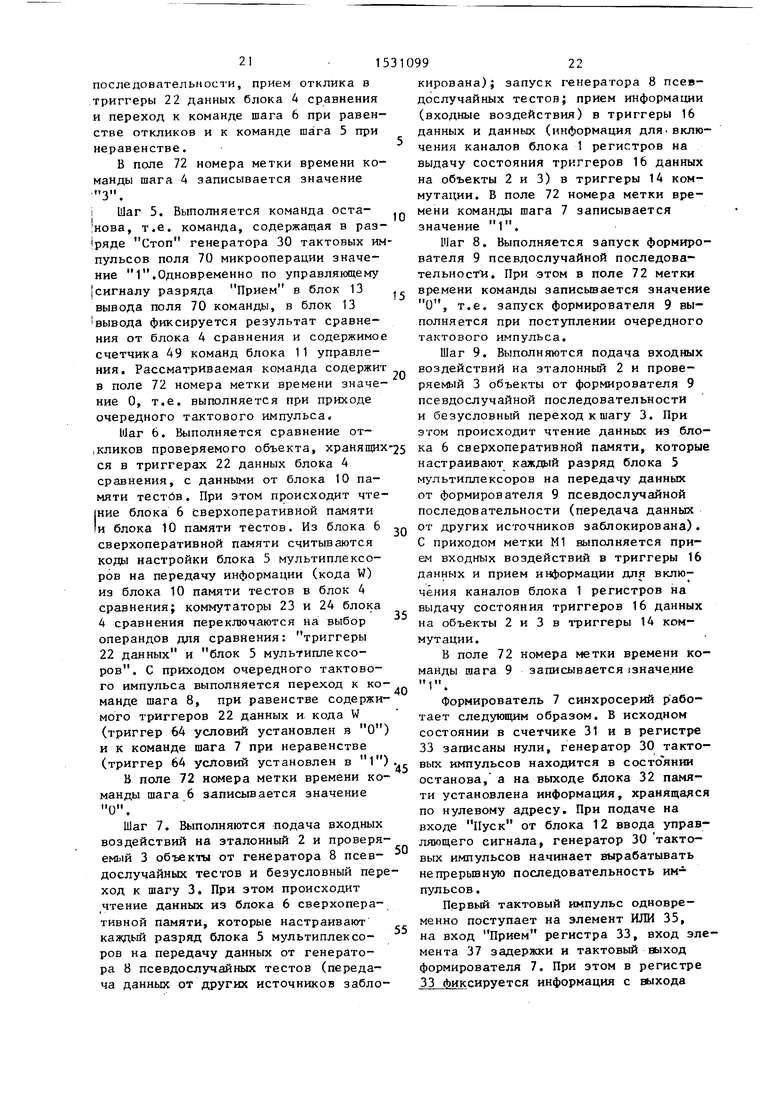

Формирователь 7 синхросерий (фиг. 3) предназначен для формирования меток времени (вторая группа выходов) , периодических воздействий, подаваемых на объект контроля и эталон (первая группа выходов), и тактовых импульсов (выход тактовых сигналов) . Под термином метка времени подразумевается сигнал на одном из разрядов второй группы выходов формирователя 7, а под термином номер метки - номер соответствующего разряда.

Формирователь 7 синхросерий содержит генератор 30 тактовых импульсов, счетчик 31, блок 32 памяти, регистр 33 с выходами 33.1 младшего разряда, 33.2 - разрядов меток времени, 33.3 - разрядов периодических воздействий, три элемента ИЛИ 34-36, элемент 37 задержки, группу 38 элементов И.

Генератор 30 тактовых импульсов предназначен для выработки непрерывной последовательности импульсов. Пуск генератора осуществляется управляющим сигналом по входу Пуск, а его останов - управляющим сигналом по входу Стоп.

Счетчик 31 предназначен дпя последовательного перебора адресов блока 32 памяти, блок 32 памяти - для хранения Программы формирования периодических воздействий и меток времени. Каждое слово блока 32 памяти содержит N М + 1 разрядов, где М - число формируемых меток времени.

Регистр 33 предназначен для фиксации информации, считанной из блока 32 памяти, элемент ИЛИ 34 - для объединения управляющих сигналов, поступающих от блока 12 ввода и блока 11 управления, элемент ИЛИ 35 - для объе- динения сигналов от генератора 30 тактовых импульсов и блока 12 ввода, элемент ИЛИ 36 - для объединения сигналов от блока 12 ввода и выхода 33,1 регистра 33, элемент 37 задержки - для устранения состязаний на входах элементов И группы 38.

91531099

Группа 38 элементов И предназначена для обеспечения одинаковой дли- тельности импульсов, являющихся метками времени.

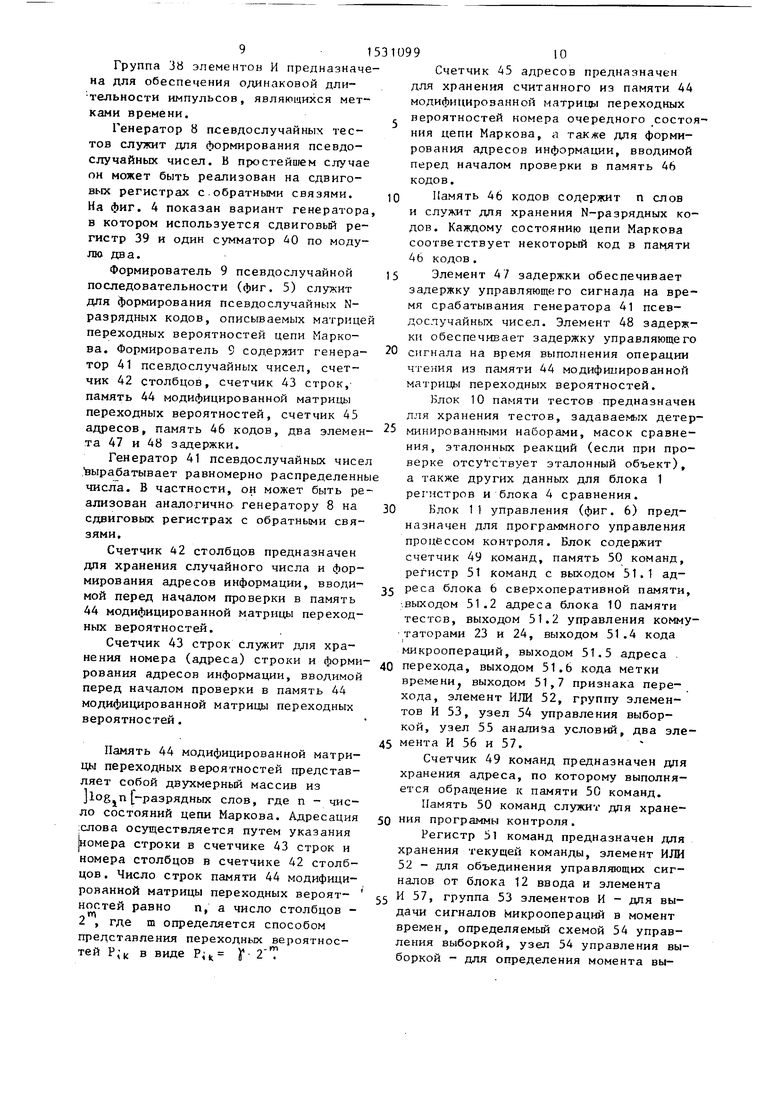

Генератор Ь псевдослучайных тестов служит дпя формирования псевдослучайных чисел. В простейшем случае он может быть реализован на сдвиговых регистрах с.обратными связями. Q На фиг. 4 показан вариант генератора, в котором используется сдвиговый регистр 39 и один сумматор 40 по модулю два.

Формирователь 9 псевдослучайной )5 последовательности (фиг. 5) служит для формирования псевдослучайных N- разрядных кодов, описываемых матрицей переходных вероятностей цепи Марко10

ва. Формирователь S содержит генера- 20 тор 41 псевдослучайных чисел, счетчик 42 столбцов, счетчик 43 строк, память 44 модифицированной матрицы переходных вероятностей, счетчик 45

Счетчик 45 адресов предназначен для хранения считанного из памяти 44 модифицированной матрицы переходных вероятностей номера очередного состояния цепи Маркова, а также дпя формирования адресов информации, вводимой перед началом проверки в память 46 кодов.

Память 46 кодов содержит п слов и служит для хранения N-разрядных кодов. Каждому состоянию цепи Маркова соответствует некоторый код в памяти 46 кодов.

Элемент 47 задержки обеспечивает задержку управляющего сигнала на время срабатывания генератора 41 псевдослучайных чисел. Элемент 48 задержки обеспечивает задержку управляющего сигнала на время выполнения операции чтения из памяти 44 модифицированной матрицы переходных вероятностей.

Блок 10 памяти тестов предназначен для хранения тестов, задаваемых детерадресов, память 46 кодов, два элемен- минированными наборами, масок сравнета 47 и 48 задержки.

Генератор 41 псевдослучайных чисел ыра батывает равномерно распределенные числа. В частности, он может быть реализован аналогична генератору 8 на сдвиговых регистрах с обратными связями.

Счетчик 42 столбцов предназначен дпя хранения случайного числа и формирования адресов информации, вводи- мой перед началом проверки в память 44 модифицированной матрицы переходных вероятностей.

Счетчик 43 строк служит для хранения номера (адреса) строки и формирования адресов информации, вводимой перед началом проверки в память 44 модифицированной матрицы переходных вероятностей.

Память 44 модифицированной матрицы переходных вероятностей представляет собой двухмерный массив из Jlog,n -разрядных слов, где п - число состояний цепи Маркова. Адресация :слова осуществляется путем указания номера строки в счетчике 43 строк и номера столбцов в счетчике 42 столбцов. Число строк памяти 44 модифицированной матрицы переходных вероят- п, а число столбцов - способом

30

35

40

ностей равно i., m

ния, эталонных реакций (если при проверке отсу гствует эталонный объект), а также других данных для блока 1 рег истров и блока 4 сравнения.

Блок 11 управления (фиг. 6) предназначен для программного управления процессом контроля. Блок содержит счетчик 49 команд, память 50 команд, регистр 51 команд с выходом 51,1 адреса блока 6 сверхоперативной памяти, .выходом 51.2 адреса блока 10 памяти тестов, выходом 51.2 управления коммутаторами 23 и 24, выходом 51.4 кода

микроопераций, выходом 51.5 адреса , перехода, выходом 51.6 кода метки времени выходом 51,7 признака перехода, элемент ИЛИ 52, группу элементов И 53, узел 54 управления выборкой, узел 55 анализа условий, два эле- 45 мента И 56 и 57.

Счетчик 49 команд предназначен дпя хранения адреса, по которому выполняется обращение к памяти 50 команд.

Память 50 команд служит для хранения программы контроля.

Регистр 51 команд предназначен для хранения текущей команды, элемент ИЛИ 52 - для объединения управляющих сигналов от блока 12 ввода и элемента И 57, группа 53 элементов И - дпя выдачи сигналов Микроопераций в момент времен, определяемьй схемой 54 управления выборкой, узел 34 управления выборкой - для определения момента вы50

55

представления переходных вероятностей Р к в виде Р; Г 27

10

Счетчик 45 адресов предназначен для хранения считанного из памяти 44 модифицированной матрицы переходных вероятностей номера очередного состоя ния цепи Маркова, а также дпя формирования адресов информации, вводимой перед началом проверки в память 46 кодов.

Память 46 кодов содержит п слов и служит для хранения N-разрядных кодов. Каждому состоянию цепи Маркова соответствует некоторый код в памяти 46 кодов.

Элемент 47 задержки обеспечивает задержку управляющего сигнала на время срабатывания генератора 41 псевдослучайных чисел. Элемент 48 задержки обеспечивает задержку управляющего сигнала на время выполнения операции чтения из памяти 44 модифицированной матрицы переходных вероятностей.

Блок 10 памяти тестов предназначен для хранения тестов, задаваемых детер минированными наборами, масок сравне0

5

0

ния, эталонных реакций (если при проверке отсу гствует эталонный объект), а также других данных для блока 1 рег истров и блока 4 сравнения.

Блок 11 управления (фиг. 6) предназначен для программного управления процессом контроля. Блок содержит счетчик 49 команд, память 50 команд, регистр 51 команд с выходом 51,1 адреса блока 6 сверхоперативной памяти, .выходом 51.2 адреса блока 10 памяти тестов, выходом 51.2 управления коммутаторами 23 и 24, выходом 51.4 кода

микроопераций, выходом 51.5 адреса , перехода, выходом 51.6 кода метки времени выходом 51,7 признака перехода, элемент ИЛИ 52, группу элементов И 53, узел 54 управления выборкой, узел 55 анализа условий, два эле- 5 мента И 56 и 57.

Счетчик 49 команд предназначен дпя хранения адреса, по которому выполняется обращение к памяти 50 команд.

Память 50 команд служит для хранения программы контроля.

Регистр 51 команд предназначен для хранения текущей команды, элемент ИЛИ 52 - для объединения управляющих сигналов от блока 12 ввода и элемента И 57, группа 53 элементов И - дпя выдачи сигналов Микроопераций в момент времен, определяемьй схемой 54 управления выборкой, узел 34 управления выборкой - для определения момента вы0

5

дачи сигналов микроопераций и запуска операции выборки очередной команды Узел 54 управления выборкой состоит (фиг. Ь) из дешифратора 58, группы 59 элементов И, элемента ИЛИ 60.

Сигнал на выходе узла 54 управления выборкой появляется в момент вре- мени, указанном меткой времени, номер которой задается кодом на выходе 51.6 регистра 51 команд.

Узел 55 анализа условий предназначен для определения способа формиро вания адреса следующей команды в соответствии со значением выхода 51.7 признака перехода регистра 51 команд и результата сравнения в блоке 4 сравнения. Узел 55 анализа условий (фиг. 6) содержит два элемента ИЛИ 61 и 62, элемент НЕ 63, триггер 64 условий, два элемента И 65 и 66.

Триггер 64 условий служит для хранения результата операции сравнения, выполняемой в блоке 4, путем объединения с помощью элемента ИЛИ 61 результатов сравнения по каждому из разрядов .

Элемент НЕ 63, элементы И 65 и 66, элемент ИЛИ 62 выполняют анализ признака перехода с выхода 51.7 регистра 51 команд (О - условный, 1 - безусловный), а также значение условия из триггера 64 условий и вырабатывает управляющие сигналы для формирования адреса следующей команды (переход по адресу с выхода 51.5 регистра 51 команд либо по адресу из счетчика 49 команд, увеличенного на единицу).

Элементы И 56 и 57 предназначены для блокировки процесса выборки до прихода сигнала запуска выборки от узла 54 управления выборкой.

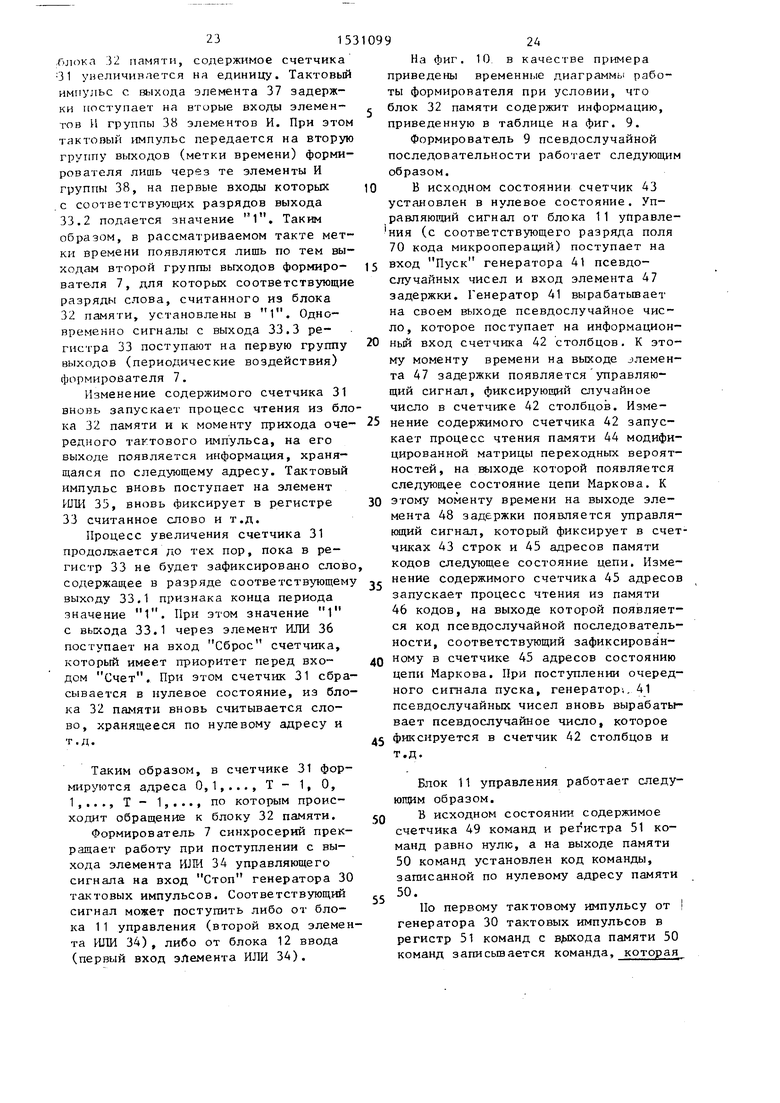

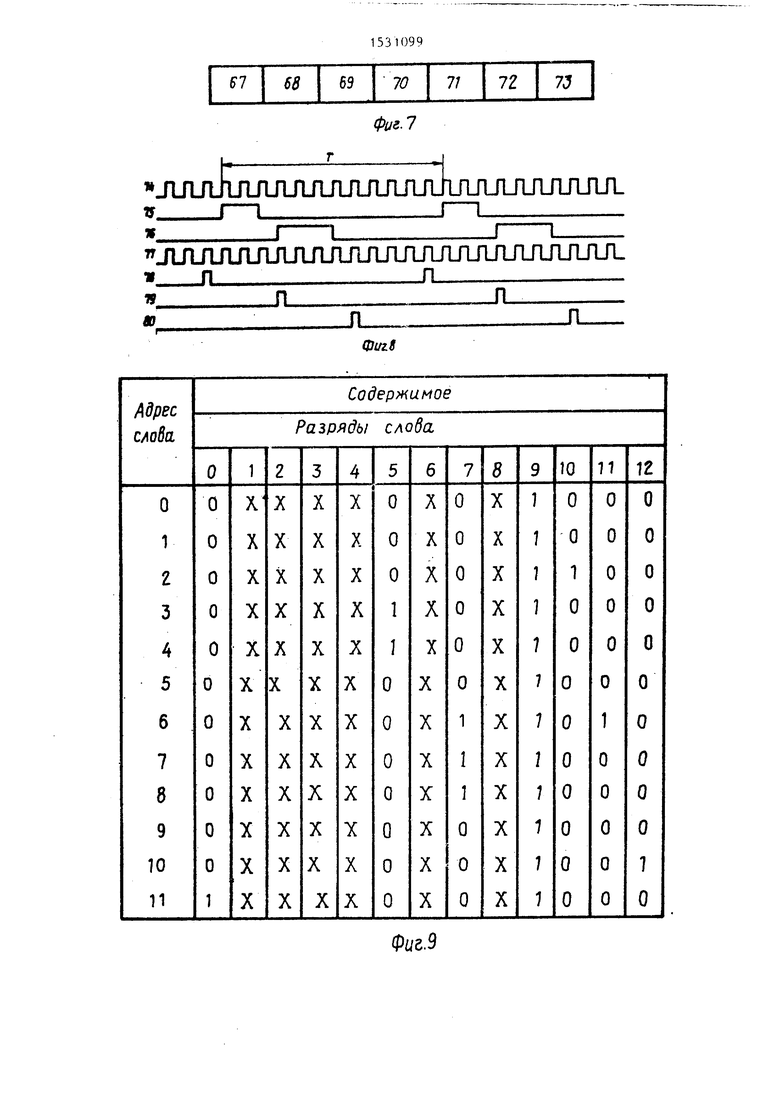

На фиг. 7 использованы следующие обозначения: 67 - поле адреса блока 6 сверхоперативной памяти, куда запи- сьшается адрес, по которому при выполнении команды осуществляется операция чтения из блока 8 сверхоперативной памяти; 68 - поле адреса блока 10 памяти тестов, куда записывается адрес, по которому при выполнении команда осуществляется чтение из блока 10 памяти тестов; 69 - поле управления коммутаторами 23 и 24, куда заносятся значения управляющих сигналов, настраивающих коммутатор 23 на передачу информации с триггера 22 данных либо передачу откликов с проверяемого объекта, коммутатор 24 на передачу

912

отклика от эталонного объекта либо передачу информации от блока 5 мультиплексоров; 70 - попе кода микроопераций, куда заносятся значения следующих управляющих разрядов: Прием в триггер 14 коммутации, Прием в триггер 15 синхронизации, Прием в триггер 16 данных, Прием в триггер

22 данньк, Стоп на генератор 30 тактовых импульсов, Пуск формирователя 9 псевдослучайной последовательности, Прием в блок 13 вывода; 71 - поле адреса перехода, куда записьтается адрес, по которому передается управление при безусловном переходе, либо при условном переходе, если результат операции сравнения в блоке 4 сравнения равен нулю; 72 - поле кода метки времени, куда заносится номер метки времени (микроопераи:;И из поля 70 выдаются на управляемые блоки в момент прихода метки с указанным номером, одновременно при этом

запускается процесс выборки очередной команды); 73 - поле признака перехода, куда заносится ноль при необхо- димости выполнения условного перехода и единица при безусловном перехоДе.

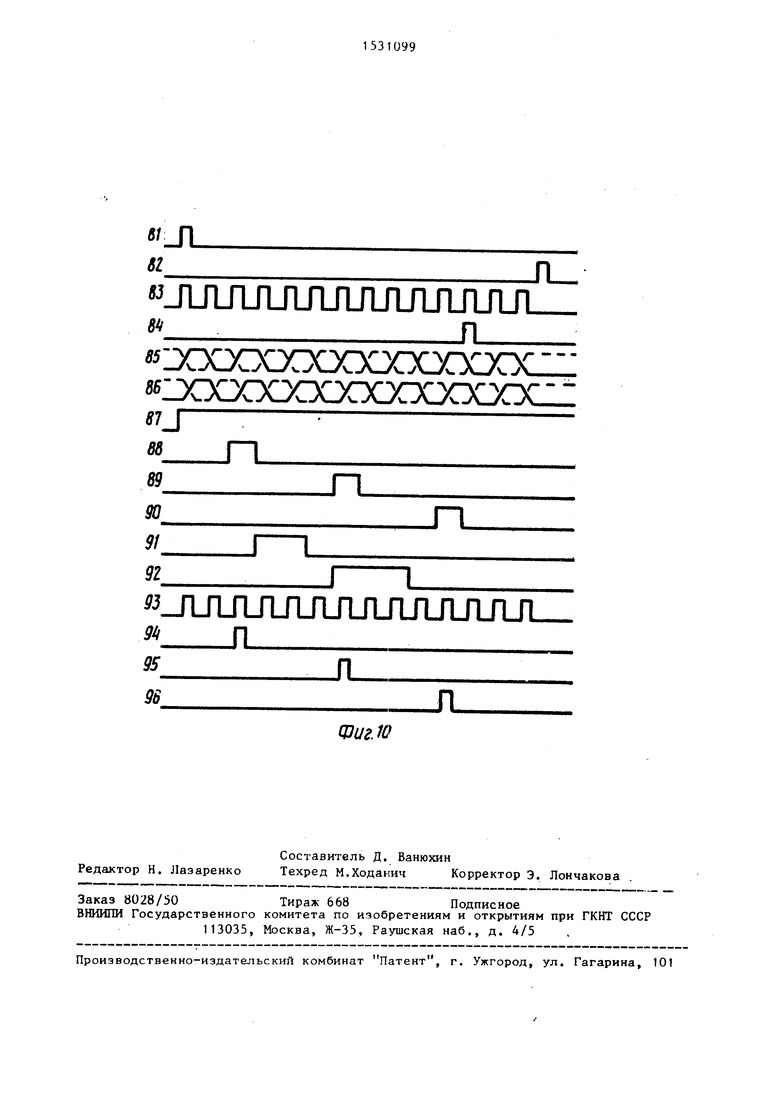

На фиг. И обозначены временная диаграмма 74 тактовых импульсов, временная диаграмма 75 первой серии синхронизации (серия Ф1), временная диаграмма 76 второй серии синхронизации (серия Ф2), временная диаграмма 77 сигнала, определяющая момент выполне-. ния команд, не связанных с обменом (метка МО); временная диаграмма 78

сигнала, определяющего моменты подачи входных воздействий на объекты

2и 3 (метка Ml); временная диаграмма 79 сигнала, определяющего моменты коммутации двунаправленных выводов

объектов 2 и 3 (метка М2); временная диаграмма 80 сигнала, определяющего моменты приема откликов объектов 2 и

3(метка МЗ).

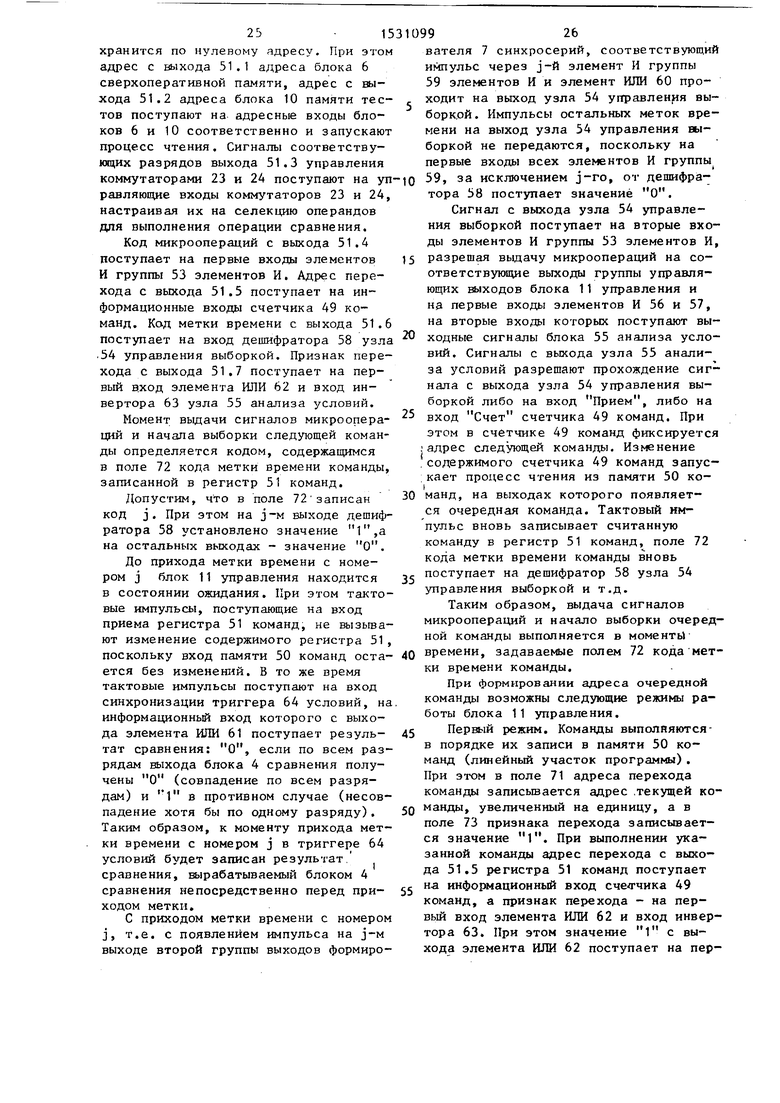

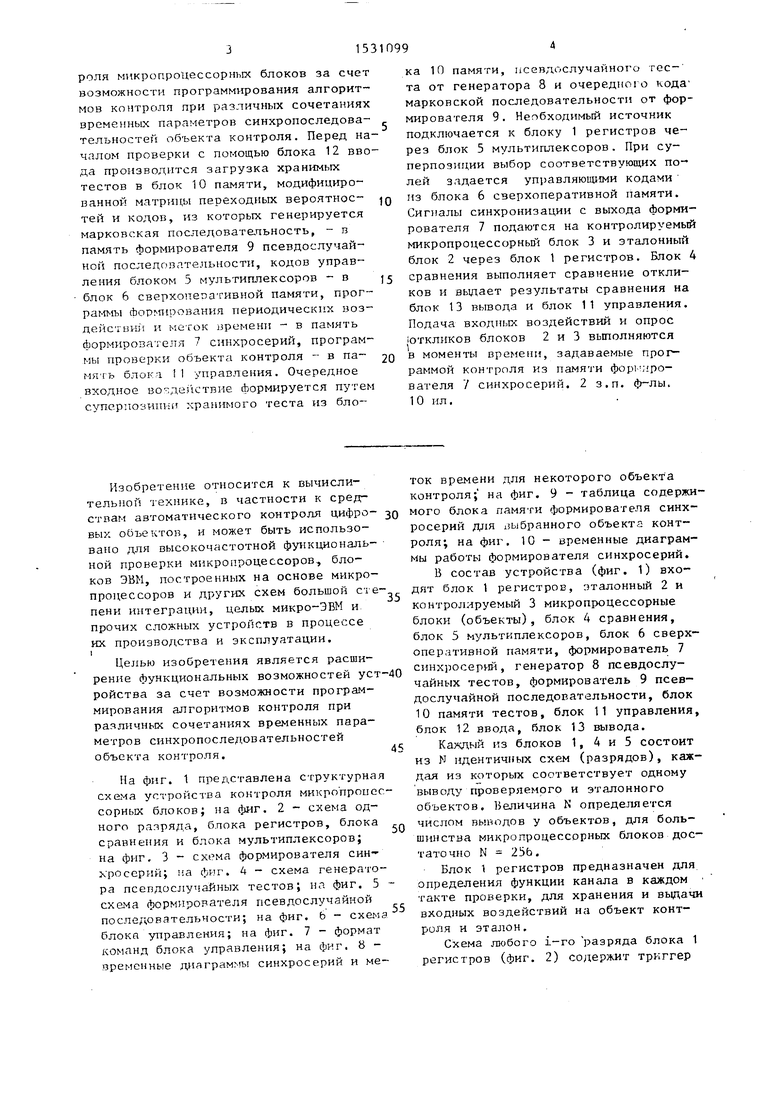

На фиг, 10 обозначены сигнал 81 на входе Пуск генератора 30 тактовых импульсов, сигнал 82 на входе Стоп генератора 30 тактовых импуль- .сов, сигнал 83 на выходе генератора 30 тактовых импульсов, сигнал 84 на выходе элемента ИЛИ 36, сигнал 85 на выходе счетчика 31, сигнал 86 на выходе блока 32 памяти; сигналы 87-90 на нулевом, первом, втором и третьем разрядах соответственно выхода 33.2

регистра 33 сигналы 9 и 92 на пятом и на седьмом выходах соответственно первой группы выходов формирователя 7; сигналы 93-96 на нулевом (метка N0), на первом (метка Ml), на втором (метка М2), на третьем (метка МЗ) выходах соответственно второй группы выходов формирователя 7.

Устройство работает следуюгцим образом .

В исходном состоянии генератор 30 тактовых импульсов находится в состоянии останова.

Перед началом проверки на соответ- единица, если k Т - 1; в каждом из

разрядов i,, i,..,,ig записывается

ствующих управляющих выходах блока 12 ввода формируются управляющие сигналы, устанавливающие в нулевое состояние регистр 51 команд блока 11

значение соответствующего синхросигнала на k-M такте; в разряде N+j+1, j 0,..,, М-1, записывается единица,

управления и регистр 33 формирователя Q если на k-м такте дохгана выдаваться

7синхросерий, в единичное состояние триггеры 14 коммутации блока 1 регистров. Тем самым, на управляющих выходах блока 11 управления устанавливаются нулевые значения, выходы элемен- 25 тоБ И 19 и 20 переводятся в высоко- импендансное состояние, а-на выходе 33.1 регистра 33 установлено значение О. Далее с помощью блока 12 : ввода выполняется загрузка блока 6 сверхоперативной памяти, блока 32 памяти формирователя 7 синхросерий, сдвигового регистра 39 генератора

8псевдослучайных тестов, памяти

44 модифицированной матрицы переходных вероятностей и памяти 46 кодов формирователя 9 псевдослучайной последовательности, блока 10 памяти тесметка с номером J и ноль в противном случае.

Значение остальных разрядов k-ro снова произвольное.

Пример. Пусть проверяемый объект 2 имеет N 8 выводов, причем на выводы 5 и 7 синхроимпульсы серий Ф1 и Ф2.

30

35

Подача входных воздействий выполняется до п€фехода сигнала Ф1 из О в 1, а прием отклика - после перехода сигнала Ф2 из 1 в О.

Пусть команды, не связанные с обменом, выполняются с частотой поступ ления тактовых импульсов. Для этого воспользуемся меткой с номером О. Для организации обмена воспользуемся меткой с номером 1 - моменты подачи входных воздействий, меткой с номером 2 - моменты коммутации двуна равленных выводов, и меткой с номером 3 - моменты приема откликов.

тов, памяти 50 команд блока 11 управления.

При загрузке блока 6 сверхоперач тивной памяти и блока 10 памяти тестов, адреса ячеек памяти и управляющие сигнал записи формируются на соответствующих управляющих выходах блока 12 ввода, а данные - на соответствующих информационных выходах блока 12 ввода.

При загрузке блока 32 памяти формирователя 7 синхросерий адреса ячеек памяти задаются счетчиком 31, данные, записываемые в память, формируются на соответствующих информационных выходах блока 12 ввода, а сигналы управления счетчиком 31 и записью в блоке 32 памяти формируются на соответствующих управляющих выходах блока 12 ввода. При этом в блок 32 памяти загружается следующая информа

ция, Пусть заданы временные дм;;грам- мы синхросерий, которые подаются на выводы i , i,...,ip объекта 3 контроля и временные диаграммы меток времени. Интервалы времени измеряют в относительных единицах, равных периоду импульсов генератора 30 тактовых импульсов. Через Т обозначим период синхроимпульсов и меток времени.

В k-e слово, k 0,1,,.,, Т - 1, блока 32 памяти записывается следующая информация: в нулевом разряде записывается ноль, если k «i. Т - 1, и

значение соответствующего синхросигнала на k-M такте; в разряде N+j+1, j 0,..,, М-1, записывается единица,

если на k-м такте дохгана выдаваться

метка с номером J и ноль в противном случае.

Значение остальных разрядов k-ro снова произвольное.

Пример. Пусть проверяемый объект 2 имеет N 8 выводов, причем на выводы 5 и 7 синхроимпульсы серий Ф1 и Ф2.

Подача входных воздействий выполняется до п€фехода сигнала Ф1 из О в 1, а прием отклика - после перехода сигнала Ф2 из 1 в О.

Пусть команды, не связанные с обменом, выполняются с частотой поступления тактовых импульсов. Для этого воспользуемся меткой с номером О. Для организации обмена воспользуемся меткой с номером 1 - моменты подачи входных воздействий, меткой с номером 2 - моменты коммутации двунаправленных выводов, и меткой с номером 3 - моменты приема откликов.

Временные диаграммы синхросерий и меток для рассмотренного примера приведены на фиг. 8, где Т 12.

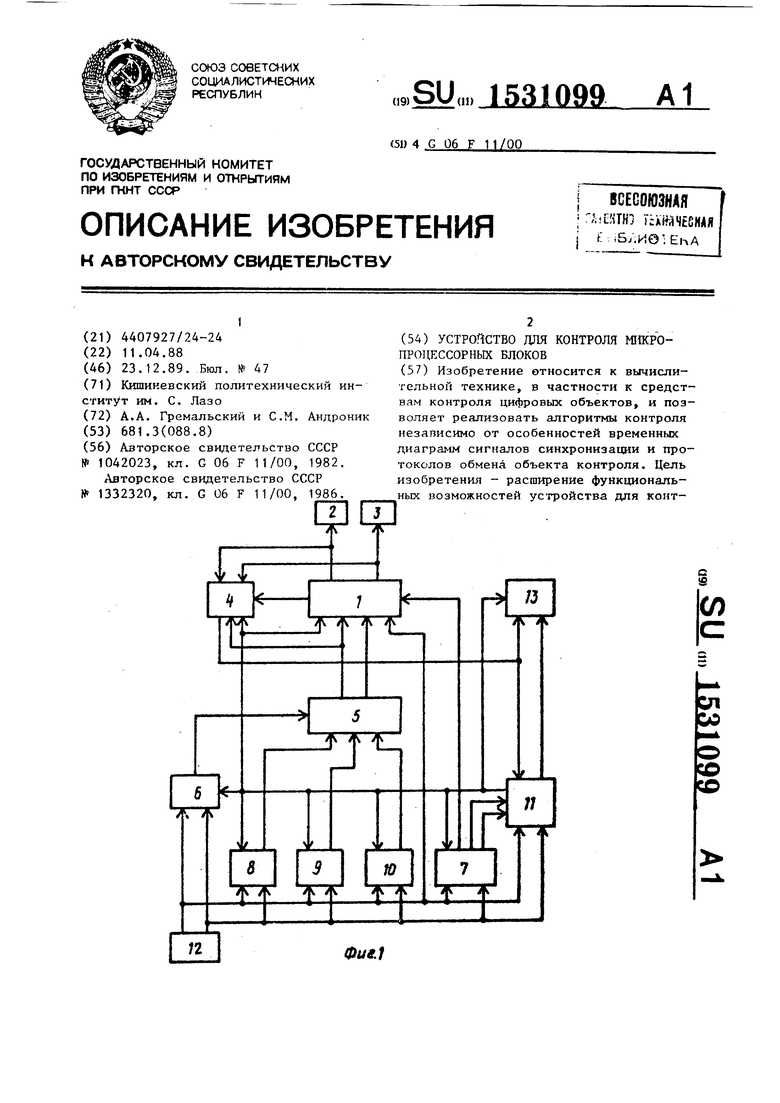

Содержимое блока 32 памяти для рассматриваемого примера приведено в таблице на фиг. 9, где символом X обозначено безразличное состояние.

При загрузке генератора 8 псевдослучайных тестов данные для записи в сдвиговом регистре 39 формируются на соответствующих информационных выходах, а сигналы приема в регистр 39 - на соответствующих управляющих выходах блока 12 ввода.

При загрузке памяти 44 модифици- .рованной матрицы переходных вероят

ностей адреса ячеек памяти задаются счетчиками 42 столбцов и 43 строк, данные, записьюаемые в память, формируются на соответствующих информаци- онных выходах, а сигналы управления счетчиком 42 столбцов, счетчиком 43 строк и записью в память 44 - на соответствующих управляющих выходах блока 12 ввода. При этом в память 44 загружается модифицированная матрица переходных вероятностей А, пол чаемая следующим образом.

Пусть задана простая однородная цепь Маркова S з , i 0,п-1 с матрицей переходных вероятностей Р / Д i вероятность перехода за один такт из состояния s , в состояние i, k О, n-f, P;i If .k y;k целое. Модифици- рованная матрица переходных вероятностей А имеет вид А (|a;j || , ,п-1, ,. Строка А;, соответствующая состоянию SJ, представляет собой числовую последовательность, состоящую из п серий, причем k-я серия состоит из номеров k, повторенных у;| раз

Например, при Р

(1 1 4 8

m 3; А., (О, О, 1, 1, 1, 1, 1, 2).

При загрузке памяти 46 кодов адреса ячеек памяти задаются счетчиком 45 адресов, данные, записываемые в память, формируются на соответствующих информационных выходах, а сигналы управления счетчиком 45 адресов и записью в память 46 кодов - на соответствующих управляющих выходах блока 12 ввода.

При загрузке памяти 50 команд блока 11 управления адреса ячеек памяти задаются счетчиком 49 команд, дан- ные для записи в памяти 50 формируются на соответствующих информационных выходах, а сигналы управления счетчиком 49 команд и записью в памяти 50 - на соответствующих управляющих выходах блока 12 ввода.

После завершения процесса загрузки блок 12 ввода с помощью соответствующих сигналов на управляющих выхог дах устанавливает э нулевое состояние счетчик 31, счетчик 43 строк и счетчик 49 команд. Далее начинается сам процесс высокочастотной проверки.

Без ограничения общности примем дпя определенности, что прием информа ции в триггеры коммутации 14, синхро

низации 15 и данных 16 блока 1 регистров осуществляется по заднему фронту управляющего сигнала на соответству-| ющем синхровходе; прием информации в триггер 22 данных блока 4 сравнения, в триггер 64 условий блока 11 управления - по переднему фронту управляющего сигнала на синхровходе; прием информации в регистре 33 формирователя 7 синхросерий, в регистр 51 команд блока 11 управления, в счетчи- кя столбцов 42, строк 43 и адреса 45 формирователя 9 псевдослучайной последовательности, в счетчик 49 команд, а также увеличение их содержимого и пуск генераторов 8 и 41 выполняются по переднему фронту соответствующего управляющего сигнала; очередное псевдослучайное число на выходах генераторов 8 и 41 появляется за время, не превышающее длительности тактового сигнала.

Подразумевается также, что блок 6 сверхоперативной памяти, блок 9 памяти тестов, блок 32 памяти формирователя 7 синхросерий и памяти 44 модифицированной матрицы переходных вероятностей, памяти 46 кодов, памяти 50 команд имеют одинаковое время выбор - ки, не превосходящей длительности тактового импул.ьса.

Сигнал пуска, сформированный на соответствующем управляющем выходе i блока 12 ввода запускает формирователь 7 синхросерий. При этом генератор 30 тактовых импульсов начинает вырабатывать непрерывную последовательность импульсов. По первому тактовому импульсу в регистр 51 команд с выхода памяти 50 команд заносится первая команда програм контроля, которая хранится по нулевому адресу. При синхронной организации обмена с проверяемым объектом работа устройства в каждом такте t высокочастот- |ной проверки сводится к следующей последовательности шагов, задаваемых командами программы, хранимой в памяти 50 команд блока 11 управления. Для определенности далее считается, что последовательность синхронизации объекта состоит из двух серий Ф1 и Ф2, причем подача входных воздействий осуществляется в моменты времени, задаваемые меткой Ml, входы объекта - контроля и эталона должны оставаться без изменений до момента времени, за

даваемого меткой М2, а сня 1-ие откликов объектов должно выполняться в моменты времени, задаваемые меткой МЗ.

Рассмотрим сперва работу устройства при реализации алгоритма контроля при котором входные воздействия подаются на эталонный и проверяемый объеты 2 и 3 без подробного анализа откликов проверяемого объекта и выполняется лишь сравнение откликов объектов 2 и 3.

Шаг 1. Выполняются логическое подключение второй группы выходов (выходов периодических воздействий) форми- рователя 7 синхросерий к соответствующим входам эталонного 2 и проверяемого 3 объектов (синхровходов) и запуск формирователя 9 псевдослучайной последовательности для получения соответствующих входных воздействий первого такта высокочастотной проверки. При этом происходит чтение данных из блока б сверхоперативной памяти, которые настраивают блок 5 мультиплексоров на передачу информации из блока 10 памяти тестов в блок 1 регистров; чтение слова из блока 10 памяти тестов и его запись в триггеры 15 синхронизации блока 1 регист- ров, а также запуск формирователя 9 псевдослучайной последовательности. Рассматриваемая команда содержит в поле 72 номера метки времени значение О, т.е. сигналы приема в триггеры 15 и запуска формирователя 9 выдаются при поступлении метки времени с номером О, т.е. фактически по очередному тактовому импульсу. Шаг 1 выполняется только один раз в начале программы высокочастотной проверки.

Шаг 2. Выполняется подача входных воздействий на эталонный 2 и проверяемый 3 объекты. При этом происходит: чтение данных из блока 6 сверхопер.а- тивной памяти, которые настраивают каждый разряд блока 5 мультиплексоров на требуемый источник данных; запуск генератора 8 псевдослучайных тестов; чтение блока 10 памяти тестов; прием данных (входных воздействий) , поступающих от генератора 8 псевдослучайных тестов, от формирователя 9 псевдослучайной последовательности, от блока 10 памяти тестов в триггеры 16 данных; прием данных с второй группы выходов блока 5 (информация для включения каналов блока 1 регистров, связанных с двунаправлен

ными выводами объектов, на выдачу состояния триггеров 16 данных на объекты) в триггеры 14 коммутации.

Рассматриваемая команда содержит в поле 72 номера метки времени значение

1

т.е. сигналы микроопераций

10

0

5

Q

5

0

0

5

(прием в триггеры данных 16 и коммутации 14, запуск генератора 8) выдаются при поступлении метки М1.

Шаг 3. Выполняются переключение соответствующих выводов эталонного 2 и проверяемого 3 объектов на выдачу информации, а также подготовка маски сравнения. При этом происходит чтение блока 6 Сверхоперативной памяти, чтение блока 10 памяти тестов; прием данных с второй группы выходов блока 5 мультиплексоров для включения каналов блока 1 регистров на прием реак- 1Ц{й объектов в триггеры 14 коммутации; прием маски сравнения от блока 10 памяти тестов (по выходам, которые участвуют в сравнении, принимается 1, а по остальным разрядам О) в триггеры 16 данных. В поле 72 номера метки времени рассматриваемой команды записывается значение 2, т.е. сигналь; микроопераций (прием в триггеры 14 и 16) выдаются при поступлении метки М2.

Шаг 4. Выполняются опрос выходов эталонного 2 и проверяемого 3 объектов, сравнение незамаскированных выходов объектов 2 и 3, а также запуск формирователя 9 псевдослучайной последовательности для получения соответствующих входных воздействий для следующего такта t (с 2 ,3,. ..) ;про- верки (шаг 2). При этом коммутаторы 23 и 24 блока 4 сравнения с помощью управляющих сигналов с выхода 51.3 регистра 51 команд переключаются на выбор операндов для сравнения: про- д5 веряемьй объект и эталонный объект. К моменту прихода метки МЗ на выходах объектов 2 и 3 уже установились соответствующие отклики, а на выходе блока 4 сравнения - результат сравнения. С приходом метки МЗ выполняется запуск формирователя 9 и переход: при равенстве откликов (триггер 64 условий установлен в О) - к команде шага 2; при неравенстве (триггер 64 условий установлен в 1) - к команде шага 5., В поле 72 номера метки времени команды шага 4 записывается значение

гг-з г

Шаг 5. Выполняется команда останова, t.e. команда, содержащая в разряде Стоп генератора 30 тактовых импульсов поля 70 микроопераций значение 1. Одновременно по управляющему сигналу разряда Прием в блок 13 вывода поля 70 команды, в блок 13 вывода фиксируется результат сравнения от блока 4 сравнения и содержимое .счетчика 49 команд блока 11 управления. Рассматриваемая команда содержит в поле 72 номера метки времени значение О, т.е. рассматриваемые управляющие сигналы с поЛя 70 выдаются при поступлении метки МО, т.е. по очередному тактовому импульсу.

Рассмотрим теперь работу устройства при реализации более сложного алгоритма контроля, а именно выбор источников входных воздействий выполняется в зависимости от отклика проверяемого объекта. Примем для определенности, что, если отклик проверяемого объекта совпадает с кодом W, входное воздействие на проверяемый объект подается с выхода формирователя 9 псевдослучайной последовательности, а в противном случае - с выхода генератора 8 псевдослучайных тестов.

Шаг 1. Выполняются логическое подключение второй группы выходов формирователя 7 синхррсерий к соответствующим входам эталонного 2 и проверяемого 3 объектов и запуск формирователя 9 псевдослучайной последовательности для получения соответствующих , входных воздействий первого вы- сокочасто тной проверки. При этом происходит чтение данных из блока 6 - . сверхоперативной памяти, которые настраивают блок 5 мультиплексоров на передачу информации из блока 10 памяти тестов в блок 1 регистров;чтение слова из блока to памяти тестов и его запись в триггеры 15 синхронизации блока 1 регистров. Рассматриваемая команда содержит в поле 72 номера метки времени значение О. Этот шаг выполняется только один раз в начале программы высокочастотной проверки.

Шаг 2. Выполняется подача входных воздействий на этапонньй 2 и проверяемый 3 объекты. При этом происходит: чтение данных из блока 6 сверхоперативной .памяти, которые настраивают калдтый разряд блока 5 мультиплексоров на требуемый источник данных; запуск

5

0

5

О

генератора 8 псевдослучайных гестов; чтение блока 10 памяти тестов. С приходом метки Ml выполняется: прием данных (входных воздействий), посту- паиощих от генератора В псевдослучайных тестов, от формирователя 9 псевдослучайной последовательности, от блока 10 памяти тестов в триггеры 1 данных; прием данных со второй группы выходов блока 5 (информация для включения каналов блока 1 регистров на выдачу состояния триггеров 16 данных на объекты) в триггеры 14 комму- тащии. В поле 72 номера метки времени данной команды записывается значение 1, т.е. сигналы микроопераций (прием в триггер данных 16 и коммутации 14, запуск генератора 8) выдаются в момент прихода метки 1.

Шаг 3. Выполняются переключение двунаправленных выводов эталонного 2 и проверяемого 3 объектов на выдачу информации, а также подготовка маски сравнения. При этом происходит чтение блока 6 сверхоперативной памяти и блока 10 памяти тестов. Из блока 6 сверхоперативной памяти считьшаются коды настройки блока 5 мультиплексоров, а из блока 10 памяти тестов - данные для маски сравнения. При приходе метки М2 в триггеры 14 коммутации записываются данные для включения каналов блока 1 регистров на прием реакций объектов, а в триггеры 16 данных записывается маска сравнения. В поле 72 номера метки времени рассматриваемой команды записывается значение 2.

Шаг 4. Выполняются опрос выход ов эталонного 2 и проверяемого 3 объектов, сравнение незамаскированных выходов объектов 2 и 3, а также запуск формирователя 9 псевдослучайной пос- 5 ледовательности для получения соот- |ветствующих входных воздействий для следующего такта t (,3,...) проверки (шаг 2). При этом коммутаторы 23 и 24 блока 4 сравнения с помощью управляющих сигналов с выхода 51.3 регистра 51 команд переключаются на выбор операндов для Сравнения: про- .веряемый объект и эталонный объект. К моменту прихода метки МЗ на выходе объектов 2 и 3 уже установились соответствующие отклики, а на выходе блока 4 сравнения - результат сравнения. С приходом метки МЗ выполняются запуск формирователя 9 псевдослучайной

0

5

0

5

21

последовательности, прием отклика в триггеры 22 данных блока 4 сравнения и переход к команде шага 6 при равенстве откликов и к команде шага 5 при неравенстве.

В поле 72 номера метки времени команды шага 4 записывается значение

illQll J

1 Шаг 5. Выполняется команда оста- нова, т.е. команда, содержащая в раз- ряде Стоп генератора 30 тактовых импульсов поля 70 микрооперации значение 1.Одновременно по управляющему I сигналу разряда Прием в блок 13 вывода поля 70 команды, в блок 13 вывода фиксируется результат сравнения от блока 4 сравнения и содержимое счетчика 49 команд блока 11 управления. Рассматриваемая команда содержит в поле 72 номера метки времени значение О, т.е. выполняется при приходе очередного тактового импульса.

War 6. Выполняется сравнение от- ,кликов проверяемого объекта, хранящих ся в триггерах 22 данных блока 4 сравнения, с данными от блока 10 памяти тестбв. При этом происходит чтение блока 6 Ьверхоперативной памяти и блока 10 памяти тестов. Из блока 6 сверхоперативной памяти считываются коды настройки блока 5 мультиплексоров на передачу информации (кода W) из блока 10 памяти тестов в блок 4 сравнения; коммутаторы 23 и 24 блока 4 сравнения переключаются на выбор операндов для сравнения: триггеры 22 данных и блок 5 мультиплексоров. С приходом очередного тактового импульса выполняется переход к команде шага 8, при равенстве содержимого триггеров 22 данных и кода W (триггер 64 условий установлен в О) и к команде шага 7 при неравенстве

(триггер 64 УСЛОВИЙ установлен в l)В поле 72 номера метки времени команды шага 6 записывается значение О.

Шаг 7. Выполняются подача входных воздействий на эталонный 2 и проверяемый 3 объекты от генератора 8 псев- дослучайных тестов и безусловный переход к шагу 3. При этом происходит чтение данных из блока 6 сверхоперативной памяти, которые настраивают каждый разряд блока 5 мультиплексоров на передачу данных от генератора 8 псевдослучайных тестов (передача данных от других источников забло1

10

15

20

25

-,3109922

кирована); запуск генератора 8 псевдослучайных тестов; прием информации (входные воздействия) в триггеры 16 данных и данных (информация для.включения каналов блока 1 регистров на выдачу состояния триггеров 16 данных на объекты 2 и 3) в триггеры 14 коммутации. В поле 72 номера метки времени команды шага 7 записывается значение 1.

Шаг 8. Выполняется запуск формирователя 9 псевдослучайной последовательное . При этом в поле 72 метки времени команды записьюается значение О, т.е. запуск формирователя 9 выполняется при поступлении очередного тактового импульса.

Шаг 9. Выполняются подача входных воздействий на эталонный 2 и проверяемый 3 объекты от формирователя 9 псевдослучайной последовательности и безусловный переход к шагу 3. При этом происходит чтение данных из блока 6 сверхоперативной памяти, которые настраивают каждый разряд блока 5 мультиплексоров на передачу данных от формирователя 9 псевдослучайной последовательности (передача данных от других источников заблокирована). С приходом метки Ml выполняется прием входных воздействий в триггеры 16 данных и прием информации для включения каналов блока 1 регистров на выдачу состояния триггеров 16 данных на объекты 2 и 3 в триггеры 14 коммутации.

В поле 72 номера метки времени команды шага 9 записывается (значение It II I .

Формирователь 7 синхросерий работает следующим образом. В исходном состоянии в счетчике 31 и в регистре 33 записаны нули, генератор 30 тактовых импульсов находится в состо янии

30

35

40

останова, а на выходе блока 32 памяти установлена информация, хранящадся по нулевому адресу. При подаче на входе Пуск от блока 12 ввода управляющего сигнала, генератор 30 тактовых импульсов начинает вырабатывать непрерьшную последовательность импульсов .

Первый тактовый импульс одновременно поступает на элемент ИЛИ 35, на вход Прием регистра 33, вход элемента 37 задержки и тактовый выход формирователя 7. При этом в регистре 33 фиксируется информация с выхода

2315

,блока 32 памяти, содержимое счетчика 31 увеличивается на единицу. Тактовый импульс с выхода элемента 37 задержки поступает на вторые входы элементов И группы 38 элементов И, При этом тактовый импульс передается на вторую группу выходов (метки времени) формирователя лишь через те элементы И группы 38, на первые входы которых с соответствующих разрядов выхода 33.2 подается значение 1. Таким образом, в рассматриваемом такте метки времени появляются лишь по тем выходам второй группы выходов формирователя 7, для которых соответствующие разряды слова, считанного из блока

32памяти, установлены в 1. Одновременно сигналы с выхода 33.3 регистра 33 поступают на первую группу выходов (периодические воздействия) формирователя 7.

Изменение содержимого счетчика 31 вновь запускает процесс чтения из блока 32 памяти и к моменту прихода очередного тактового импульса, на его выходе появляется информация, хранящаяся по следующему адресу. Тактовый импульс вновь поступает на элемент ШЩ 35, вновь фиксирует в регистре

33считанное слово и т.д. Процесс увеличения счетчика 31

продолжается до тех пор, пока в регистр 33 не будет зафиксировано слово содержащее в разряде соответствующему выходу 33.1 признака конца периода значение 1. При этом значение 1 с выхода 33.1 через элемент ИЛИ 36 поступает на вход Сброс счетчика, который имеет приоритет перед входом Счет. При этом счетчик 31 сбрасывается в нулевое состояние, из блока 32 памяти вновь считывается слово, хранящееся по нулевому адресу и т.д.

Таким образом, в счетчике 31 формируются адреса 0,1,..., Т - 1, О, 1 , .. ., Т - 1по которым происходит обращение к блоку 32 памяти.

Формирователь 7 синхросерий прекращает работу при поступлении с выхода элемента ИЛИ 34 управляющего сигнала на вход Стоп генератора 30 тактовых импульсов. Соответствующий сигнал может поступить либо от блока 11 управления (второй вход элемента ШШ 34), либо от блока 12 ввода (первый вход элемента ИЛИ ЗА).

924

На фиг. 10 в качестве примера приведены временн1)1е диагргичмь работы формирователя при условии, что

блок 32 памяти содержит информацию, приведенную в таблице на фиг. 9.

Формирователь 9 псевдослучайной последовательности работает следующим образом.

В исходном состоянии счетчик 43 установлен в нулевое состояние. Управляющий сигнал от блока 11 управле- ния (с соответствующего разряда поля 70 кода микроопераций) поступает на

вход Пуск генератора 41 псевдослучайных чисел и вход элемента 47 задержки. Генератор 41 вырабатьшает на своем выходе псевдослучайное число, которое поступает на информацион-

ньй вход счетчика 42 столбцов. К этому моменту времени на выходе Jлeмeн- та 47 задержки появляется управляющий сигнал, фиксирующий случайное число в счетчике 42 столбцов. Изменение содержимого счетчика 42 запускает процесс чтения памяти 44 модифицированной матрицы переходных вероятностей, на выходе которой появляется следующее состояние цепи Маркова. К

этому моменту времени на выходе элемента 48 задержки появляется управляющий сигнал, который фиксирует в счетчиках 43 строк и 45 адресов памяти кодов следующее состояние цепи. Изменение содержимого счетчика 45 адресов запускает процесс чтения из памяти 46 кодов, на выходе которой появляется код псевдослучайной последовательности, соответствующий зафиксированному в счетчике 45 адресов состоянию цепи Маркова. При поступлении очередного сигнала пуска, генератор;, 41 псевдослучайных чисел вновь вырабатывает псевдослучайное число, которое

фиксируется в счетчик 42 столбцов и т.д.

Блок 11 управления работает следующим образом.

В исходном состоянии содержимое счетчика 49 команд и регистра 51 команд равно нулю, а на выходе памяти 50 команд установлен код команды, записанной по нулевому адресу памяти 50.

По первому тактовому импульсу от генератора 30 тактовых импульсов в регистр 51 команд с в lxoдa памяти 50 команд записьшается команда, которая

хранится по нулевому адресу. При этом адрес с выхода 51.1 адреса блока 6 сверхоперативной памяти, адрес с выхода 51.2 адреса блока 10 памяти тестов поступают на адресные входы блоков 6 и 10 соответственно и запускают процесс чтения. Сигналы соответствующих разрядов выхода 51.3 управления

вателя 7 синхросерий, соответствующий импульс через j-й элемент И группы 59 элементов И и элемент ИЛИ 60 проходит на выход узла 54 управления выборкой. Импульсы остальных меток времени на выход узла 54 управления выборкой не передаются, поскольку на первые входы всех элементов И группы

коммутаторами 23 и 24 поступают на уп-ю 9, за исключением j-ro, от дешифратора 58 поступает значение О.

равляющие входы коммутаторов 23 и 24, настраивая их на селекцию операндов для выполнения операции сравнения.

Код микроопераций с выхода 51.4 поступает на первые входы элементов И группы 53 элементов И. Адрес перехода с выхода 51.5 поступает на информационные входы счетчика 49 команд. Кад метки времени с выхода 51.6 поступает на вход дешифратора 58 узла .54 управления выборкой. Признак перехода с выхода 51.7 поступает на первый вход элемента ИЛИ 62 и вход инвертора 63 узла 55 анализа условий.

Момент выдачи сигналов микроопераций и начала выборки следующей команды определяется кодом, содержащимся в поле 72 кода метки времени команды, записанной в регистр 51 команд.

Допустим, что в поле 72 записан код J. При этом на j-м выходе дешифратора 58 установлено значение 1,а на остальных выходах - значение О.

До прихода метки времени с номером j блок 11 управления находится в состоянии ожидания. При этом тактовые импульсы, поступающие на вход приема регистра 51 команд, не вызывают изменение содержимого регистра 51 , поскольку вход памяти 50 команд остается без изменений. В то же время тактовые импульсы поступают на вход синхронизации триггера 64 условий, на информационный вход которого с выхода элемента ИЛИ 61 поступает результат сравнения: О, если по всем разрядам выхода блока 4 сравнения получены О (совпадение по всем разрядам) и в противном случае (несовпадение хотя бы по одному разряду). Таким образом, к моменту прихода метки времени с номером j в триггере 64 условий будет записан результат. сравнения, шфабатываемый блоком 4 сравнения непосредственно перед приходом метки.

С приходом метки времени с номером j, т.е. с появлением импульса на j-м выходе второй группы выходов формироI

вателя 7 синхросерий, соответствующий импульс через j-й элемент И группы 59 элементов И и элемент ИЛИ 60 проходит на выход узла 54 управления выборкой. Импульсы остальных меток времени на выход узла 54 управления выборкой не передаются, поскольку на первые входы всех элементов И группы

9, за исключением j-ro, от дешифра-ю 9, за исключением j-ro, от дешифра

.

15

20

{

30

тора 58 поступает значение О.

Сигнал с выхода узла 54 управления выборкой поступает на вторые входы элементов И группы 53 элементов И, разрешая вьщачу микроопераций на соответствующие выходы группы управляющих выходов блока 11 управления и нэ первые входы элементов И 56 и 57, на вторые входы которых поступают выходные сигналы блока 55 анализа условий. Сигналы с выхода узла 55 анализа условий разрешают прохождение сигнала с выхода узла 54 управления выборкой либо на вход Прием, либо на

25 вход Счет счетчика 49 команд. При этом в счетчике 49 команд фиксируется ;адрес следующей команды. Изменение содержимого счетчика 49 команд запускает процесс чтения из памяти 50 ко- I

манд, на выходах которого появляется очередная команда. Тактовый импульс вновь записывает считанную команду в регистр 51 команд, поле 72 кода метки времени команды вновь поступает на дешифратор 58 узла 54 управления выборкой и т.д.

Таким образом, выдача сигналов микроопераций и начало выборки очередной команды выполняется в моменть

40 времени, задаваемые полем 72 кода метки времени команды.

При формировании адреса очередной команды возможны следующие режимы работы блока 11 управления.

Первый режим. Команды выполняются- в порядке их записи в памяти 50 команд (линейный участок программы). При этом в поле 71 адреса перехода команды записьшается адрес .текущей команды, увеличенный на единицу, а в поле 73 признака перехода записывается значение 1. При выполнении указанной команды адрес перехода с выхода 51.5 регистра 51 команд поступает н-а информационный вход сче гчика 49 команд, а признак перехода - на первый вход элемента ИЛИ 62 и вход инвертора 63. При этом значение 1 с выхода элемента ИЛИ 62 поступает на пер35

45

50

55

2715

Bbu i вхол элемента И 56 и при приходе cvirna.na от пыхода узла 54 управления выборкой, на вход Прием счетчика 49 команд. Таким образом, в счетчик 49 команд записывается адрес следующей по порядку команды. Отметим, что по входу Счет счетчика 49 команд сигнал не поступает, поскольку на втором входе элемента И 57 с выхода элемента И bb поступает значение О, т.е. на первый вход элемента И 66 подается значение ).

Второй режим. Выполняется переход по указанному адресу (безусловный переход) , При этом в поле 71 адреса перехода команды записывается адрес, по которому необходимо выполнить бе- зуслонньш переход, а в поле 73 признака перехода записывается значение l. Работа блока 11 управления при рассма-1 риваемом режиме полностью совпадает с работой в первом режиме,

Третий режим. Переход по указанному адресу выполняется в зависимости от результата операции сравнения, выполняемой в блоке 4 сравнения (условный переход).

В этом в поле 71 адреса перехода команды записьгаается адрес, по которому необходимо выполнить переход при условии, что результат операции сравнения по всем незамаскированным разрядам равен О. В поле 73 признака перехода записывается значение О При выполнепн указанной команды значение О признака перехода поступает .на вход инвертора ЬЗ, на выходе которого появляется значение 1.

Если к моменту прихода метки времени триггер 64 условий установлен в нулевом состоянии (результат сравнения равен нулю), на выходе элемента И 65 установлено значение 1, которое через элементы Ш1И 62 и И 56 разрешает прохождение сигнала с выхода узла 54 управления выборкой на вход Прием счетчика 49 команд. Тем самым в счетчик 49 команд, записывается адрес с поля 71 команды.

Если же триггер 64 условий установлен в единичное состояние (результат сравнения равен единиде), выход элемента И 66 установлен в 1 и сигнал с выхода узла 54 управления выборкой поступает на вход Счет счетчика команд, увеличивая его содержимое на единицу. Тем самым, начинает928

я процесс выборки команды, следующей за рассматриваемой.

Работа блока 11 управления прекраается при отсутствии тактовых импульсов, т.е. при останове генератора 30 тактовых импульсов. Генератор 30 тактовых импульсов может быть остановлен программно командой, в поле 70 микр.оопераций которой соответствуюисий разряд установлен в 1, либо принудительно от блока 12 ввода.

Формула изобретения

памяти, генератор псевдослучайных

тестов, формирователь псевдослучайной последовательности, блок памяти тестов, блок управления, блок ввода, . блок вывода, эталонный микропроцес-

сорный блок, причем первая и вторая группы выходов блока регистров и первая и вторая группы информационных входов блока сравнения подключены соответственно к группе входов-выходов эталонного микропроцессорного блока и группе входов-выходов устройства для подкоаочения к входам-выходам контролируемого микропроцессорного блока, третья группа выходов блока регистров соединена с группой разрешающих входов блока сравнения, группа входов синхронизации блока регистров, блока сверхоперативной памяти, группы адресных входов группы

входов синхронизации генератора псевдослучайных тестов, группа адресных входов формирователя псевдослучайной последовательности и группа адресньк входов блока памяти тестов подключе- ны к первой группе выходов блока управления, первая, вторая и третья группы информаид онных входов блока мультиплексоров соединены соответ- ,ственно с группой выходов генератора псевдослучайных тестов, группой выходов формирователя псевдослучайной последовательности и группой выходов блока памяти тестов, вторая группа выходов блока управления сое-

динена с первой группой информационных входов блока вывода, группа входов кода команды блока Управления соединена с группой информационных выходов блока ввода, отличаю

щ е е с я тем, что, с целью расшире- ния функциональных возможностей за счет возможности программирования алгоритмов контроля при различных сочетаниях временных, параметров синхро- последовательностей объекта контроля, устройство, содержит формирователь синхросерий, первая и вторая группы выходов которогр соединены соответственно с первой группой информационных входов блока регистров и группой входов синхросерий блока управления, вход останова формирователя синхросерий подключен к первой группе выходов блока управления, тактовый выход формирователя синхросерий подключен к тактовому входу блока управления, группа входов логических условий бло

ка управления соединена с второй груп-20 мирователя синхросерий, выход второ- пой информационных входов блока вывода и группой выходов блока сравнения группа управляющих входов блока сравнения и группа управляющих входов

го элемента ИЛИ соединен с суммирующим входом счетчика, вход сброса которого соединен с выходом третьего элемента ИЛИ, группа выходов счетчиго элемента ИЛИ соединен с суммирующим входом счетчика, вход сброса которого соединен с выходом третьего элемента ИЛИ, группа выходов счетчиблока вывода подключены к первой груп-25 ка подключена к адресным входам блока

пе выходов блока управления ,первая группа выходов блока мультиплексоров соединена с третьей:группой информационных входов блока сравнения и с второй группой информационных входов бло-30 пой информационных входов регистра.

ка регистров, третья группа информационных входов которого подключена к второй группе выходов блока мультиплексоров, группа адресных входов блока мультиплексоров соединена с группой н 1ходов блока сверхоперативной памяти, группа управляющих входов блока регистров, группа входов записи блока сверхоперативной памяти, группа управляюпи1х входов формирователя синхросерий, группа управляющих входов генератора псевдослучайных тестов , группа управляющих входов формирователя псевдослучайной последовательности, группа входов записи блока памяти тестов, группа входов записи блока управления подключены к группе управляющих выходов блока ввода, группы информационных входов блока сверхоперативной памяти, формирователя синхросерий, генератора псевдослучайных тестов, формирователя псевдослучайной последовательности и блока памяти тестов подключены к группе информационных выходов блока ввода.

9

счетчик,

блок

30 памяти.

регистр, группу

элементов И, элемент задержки, причем первые входы первого, второго и третьего элементов ИЛИ, вход пуска ге- нератора тактовых импульсов, вход записи блока памяти, вход сброса регистра соединены с соответствующими входами группы управляющих входов формирователя синхросерий, вход останова генератора тактовых импульсов соединен с выходом первого элемента ИЛИ, второй вход которого соединен с входом останова формирователя синхро- серий, выход генератора тактовых импульсов соединен с вторым входом второго элемента ИЛИ, с входсм элемента задержки, с входом записи регистра,а также с а1ходом тактовых сигналов фор

мирователя синхросерий, выход второ-

го элемента ИЛИ соединен с суммирующим входом счетчика, вход сброса которого соединен с выходом третьего элемента ИЛИ, группа выходов счетчика подключена к адресным входам блока

памяти, информационные входы которого соединены С группой информационных входов формирователя синхросерий, выходы блока памяти соединены с груп-

5

0

5

0

5

нулевой разряд регистра соединен с вторым входом третьего элемента ИЛИ, выходы разрядов первой группы регистра соединены с первыми входами элементов И группы, вторые входы которых соединены с ь кодом элемента задержки, выходы разрядов второй группы регистра соединены с первой группой выходов формирователя синхросерий, а выходы элементов И группы соединены с второй группой выходов.формирователя синхросерий.

с соответствующими разрядами выхода поля адреса перехода регистра команд, выходы счетчика команд подключены к адресным входам памяти команд, а также соединены с второй группой выходов блока управления, информационные входы памяти команд соединены с группой входов кода команды блока управления, суммирующий вход счетчика команд соединен с выходом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, вход записи счетчика команд подключен к выходу второго элемента И, первый вход которого соединен с выходом первого элемента ИЛИ узла анализа условий, выходы памяти команд соединены с информационными входами регистра команд, вход записи которого соединен с входом тактовых сигналов блока управления выходов разрядов полей адреса блока сверхоперативной памяти, адреса блока памяти тестов, управления коммутацией регистра команд соединены с.соответствующими выходами первой группы выходов блока управления,выходы разрядов поля микроопераций регистра команд соединены с первыми входами соответствующих элементов И группы, вторые входы которых соединены с первым входом пер вого и вторым входом второго элементов И и выходом элемента ИЛИ узла управления выборкой, .а выходы подключены к соответствующим выходам первой

группы выходов блока управления, выходы разрядов поля метки времени регистра команд соединены с входами дешифратора узла управления выборкой, выходы дешифратора соединены с первыми входами соответствующих элементов И группы узла управления выборкой, вторые входы которых подключены к соответствующим входам группы входов синхросерий блока управления, а выходы соединены с входами элемента ИЛИ узла управления выборкой, выход поля признака перехода регистра команд со5 единен с входом элемента НЕ и первым входом первого элемента ИЛИ узла анализа условий, входы второго элемента ИЛИ узла анализа условий соединены с соответствующими входами группы входов логических условий блока управления , а выход соединен с информационным входом триггера условий, синхровход которого соединен с входом записи регистра команд, прямой выход тригге5 ра условий соединен с первым входом первого элемента И узла анализа условий, выход которого соединен с вторым входом первого элемента И ,инверсный выход триггера условий соединен с первым входом второго элемента И узла ан&- лиза условий, выход которого соединен с вторым входом первого элемента ИЛИ узла анализа условий,выход элемента НЕ соединен с вторыми входами первого и второго элементов И узла анализа условий.

0

0

0ml

Omtl

Отв Фиг.1

ОтЗОтЮОтП

Omtl

о/п/г

Фиг.

ftp 7 К гЩОкгЗОт 7

А ь

ч f

г

г„

Mi4i . .J-tLrrLj.

иb:il..J

5

J0|

От 7

ч f

Mi4i J-tLrrLj.

5

fa

я

«м

J0|

JinJlJTJlJTJl UinJTJ

Т9nn

лП

(Otn.t

Фиг-7

Фи.9

ri

ишлши

n

ОСЮСЮСХ :

осххх:ос

5Z7П.

91

9гI L

ллллллъа/

Л

Л

03 и г. 10

| Устройство контроля микропроцессорных блоков | 1982 |

|

SU1042023A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-23—Публикация

1988-04-11—Подача