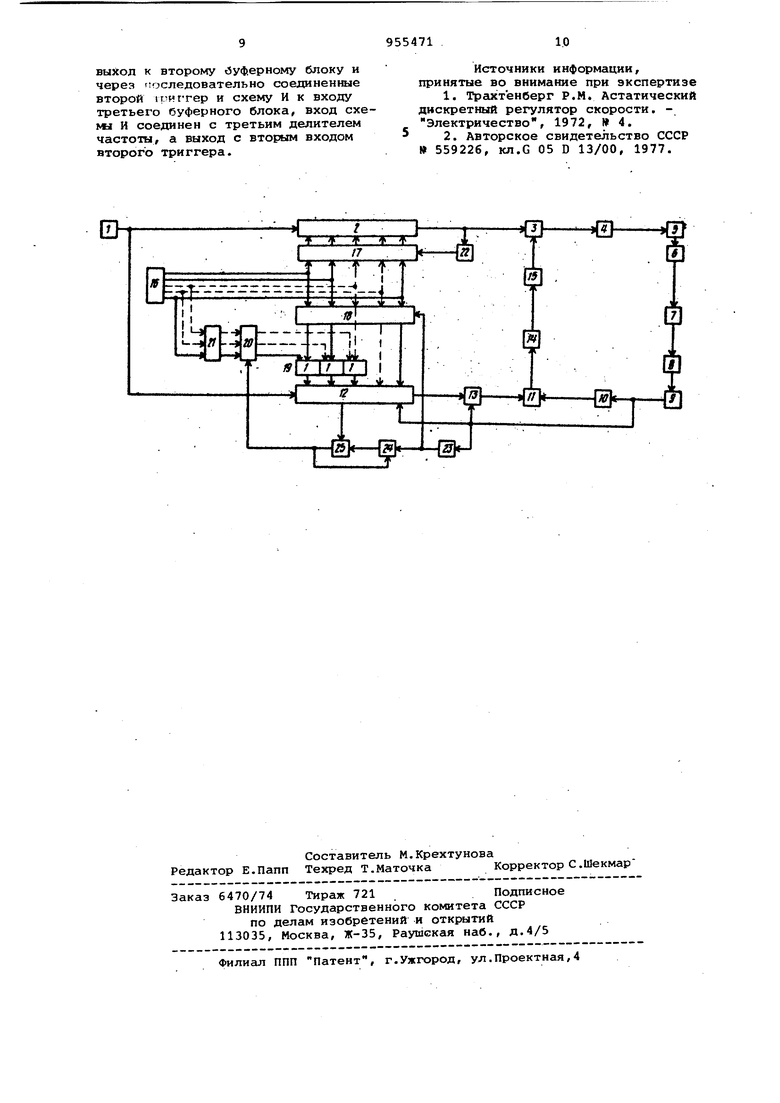

Данное устройство позволяет регу лирор ать скорость вращения вала исполнительного двигателя изменьнием коэффициентов деления первого и тре тьего делителей. При этом первым де лителем производится плавное регули рование скорости, третьим делителем грубое Недостатком известного устройств является недостаточные -плавность и точность установки регулируемой скорости вращения исполнительного двигателя. Частота Jигнaлa, поступа ющего на силовой ключ, должна находиться в пределах 500-ZOOO Гц, Нижняя граница обусловлена недопустимы 1И пульсациямитока в двигателе, чт вызывает его нагрев, и малой добротностью контура регулирования, ухудша ющей регулятора скоростио Верхняя граница обусловлена потерями в силовых ключах и уменьш нием устойчивости устройства из.за увеличения добротности контура регулирования. При повышенных требованиях к помехоустойчивости приме няются микросхемы с относительно ма лым быстродействием, что ограничива ет частоту кварцевого генератора на уровне 0,5-1 МГц. Учитывая, что Км при устойчивой работе устройства и хороших динамических показателях находится в диап зоне -Ку 15-20, п 2Ку 30-40 и при указанных выше ограничениях изменением коэффициента деления пер вого делителя можно получить не более 65 ступеней скорости. Полученное значение ступеней при плавном регулировании недостаточно для использования услгройства в автоматизи рованных установках, работающих сой местно с вычислительными устройства ми . 1 Цель изобретения - повышение точ НОСТИ регулирования скорости. Указанная цель достигается тем, что в устройство дополнительно введены три буферных блока,, дешифратор блок элементов ИЛИ, схема И, второй триггер, два одновибратора и переключатель , одни выходы которого через первый буферный блок подключены к входам первого делителя частоты, другие через второй буферный блок подключены к входам третьего делите ля частоты, причем одни непосредственно, а другие через блок элементов ИЛИ, другие входаа которого чере третий буферный блок и дешифратор подключены к выходам переключателя, вход первого одновибратора подключе к выходу первого.делителя частоты, а выход - к управляющему входу первого буферного блока, вход другого одновибратора подключен к выходу второго делителя частоты, а выход к второму буферному блоку и через последовательно соединенные второй триггер и схему И к входу третьего буферного блока, причем вход схемы И соединен с третьим делителем частоты, а выход с вторым входом второТо триггера. На чертеже представлена блок-схема предлагаемого устройства. Устройство для регулирования скорости вращения электродвигателя содержит генера тор 1 импульсов, выход которого через последовательно соединенные первый делитель 2 частоты, блок. 3 распределения импульсов, компаратор 4 и силовой ключ 5 подключен к исполнительному электродвигателю 6, датчик 7 частоты вращения которого через последовательно соединенные первый формирователь 8, второй делитель 9 частоты и элемент 10 задержки соединен с первым входом первого триггера 11, к второму входу которого подключены последовательно соединенные третий делитель 12 частоты, входом подключенный к выходу генератора 1 импульсов, и элемент ИЛИ 13, а выход первого триггера 11 через расширитель 14 импульсов и второй формирователь 15 подключен к блоку 3 разделения импульсов, вторые входы третьего делителя 12 частоты и элемента ИЛИ 13 объединены и подключены к выходу второго делителя 9 частоты, переключатель 16, одни выходы которого через первый буферный блок 17 подключены к входам первого делителя 2 частоты, другие через второй буферный блок 18 подключены к входам третьего делителя 12 частоты, причем одни непосредственно, а другие через блок 19 элементов ИЛИ, другие входы которого через третий буферный блок 20 и дешифратор 21 подключены к выходам переключателя 16, вход первого одновибратора 22 подключен к выходу первого делителя 2 частоты, а выход к управляющему входу первого буферного блока 17, вход другого одновибратора 23 подключен к выходу второго делителя 9 частоты, а выход к второму буферному блоку 18 и через последовательно соединенные второй триггер 24 и схему И 25 к входу третьего буферного блока 20, причем вход схемы И 25 соединен с третьим делителем 12 частоты, а выход с вторым входом второго триггера 24. Устройство работает следующим образом. Импульсы эталонной частоты fg, получаемой делением на делителе 2 в К раз частоты fp генератора 1, сравниваются по фазе со скорректированными импульсами частоты „«. Частота в среднем равна измеренной частоте ц и имеет фазовый сдвиг, пропорциональный корректирующему сигналу. Частот ц получается путем деления делителем 9 частотного сигнала, вырабатыв емого частотным датчиком 7, соедине ным с валом исполнительного электро двигателя 6. При этом сигнал с частотного датчика предварительно формируется формирователем 8. С приходом каждого импульса частоты э ком паратор подключает через силовой .ключ 5 исполнительный двигатель 6 к сети, а с приходом каждого импульса частоты fи выдает сигнгш на торможе ние исполнительного электродвигателя, т.е. среднее напряжение получается пропорциональным разности фаз сравниваемых частот э и f ик Коррекция, необходимая для обеспечения устойчивости работы регулятора скорости и работающая только при небольших рассогласованиях частот э и fу, , осуществляется изменением фазы сигнала частоты yi на вел чину, пропорциональную отклонению скорости вращения вала исполнительного двигателя. Установившийся режим работы устройства возможен только при э и или Тэ TV, . Поэтому отклонение ско рости от установившегося значения . можно выявить, сравнивая период Ти измеренной частоты с периодом Тэ эталонной частоты. . Для упрощения введения опережающего по фазе частоту ц сигнала при отрицательной разности сравниваемых периодов, возникающей при отклонении скорости вращения двигателя вверх от установившегося значения, в устройст во вводится начсшьный сдвиг по фазе в установившемся режиме 3 ) между измеренной м и скорректированной частотами такой величины, чтобы расширенная в Ку раз разность между периодом .Ти и вычитаемым временным интервалом Тд была равна половине периода Тд эталонной частоты с точностью до допустимо малой величины (т„ - ТО)КУ +d, где К„ - коэффициент расширения отклонения, выбираегиый из условия обеспечения устойчивой работы и качественной динамики регулятора .скорости j 6 - абсолютная ошибка расширенного отклонения от середины периода эталонной частоты в установившемся режиме работы устройства. При отклонении измеренной частоты ц от эталонной сдвиг по фазе час тоты ик относительно частоты f„ опре деляется выражением (Ти - Т,)Ку Чноц + Ч , где Тц - период частотьа f , соответствующий скорости вращения исполнительного двигателя со ПРИ(0 Wye т .2|Г§ Изменение коэффициента деления делителя 2 эталонного канала для регулирования э, осуществляется начальной записью в делитель числа А, которое определяется переключателем 16. Обозначая через D Максимальное число, которое можно записать в делитель, или полный объем, получаем коэффициент деления К эталонного делителя 2 частоты К D - А Запись числа А в делитель 2 происходит после его переполнения, когда все его триггеры -находятся в состоянии О. По заднему фронту импульса, возникающего на выходе делителя в момент переполнения, запускается и формирует короткий импульс одновибратор 22, подключающий кратковременно шины, задающего переключателя к установочным входам триггеров дели.теля, что и производит запись числа А черезбуферный блок 17. При изменении эталонной частоты fg в соответствии с выражением (1) меняется значение временного интервала TO . Коэффициент деления В делителя 12, формирующего временной интервал Тд, определяется записью в делитель двух чисел А и X. После сброса делителя 12 импульсом измеренной частоты по заднему фронту последнего возбуждается Омновибратор 23, в результате чего кратковременно подключаются шины задающего переключа теля 16 к установочным входам триггеров делителя 12 одними входами непосредственно, а другими через блок 19 элементов ИЛИ, что приводит к записи в делитель числа А. В процессе счета импульсов, непрерывно поступающих на вход делителя от генератора 1, в момент обнуления триггеров, связанных установочными входами с дешифратором 21 через буферный блок 20 и блок 19 элементов ИЛИ, на выходе схемы И 25 появляется сигнал, разрешающий открытие буферного блока 20 и запись в эти триггеы числа X. Состояние X дешифрируется по -старшим разрядам задающего пееключател.я 16. Однотактность записи числа X за цикл вычисления Т, обеспечивает триггер 24, который устанавивается в состояние 1 задним фронтом одновибратора 23, а сбрасывается в момент появления импульса на выходе схемы И 25, запрещая до конца цикла формирование сигналов этой схемой. Коэффициент деления В делителя 1 определяется выражением В D - (А + X) Учитывая, что в установившемся режиме TS Тц , Т Тг-К То Т„В и выражения (3),(45 , получим Тц .-TO Тэ Т к -Т-в Т,,- Х Д т (5) Т.е. начальный сдвиг фаз определяется при постоянных старших разрядах задающего переключателя в установившемся режиме постоянным временным интервалом ДТ Тр-Х . Значение величины X определяется из условия равной относительной ошиб ки расширенного отклонения от середины периода эталонной частоты Разность Tj;( - TO в схеме выявляет ся триггером 11, Триггер 11 устанавливается В состояние 1 через элемент ИЛИ 13 по истечении времени Тд и сбрасывается с задержкой, определяемой элементом 10 на время f после прихода импульса частоты. Задержка, величина которой выбирается значительно меньшей, чем разность Тя - TO (в установившемся режиме Тр, - ), вводится для защитыот пропадания импульсов частоты при отклонении скорости исполнительного двигателя вверх от установившегося значения. Если Т( , то триггер 11 через элемент ИЛИ 13 устанавливается в состояние 1 в момент прихода импульса частотьТ f , а сбрасывается через время 1 . Время нахождения триггера 11 в состоянии 1 расширяется в Ку раз расширителем 14. Сформированный по заднему фронту расширенного сигнала формирователем 15 импульс частоты подается на второй вход блока 3 распределения импульсов. Блок 3 распре деления импульсов исключает возможность прихода импульсов частот «« и ts на вход компаратора 4 с интервалом, меньшим, чем разрешающая спо собность в-ходных элементов компаратора 4. Изменение уставок скорости исполнительного электродвигателя можно пр изводить не только изменением коэффициента деления эталонного делителя 2, но и изменением коэффициента деле НИН делителя 9 в канале измеренной частоты, причем делителем 2 произво дится плавное регулирование скорости, а делителем 11 грубое. Общее число ступеней NCT изменени скорости двигателя при изменении ко эффициентов деления делителей часто ты 2 и 9 NCY (К/«акс- Кщян )С коэффициент деления делителя 9; ддакс мин максимальное и минимальное значение эталонной частоты ., ; максимальное и минимальное значение эталонной частоты. Таким образом, предлагаемое устройство обеспечивает большую точность регулирования за счет того, что имеет большее количество ступеней изменения скорости вращения исполнительного двигателя по сравнению с известными устройствами. Формула изобретения Устройство для регулирования скорости вращения электродвигателя, содержащее генератор импульсов, выход которого через последовательно соединенные первый делитель частоты, блок распределения импульсов, компаратор и, силовой ключ подключен к электродвигателю, датчик частоты вращения которого через последовательно соединенные первый формирователь, второй делитель частоты и элемент задержки соединен с первым входом первого триггера, к второму входу которого подключены последовательно соединенные третий делитель частоты, входом подключенный к выходу генератора импульсов, и элемент ИЛИ, а выход первого триггера через расширитель импульсов и второй формирователь подключен к блоку распределения импульсов, вторые входы третьего делителя частоты и элемента ИЛИ объединены и подключены к выходу второго делителя частоты, отличающееся тем, что, с целью повышения точности регулирования, в него дополнительно введены; три буферных блока, даяифратор, блок элементов ИЛИ, схема И, второй триггер, два одновибратора и переключатель, одни выходы которого через первый буферный блок подключены к входам первого делителя частоты, другие через второй буферный блок, подключены к входам третьего делителя частоты, причем одни непосредственно, а другие через блок элементов ИЛИ, другие входы которого через третий буфернь1й блок и дешифратор подключены к выходам переключателя, вход одного одновибратора подключен к выходу первого делителя частоты, а выход -.к управляющему входу первого буферного блока, вход другого одновибратора подключен к выходу второго делителя частоты, э

выход к второму буферному блоку и через 1;оследовательно соединенные второй чриггер и схему И к входу третьего буферного блока, вход схеtti И соединен с третьим делителем частоты, а выход с вторым входом второго триггера.

Источники информации, принятые во внимание при экспертизе 1. Трахтенберг P.M. Астатический дискретный регулятор скорости, Электричество, 1972, 4. 2. Авторское свидетельство СССР 559226, кл.С 05 D 13/00, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматический регулятор частоты | 1982 |

|

SU1078571A1 |

| Регулятор скорости | 1975 |

|

SU559226A1 |

| Устройство для регулирования скорости электропривода | 1986 |

|

SU1322229A1 |

| Устройство для регулирования скорости электропривода | 1988 |

|

SU1539725A1 |

| Электропривод постоянного тока | 1986 |

|

SU1374388A1 |

| Регулятор частоты электроагрегата | 1985 |

|

SU1288891A1 |

| Электропривод | 1986 |

|

SU1390757A1 |

| Двухдвигательный электропривод с механическим дифференциалом | 1973 |

|

SU866678A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1783577A2 |

| Электропривод постоянного тока | 1984 |

|

SU1220097A1 |

Авторы

Даты

1982-08-30—Публикация

1981-01-05—Подача