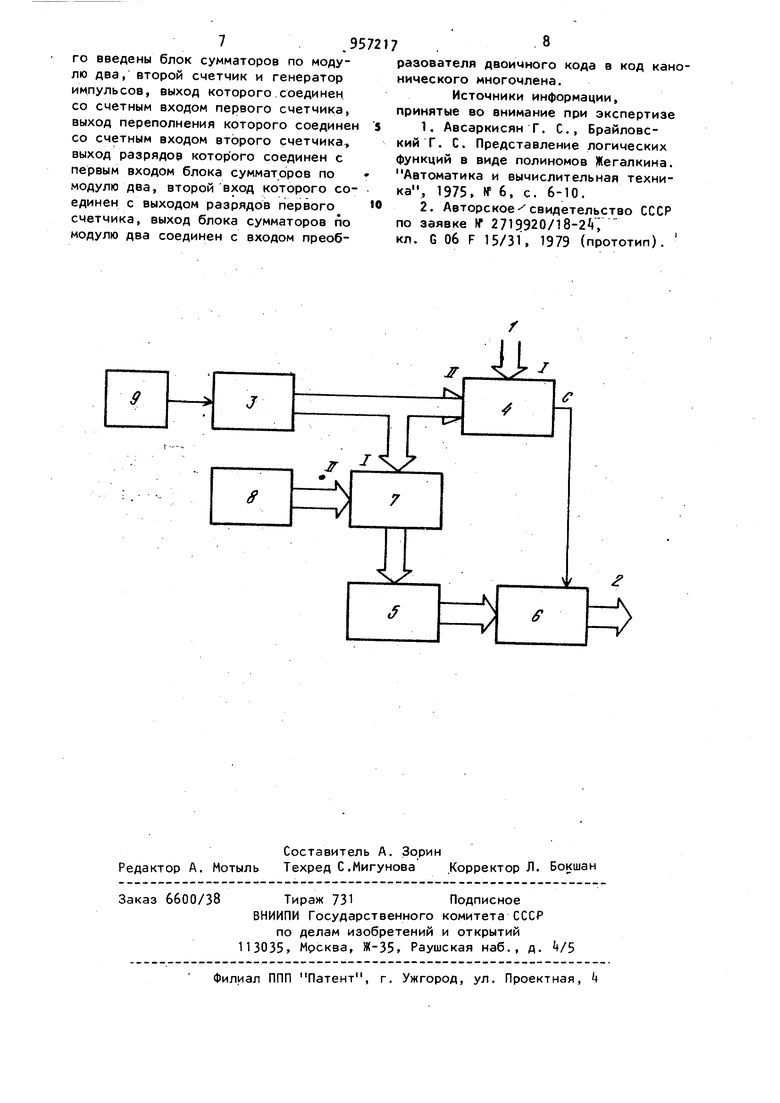

3 . 95 код канонического многочлена и блок фор мирования результата,информационный и управляющий входы которого соединены соответственно с выходами преобразователя двоичного кода в код канонического многочлена и мультиплексора, управляющий вход которого соединен с выходом разрядов первого счетчика, информационный вход мультиплексора соединен с входом преобразователя, выход которого соединен с выходом блока формирования результата, дополнительно введены блок сумматоров по модулю два, второй счетчик и генератор импульсов, выход которого соединен со счетным входом первого счетчика, выход переполнения которого соединен со счетным входом второго счетчика, выход разрядов которого соединен с первым входом блока сумматоров по модулю два, второй вход которого соеди нен с выходом рязрядов первого счетчика, выход блока сумматоров по моду лю два соединен с входом преобразова теля двоичного кода в код канонического многочлена. На. чертеже дана блок-схема .устрой ства. Устройство включает вход 1 преобразователя, выход 2 преобразователя, счетчик 3, мультиплексор-4, преобразователь 5 двоичного кода в код канонического многочлена, блок 6 формирования результата, блок 7 сумматоров по модулю два, счетчик 8 и генератор.9 импульсов. Рассмотрим назначение элементов схемы. Вход 1 (исходных данных) имеет 2 разрядов. Исходная логическая 4)ункция задается в виде таблицы истинности. Значения функций на двоичных на борах подаются на соответствующие разряды входа 1 (исходных данных), значение функций на 1-м наборе подается на i-ii-l разряд входа 1. Выход 2 (результата) имеет 2 раз рядов и предназначен для выдачи per зультата. Канонический многочлен в общем случае имеет вид F(X,, Хэ,...,Хи) Ao0-A X ffi ..+А„Хп ©Aп,X J. +) Qt . .+А (п-1) 3 © .. . . Х, где А - значения коэффициентов, соответствующие вхождени конъюнкции в многочлен (при А 1). Значение выходной информации в шине результата соответствует значениям коэффициентов А следующим образом: 1-й группе разрядов выхода 2 ставится в соответствие п-разрядное двоичное число, соответствующее десятичному эквиваленту числа 1-1 (так как нумерация выводов идет с номера 1). В рассматриваемом двоичном коде К переменных входят в прямой форме и (п-К) в инверсной (К О, п). Значение сигнала 1 на 1-й группе разрядов выхода 2 соответствует вхождению в канонический многочлен конъюнкции из К . букв, входящих в двоичный код в прямом виде, например, для получаем, Если на выходе 2 двоичный код 101001101, это соответствует каноническому многочлену вида . Таким образом, двоичный код на выходе 2 однозначно определяет вид канонического многочлена для заданной логической функции. Счетчики 3 и 8 обеспечивают подсчет поступающих на его вход импульсов. В данном преобразователе применен счетчик суммирующего типа и может быть выполнен по любой известной схеме для формирования п-разрядного двоичного слова, соответствующего количеству поданных на его вход импульсов. Мультиплексор i имеет п управляющих входов, 2 информационных входов, 5, 9 один выход и предназначен для выбора соответствующего разряда из информационного двоичного кода на основании управляемого двоичного кода и выдачи его значения на- выход мультиплексора. Преобразователь 5 двоичного кеда в код канонического многс члена содержит п элементов НЕ и z.С„ эле iKr-Zментов И, входы которых соединены с выходами элементов НЕ, выходы элементов И являются выходами преобразователя, входами которого являются входы элементов НЕ. Блок 6 формирования результата предназначен для хранения и сложения по модулю 2 промежуточных многочленов и содержит 2 -1 элементов Ии 2 триггеров, причем входы элементов И соединены с управляющим входом и соо ветствующими информационными входами Блок 7 сумматоров по модулю два предназначен для инверт1 рования сигналов, поступающих с выходов .. первого счетчика, в соответствии со значениями сигналов, поступающих с второго счетчика. Если обозначить сигналы первой группы входов q , вто рой группы входов Ь , то выходной сигнал описывается логической функцией i l, п rt fj-l -I- . В основе работы устройства лежит тождественное преобразование вида т Л , Х, ) л.2,...,Х ... . Обозначим Х-через,X , тогда получаем f(X, Х,, ...,Х, ...,Хп). Это приведет к преобразованию исходной таблицы истинности и в общем случае к различному виду канонического мног члена. Для п входных переменных сущее вует 2 возможных инверсий входных переменных. Номера инвертируемых перокенных генерирует второй счетчик 8, Если сигнал на его выходах 00...О то схема работает, как прототип. Устройство работает следующим образом. Значение исходной функции на всех двоичных наборах (в порядке возраста ния номеров) подается на вход. Счетчик 3 формирует последовательность двричных наборов. Эти наборы преобра зуются в соответствии со значением 7 о выходных сигналов счетчика о в новые наборы в блоке 7. Для каждого из них в преобразователе 5 определяется вид промежуточного многочлена. Если на рассматриваемом наборе исходная функция принимает значение 1 (сигнал на выходе мультиплексора k равен 1)| то промежуточный многочлен записывается в блок 6 формирования результата, где производится его суммирование по модулю два с результатом предыдущего суммирования (в исходном состоянии содержимое триггеров 00...О). По окончании 2 тактов на выходах блока 6, образующих выход 2, получаем результат преобразования. Этот процесс повторяется для различных значений выходных сигналов счетчика 8, полученные результаты сравниваются с выбора лучшего по заданным критериям. Например, критерий минимального числа букв соот-. ветствует минимальному числу ральных микросхем при построении схемы по каноническому многочлену. Таким образом, применение предлагаемого устройства позволяет механизировать ручные методы синтеза логических структур и преобразования логических функций в канонический многочлен,уменьшить трудоемкость преобразований, увеличить достоверность и надежность, автоматизировать процесс перебора вариантов. Формула изобретения Функциональный преобразователь, содержащий первый счетчик, мультиплексор, преобразователь двоичного кода в код канонического многочлена и блок формирования результата, информационный и управляющий входы которого соединены соответственно с выходами преобразователя двоичного кода в код канонического многочлена и мультиплексора, управляющий вход которого соединен с выходом разрядов первого счетчика, информационный вход мультиплексора соединен с входом преобразователя, выход которого соединен с выходом блока формирования результата, отличающий ся тем, что, с целью расширения класса решаемых задач за счет возможности воспроизведения различных вариантов представления логических функций в виде канонического многочлена, в не7.95721;

го введены блок сумматоров по модулю два, второй счетчик и генератор импульсов, выход которого соединен со счетным входом первого счетчика, выход переполнения которого соединен $ со счетным входом второго счетчика, выход разрядов которого соединен с первым входом блока сумматоров по модулю два, второй вход которого соединен с выходом разрядов первого счетчика, выход блока сумматоров по модулю два соединен с входом преоб . 8 разователя двоичного кода в код канонического многочлена.

Источники информации, принятые во внимание при экспертизе

1,Авсаркисян Г. С., Брайловский Г. С. Представление логических функций в виде полиномов Жегалкина. Автоматика и вычислительная техника, 1975, ff 6, с. 6-10.

2.Авторское- свидетельство СССР по заявке If 2719920/18-2 7

кл. G Об F 15/31, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1980 |

|

SU903890A2 |

| Функциональный преобразователь | 1978 |

|

SU781822A1 |

| Устройство для вычисления синдромов кода Рида-Соломона | 1990 |

|

SU1751860A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Преобразователь формы представления логических функций | 1987 |

|

SU1474671A1 |

| Перестраиваемый цифровой фильтр с программируемой структурой | 2016 |

|

RU2631976C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| Устройство для вычисления значений группы функций | 1988 |

|

SU1656532A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГОЛ-КОД | 2013 |

|

RU2530336C1 |

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

д

ь

Авторы

Даты

1982-09-07—Публикация

1980-12-31—Подача