(54) ГЕНЕРАТОР ПСЕВДОСЛУ ХАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1991 |

|

RU2030104C1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

| Генератор псевдослучайной последовательности | 1981 |

|

SU1013954A1 |

| Генератор псевдослучайных чисел | 1989 |

|

SU1691839A2 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| Генератор псевдослучайной последовательности | 1987 |

|

SU1528770A1 |

| Генератор псевдослучайных последовательностей | 1981 |

|

SU993444A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| Генератор псевдослучайных равномерно распределенных двоичных цифр | 1988 |

|

SU1709305A1 |

Изобретение относится к области i вычислительной техники и может быть использовано при статистическом моделировании систем автоматического управления.

Известен генератор псевдослучайных двоичных чисел, содержащий регистры сдвига с сумматорами по модулю два в цепях обратной связи и тактовый генератор, выход которого соединен с тактовыми входами регистров сдвига. При этом второй вход сумматора по модулю два каждого последующе17О регистра сдвига соединен с Выходом одной из ячеек предьадущего регистра сдвига. Длина генерируемой псевдослучайной последовательности определяется разрядностью регистров сдвига и и числом регистров w:М - 1 l.

Недостатком данного устройства является громоздкость злектронной схемы и сложность ее настройки при большой длине генерируемой последовательности, вызванные большим числом регистров сдвига и связей между ними.

Наиболее близким техническим решением к данному изобретению является генератор псевдослучайной последовательности , содержащий регистр сдвига и сумматор помодулю два в цепи обратной свяи, генератор тактовых импульсов, выход которого соединен со входом регистра сдвига, а также счетчик и блок сумматоров 2.

Недостатком данного устройства является малое значение периода псев10дослучайной последовательности, ог- ; раниченное разрядностью регистра сдвига. Максимальная длина последовательности равна 2 - 1. Увеличение периода последовательности за

15 счет разрядности регистра приводит к усложнению схемы и снижению ее надежности.

Цель изобретения - упрощение генератора при заданной длине после20довательности.

Для достижения поставленной цели в генератор псевдослучайной последовательности, содержащий счетчик, генератор тактовых импульсов, выход

25 которого соединен со входом Сдвиг регистра сдвига, выход которого является выходом генератора и соединен с первым входом сумматора по модулю два, второй вход которого соединен с выходом 1 -го разряда регистpa сдвига, введены элемент задержки и блок памяти, выход которого соединен с информационным входом регистра сдвига, выход сумматора по модулю два соединен с информационным входом блока памяти, адресные входы которого соединены с соответствующими разрядными выхода2 ш счетчика, суммирующий вход которого объединен со входом считывания блока памяти и подключен к выходу гене ратора тактовых импульсов, выход которого через элемент задержки соединен со входом записи блока па.мяти.

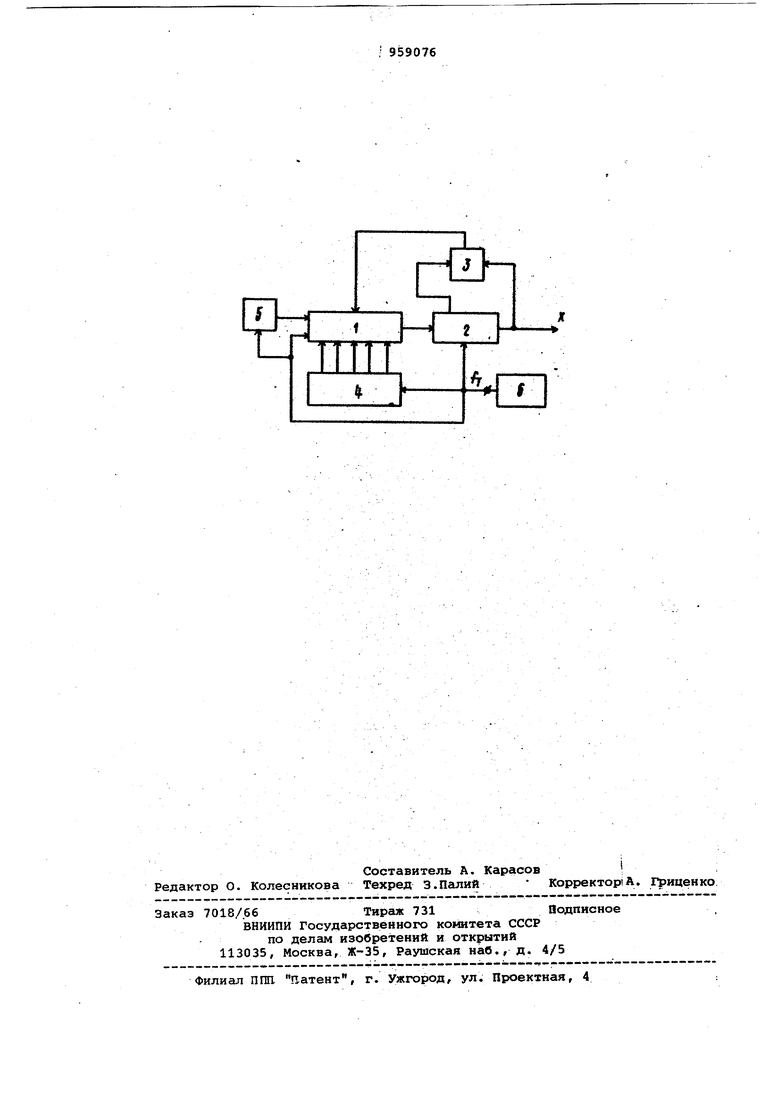

На чертеже приведена структурная схема генератора.

Генератор содержит блок 1 памяти выход которого соединен со входом регистра2 сдвига, выходы которого соединены со входами сумматора 3 по модулю два, выход которого соединен со входом блока 1 Пс1мяти, входы которого соединены с выходами счетчика 4, элемента 5 задержки и генера:тора б тактовых импульсов, вы ход которого соединен также со входами регистра 2 сдвига, счетчика 4 и элемента 5 задержки.

Генератор работает следующим образом. .

Сигнал IT с выхода генератора б поступает на счетчик 4,регистр 2 сдвига и на вход считывания блока 1 . Каждый тактовый импульс, поступающий на вход счетчика 4, увеличивает на единицу код на его разряд ных выходах, тем сгаллм изменяя адрес опрашиваемой ячейки блока. Тем. же импульсом осуществляется считывание содержимого выбраниой ячейки на информационный вход регистра 2 сдвига и сдвиг числа, записанного в регистре сдвига. На выходе сумматора по модулю два формируется Двоичное число, определяемое состоянием разрядов регистра сдвига, подключен ных к его входам. Через время Т , определяемое элементом задержки 5, происходит запись числа с выхода сумматора по модулю два в опрошенную ячейку блока пгьмяти. Во время работы счетчик проходит все N своих возможных состояний, число которых объему памяти блока 1 памяти, и на информационный вход регистра сдвига поступает последовательность двбичных чисел, записанных в блок 1 памяти на N тактов ранее. В результате работа, выполняемая блоком 1 памяти при данной организации процессов записи и считывания, анашогична работе Н-разрядно го регистра сдай

га, а всю схему генератора можно рассматривать как N+ К-разрядный регистр сдвига, в цепь обратной связи которого включен сумматор по модулю два. Здесь К - число разрядов регистра сдвига 2.

Таким образом, за счет увеличения объема памяти блока 1 памяти при соответствующем выборе номеров, подключаемых к сумматору по модулю два разрядов регистра, длина генерируемой псевдослучайной последователности может быть увеличена до значения М - 1.

Аппаратурные затраты на реализацию предлагаемого устройства при больших значения N+ К значительно меньше, чем затраты на изготовление N + К-разрядного регис тра сдвига. Так, например, прииспользовании микросхем серии К134 оперативное запоминающее устройство с объемом памяти N 1024 строится на одной микросхеме 1К134РУб) с потребляемой мощностью О,6 Вт, в то время как регистр сдвига длиной N 1024 может быть построен как минимум на 128 микросхемах ( К134ИР2). Потребляемая устройством мощность при этом составит 5 Вт.

Формула изобретения

Генератор псевдослучайной последовательности , содержащий счетчик, генератор тактовых импульсов, выход которого соединен со входам сдвга регистра сдвига, выход которого является выходом генератора и соединен с первым входом сумматора по модулю два, второй вход которого соединен с выходом i-ro разряда регистра сдвига, отличающийс Я тем, что, с целью упрощения генератора, он содержит элемент задержки и блок памяти, выход которого соединен с информационным входом регистра сдвига/ выход сумматора по модулю два соединен с информационным входом блока памяти, адресные входы которого соединены с соответствующими разрядными выходами счетчика, суммирующий вход которого объединен со входом считывания блока памяти и подключен к выходу генератора тактовых импульсов, выход которого через элемент задержки соединен со входом записи блока памяти

Источники информации, принятые во внимание при зкспертизе

524175, кл. G 06 F 1/02,1975 (прототип).

1Ы

н

Авторы

Даты

1982-09-15—Публикация

1981-02-02—Подача