(Л

с

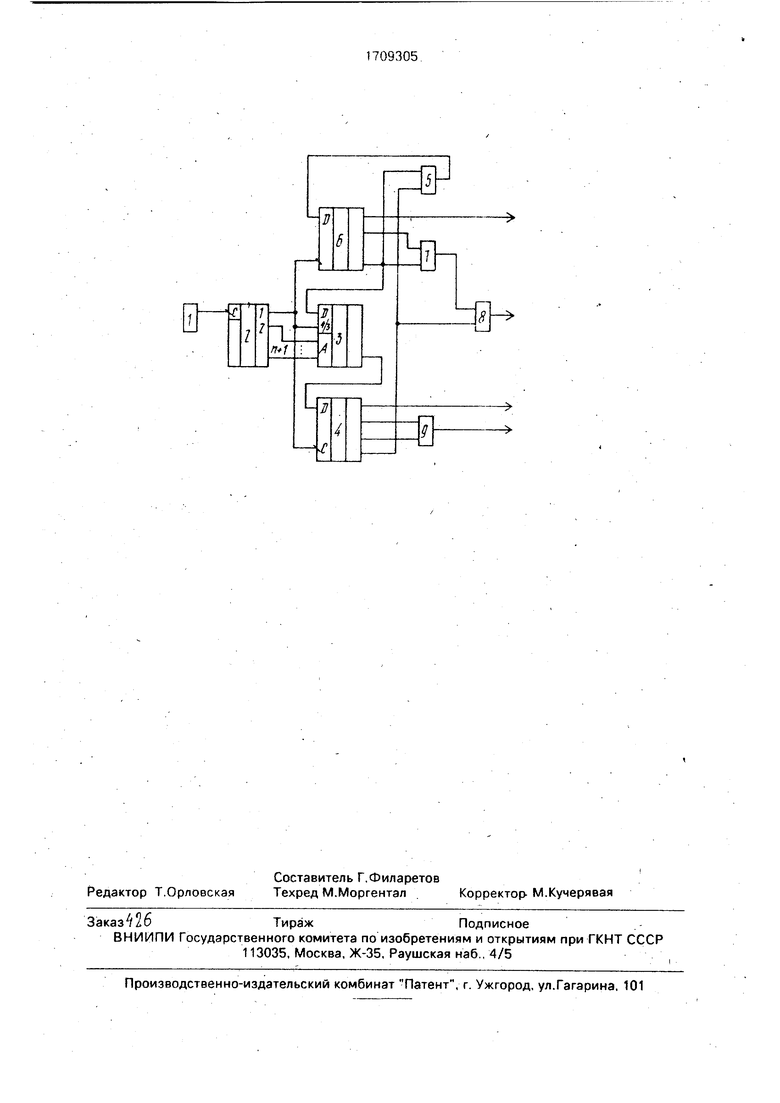

памяти. Тем самым завершается один цикл работы, длительность которого равна двум периодам импульсов, поступающих с выхода генератора 1 тактовых импульсов. С приходом очередного тактового импульса изменяется на единицу содержимое п разрядов двоичного счетчика, что приводит к изменению адреса ячейки блока 3 памяти. От цикла к циклу код на адресных входах блока 3 последовательно нарастает. Процесс продолжается до заполнения счетчика 2, а затем повторяется. По всей сути регистр 4 сдвига, блок 3 памяти и дополнительный регистр 6 сдвига в совокупности с первым сумматором 5 по модулю два образуют генератор псевдослучайных последовательностей на регистре сдвига с линейной обратной связью, причем общая длина такого регистра равна в данном случае и может быть выбрана очень больщой. Генерируемые двоичные цифры снимаются в первых разрядных выходов регистров 4 и 6 сдвига и с выходов третьего и четвертого сумматоров 8, 9 по модулю два.

Использование сумматоров 7,8 и 9 позволяет практическиИСКЛЮЧИТЬ взаимную зависимость генерируемых двоичных цифр. Точки подключения входов сумматоров 5-9 по модулю два, а также точки сьема выходного сигнала определены опытным путем и обеспечивают при достаточно большой период генерируемой псевдослучайной последовательности, независимость и равномерное распределение генерируемых двоичных кодов.

Формула изобретения Генератор псевдослучайных равномерно распределенных двоичных цифр, содержащий генератор тактовых импульсов, двоичный счетчик, блок памяти, регистр сдвига и первый сумматор по модулю два,

причем выход генератора тактовых импульсов соединен со счетным выходом двоичного счетчика, первый разрядный выход которого соединен с входом синхронизации

регистра сдвига и входом управления чтением-записью блока памяти, остальные разрядные выходы счетчика соединены с адресным входом блока памяти, информационный выход которого соединен с ииформационным входом регистра сдвига, выход старшего разряда которого соединен с первым входом первого сумматора по модулю два, отличающийся тем, что, с целью повышения быстродействия, в него введены

дополнительный регистр сдвига и три сумматора по модулю два, причем четвертый разрядный выход дополнительного регистра сдвига соединен с информационным входом блока памяти и с первым входом

второго сумматора по модулю два и со вторым входом первого сумматора по модулю два. выход которого соединен с информацирнным входом дополнительного регистра сдвига, вход синхронизации которого соединен с первым разрядным выходом двоичного счетчика, второй разрядный выход дополнительного регистра сдвига соединени со вторым входом второго сумматора по модулю два, выход которого соединен с первым входом третьего сумматора по модулю два, второй вход которого соединен с четвертым разрядным выходом регистра сдвига, второй и третий разрядные выходы которого соединены соответственно с первым и вторым входами четвертого сумматора по модулю два, первый разрядный выход дополнительного регистра сдвига, выходы третьего и четвертого сумматоров по модулю два и первый разрядный выход регистра

сдвига являются разрядным выходом генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных кодов | 1983 |

|

SU1167710A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

| Генератор псевдослучайной последовательности | 1981 |

|

SU959076A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

| Генератор псевдослучайных чисел | 1989 |

|

SU1691839A2 |

| Генератор псевдослучайной последовательности | 1981 |

|

SU1013954A1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Устройство генерации равномерно распределенных псевдослучайных чисел | 2024 |

|

RU2840424C1 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1991 |

|

RU2030104C1 |

Изобретение относится к вычислительной технике и может использоваться при мадвлироаании случайных процессов. Целью изобретения является повышение быстродейЁтвия. Для этого в устройство, содержащее генератор 1 тактовых импульсов, двоичный счетчик 2, блок 3 памяти, регистр 4 сдвига и первый сумматор 5 по модулю два, дополнительно введены регистр 6 сдвига и трги сумматора 7, 8 и 9 по модулю два.. Использование указанной структуры позволяет повысить быстродействие генератора за счет того, что соседние по времени отсчеты выходного кода становятся независимыми, 1 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Лабичев В.Н | |||

| Генератор псевдослучайного сигнала | |||

| - Приборы и техника эксперимента, 1982, N? б, с.72-73, рис.1.- | |||

Авторы

Даты

1992-01-30—Публикация

1988-10-03—Подача