Изобретение относится к импульс|ной технике и может быть использовано для формирования тестовых последовательностей при контроле и диагностике неисправностей цифровЕлх устройств автоматики, телемеханики И вычислительной техники

Известно устройство для формиро- вания псевдослучайных сигналов сложной структуры, содержащее генератор тактовых импульсов, генератор псев- . дослучайной последовательности, элемент И, электронный ключ, счетчик тактов, элемент НЕ, дешифратор, счетчик циклов и триггер, позволяницее формировать многократно повторяемые периоды псевдослучайной поспедова тельности, сдвинутые один относитель но другого на заданный интервал времени 11 .

Недостатком это.го устройства является невозможность формирования псевдослучайной последовательности в обратном направлении и блокирования выходных сигналов устройства: на отдельных отрезках последовательности,

Наиболее близким по технической сущности к предлагаемому является 17енератор псевдослучайных последовательностей, содержащий генератор такг

товых импульсов, . элемент И, первый вход которого соединен с выходом генератора тактовых импульсов, вычи таклций счетчик, счетный вход которого соединен с выходом элемента И, группу элементов И, выхода1 которых являются выходами генератора, h-разрядный реверсивный сдвигающий регистр, установочный вход кото|юго соединен с шиной Установка, вход синхронизации соединен с выходом элемента И, а выходы соединены с первьши входами группы элементов И, первьШ и второй сумматоры по модулю два, входы которых соединены с выходами реверсивного сдвигакщего регистра, а выходы соединены соответственно с. первьв и вторым информационными входами реверси вного сдвигающего ре20гистра 2 . . .

Недостатком этого устройства являются его ограниченные функциональные возможности,- так как при использовании генератора псевдослучайных поспедовательностей в качестве источника входных тестовых воздействий контролируекалх устройств в ряде случаев непосредственно воспользоваться последовательностью кодов генератора не . ддается, поскольку в этих устройствах возникают состояния неопределенности вследствие одр- временного изменения нескольких входных воздействий, появления на входах контролируемых устройств запрещенных комбина.ций и других причин. Иногда для проверки правильности функционирования устройств требуется повторение определенных участков.последовательности кодов генератора Ч пересчетные схемы ), поэтому при контроле целесообразно использовать не всю псевдослучайную последовательность кодов, а отдельные ее участки, формируемые в прямом или обратном направлении, с блокировкой или без блокировки выходных сигналов,генератора, для этого предварительно необходимо составлять программу проверки контролируемых устройств, определяющую порядок и характер формирования отдельных участков псевдослучайной последовательности. Выполнять эту программу путем изменения вручную выполняемых генератором функций,как в известных устройствах., тр/доемко и практически невозможно, вследствие большой скорости изменения тестовых воздействий контролируемых устройств.

Цель изобретения - автоматизация процесса формирования запрограммированных участков генерируемой последовательности.

Поставленная цель достигается тем, что в генератор псевдослучайных последовательностей., содержащий генератор тактовых импульсов, выход которого соединен 0 первыгл в.ходоЬ элемента И, выход которого подключен |К счетному входу вычитающего счетчика, и к синхронизирующему входу п (разрядного реверсивного регистра сдвига, установочный вход которого соединен с шиной установки, первый и второй информационные входы соединены соответственно через первый и второй сумматоры по модулю два с соответствующими выходами п-разрядного реверсивного регистра сдвига, выходы которого также соединены с первь 1и входами блока элементов И, дополнительно введены буферный запоминающий блок, регистр:, сдвига и блок управления, первый вход которо го соединен с шиной установки, второй вход соединен р выходом генератора тактовых импульсов, третий вход соединен с выходом вычитающего счетчика, а четвертый вход подключен к первому выходу регистра сдвига:, первый выход.блока управлёйия со едине с вторым входом элемента И, второй выход подключен к входу считывания буферного запоминающего блока, .установочный вход которого соединен с шиной установки, управляющий выход буферного запоминающего блока под-

ключен к входам записи вычитающего счетчика и регистра сдвига, а первая и вторая группа выходов подключена к информационным входам вычитающего счетчика и регистра сдвига

соответственно, причем второй и

третий выходы регистра сдвига соединены с входом управления п-разрядного реверсивного регистра сдвига и с вторыми входами блока элементов И.

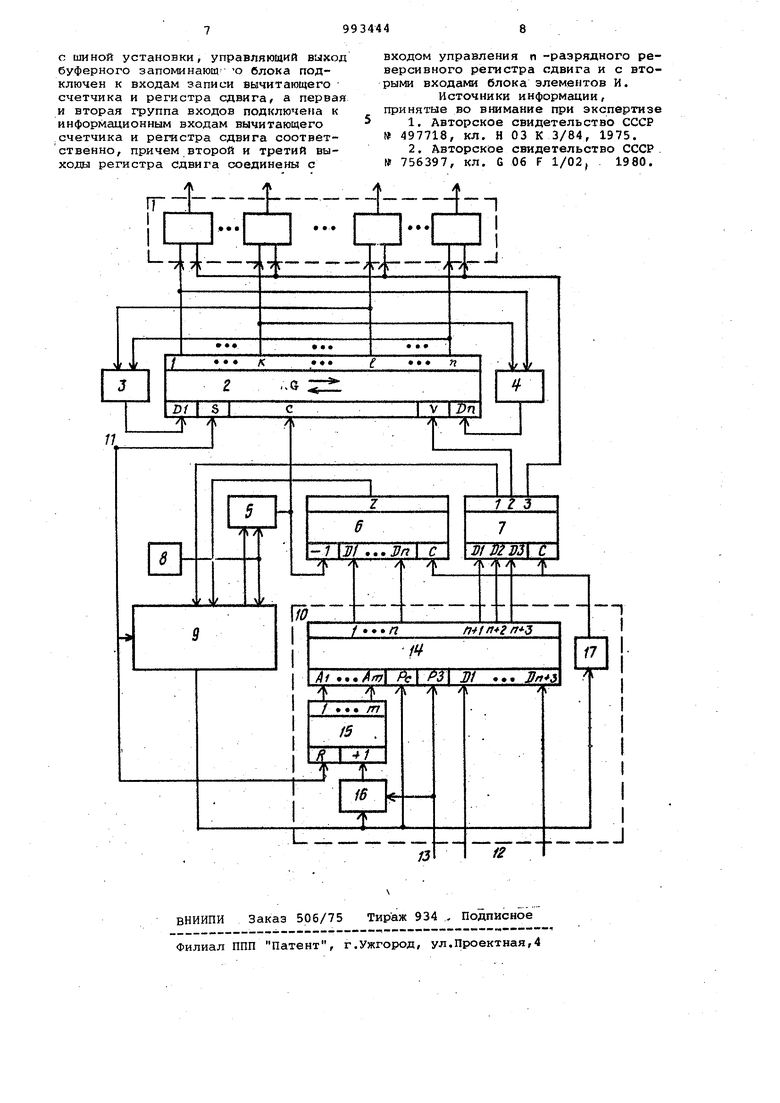

На чертеже приведена функциональная схема генератора псевдослучайных последовательностей.

Генератор псевдослучайных последовательностей содержит блок 1 элементов И, Г1 -разрядный реверсивный perjiCTp 2 сдвига, сумматоры 3 и 4 по модулю 2, элемент И 5, вычитающий счётчик 6, регистр 7 сдвига, генератор 8 тактовых иг-шульсов,

блок 9 управления, буферный запоминающий блок 10, шину 11 установки, шины 12 информационных входов, шину 13 записи. . .

На чертеже также показан пример .выполнения буферного запоминающего блока 10, который содержит запоминающий блок 14 с произвольной выборкой, с четчик 15 адреса, элемент ИЛИ 16 и формирователь 17 импульсов.

Блок 9 управления выполнен на D-триггерах.

Генератор работает следующим образом.

Перед Началом работы составляется программа формирования выходной псевдослучайной последовательности кодов в виде последовательности управляющих СЛОВ.. Каждое управляющее слово -имеет (п + 3) разряда,где п - разрядность регистра 2. Первые п.разрядов управляющего слова А1...АП содержат двоичный код длины и отрезка псевдослучайной последовательности, на которой генератор выполняет одну из возможных операций, предусмотренных в коде операции. Код операции содержится в {п + 1), (п + 2), (п + 3)-ем разрядах управляющего слова .(Ao4-t . Ati,,).-Разряд А„4.1 содержит признак конца программы. в последнем управляивдем слове программы, а в остальных словах Af,. 1. Разряд определяет направление формирования отрезка псевдослучайной последовательности: в прямом направлении при А ti+2 1 и в обратном направлении при Ап+2 0. Разряд , А„.з определяет состояние выхода генератора. Если А 1/ то на выход поступает формируемая генера- . тором последовательность кодов. Eoni (An+ji 0, то на выходе поддерживается уровень логического О, а формируемав генератором последовательность кодов не поступает потребите5.лю (маскируется).

Составленная программа загружается в блок 10, где она хранится и может быть многократно использована. Перед загрузкой программы сигналом по шине 11 обнуляется счетчик

15адреса блока 10 На шины 12 подается первоеуправляющее слово программы и сигналом по шине 13 оно записывается в нулевую ячейку памяти.. Сигнал с шины 13 через элемент ИЛИ

16поступает на счетный вход счетчика 15 и своим задним фронтом переводит его в следующееосостояние. Аналогично в блок 14 записываются остальные управляющие слова программы. После загрузки программы сигналом

по шине 11 снова обнуляется счетчик 15 и устанавливаются в исходные состояния регистр 2 и блок 9 управления. На выходе блока 9 управления формируется сигнал, вьодаваемый на вход разрешения считывания блока 10. На информационные входы блока 10 поступает первое управляющее слово из нулевой ячейки памяти. Сигнал с выхода формирователя 17, задержанный относительно сигнала на входе разрешения считывания блока 14, переписывает первые п разрядов управляющего слова (д ) в вычитающий счетчик б, а (п + 1), (п + 2), (п + 3)-ий разряды (код операции) - в регистр 7 После окончания считывания управляющего слова из блока/ 10 на первом выходе блока 9 управления проявляется сигнал, разрешающий прохождение импульсов с генератора 8 тактовых импульсов через элемент И 5 на вход синхронизации регистра 2 и на счетщо вход вычитающего счетчика 6. При это в зависимости от сигнала на входе управления направлением сдвига регистра 2 происходит сдвиг информации в регистре 2 в прямом или обратном направлении, и формируется псевдослучайная последовательность кодов в прямом или обратном направлении. В зависимости от состояния третьего регистра 7 генерируемая последовательность кодов поступает на выход устройства или .блокируется с помощью . блока элементов И 1. Каждый импульс ; на выходе элемента И 5 уменьшает сог держимое вычитающего счетчика б на единицу. После Л сдвигов регистра 2 счетчик б обнуляется, на его выходе Z формируется сигнал, поступающий в блок 9 управления. В результате на выходе блока 9 управления пояйляетсй сигнал,.запрещающий прохождение импульсов через элемент И 5. Так кончается формирование первого отрезка псевдослучайной последовательности/ кодов, соответсзтвуннцего первому уп равляющему слову npoipaMivH. После этого блок 9 управления формирует сигнал на вход разрешения считывания блока 10, и второе управляющее

слово программы переписывается в 6 и регистр 7. Формируется iковый отрезок псевдослучайной посде.довательности кодов в соответствии ;с кодом операции, записанном в реги5 стре 7, длиной в & кодов, занесенной ;в счетчик 6, и т.д. Управляюпще слов програмкы по порядку считываются из блока 10 до тех пор, пока в последнем управлянадём слове проходит призт10 нак конца программы, которой блокирует в блоке 9 управления выдачу сигналов разрешения считывания в блок 10.

Таким образом, введение в генера15 тор псевдослучайных последовательностей блока 9 управления, регистра 7 и блока 10 позволяет организовать автоматическую работу генератора по заранее разработанной программе, воз2Q можности составления выходной последовательности кодов из отдельных отрезков псевдослучайной последовательности , формируемых в прямом или обратном направлении, с блокировкой

25 или без блокировки выхода устройства, что позволяет .более эффективно использовать генератор для контроля и диагностики цифровых устройств.

30

Формула изобретения

Генератор псевдослучайных последовательностей, содержащий генератор тактовых импульсов, выход кото35рого соединен с первым входом эле-,

мента И, выход которого подключен к счетному входу вычитающего счетчика, и к синхронизирующему BXOKLп-разрядного реверсивного регистра

40 сдвига, установочный вход которого соединен с шиной установки, первый и второй информационные взсодаа соединены соответственно через первый и второй сумматоры по модулю два с

45 соответствующими, выходами h -разрядного реверсивного регистра сдвига, выходы которого также соединены с . первыми входами блока элементов И, о тл и ч ающий с я тем, что/

JQ с целью автоматизации процесса формирования запрограммированных участков генерируемой последовательности, в него дополнительно введены буферный запоминающий блок, релистр сдвиг

f и блок управления, первый вход кото рого соединен с шиной установки, второй вход соединен с выходом генератора тактовых импульсов /третий вход соединен с етходом вычитающего счетчика, а четвертый вход подключен к

первому выхдду регистра сдвига, первый выход блока управления соединен с вторым входом элемента; И, вторсЛ выход подключен к входу счи-швамия буферного запо этнаюа его блока, ус65 тановочный вход которого соединен

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных последовательностей | 1987 |

|

SU1443141A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Генератор псевдослучайных последовательностей | 1983 |

|

SU1127079A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Устройство для имитации сбоев | 1990 |

|

SU1836684A3 |

Авторы

Даты

1983-01-30—Публикация

1981-06-01—Подача