(54) УСТРОЙСТВО ДЛЯ РАСЧЕТА ВРЕМЕННЫХ ЗАТРАТ ОПЕРАТОРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синтеза регрессионных моделей многомерной статистики | 1980 |

|

SU942031A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Тренажер оператора радиоэлектронной аппаратуры | 1989 |

|

SU1658193A1 |

| Устройство для деления | 1981 |

|

SU987621A1 |

| МУЛЬТИКОНТРОЛЛЕР РАСПРЕДЕЛЯЕМОЙ ПАМЯТИ | 2014 |

|

RU2550555C1 |

| Устройство для ввода информации | 1985 |

|

SU1327087A1 |

| Устройство контроля | 1984 |

|

SU1198542A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ КОРРЕКЦИИ ПОГРЕШНОСТИ ЧАСТОТЫ ТАКТОВОГО ГЕНЕРАТОРА МИКРОКОНТРОЛЛЕРА (ВАРИАНТЫ) | 2008 |

|

RU2390786C1 |

| Устройство для определения изменения свойств случайных процессов | 1983 |

|

SU1205154A1 |

Изобретение относится к области вычислительной техники и может быть использовано для электронного моделирования задач оптимального планирования и в автоматических системах управления.

Известно устройство, предназначенное для решения частной задачи оптимального планирования, содержащее генератор импульсов, регистры, счетчики запоминающие устройства и соответст-. вующие связи 1 .

Недостатком этого устройства является сложность структуры и процеду « поиска решения, усложняющая конструкцию устройства.

Наиболее близким по технической сущности к данному является устройство для решения задачи оптимального распределения ресурсов, содержащее генератор импульсов, триггер, счетчики, три блока памяти, блок умножения, блоки вычитания, причём первые входы генератора импульсов, первого и второго блоков памяти являются входами устройства, первый выход первого блока памяти соединен с первым входом первого блока умножения 2.

Недостаток устройства состоит в том, что с его помощью невозможно

использовать непосредственно для расчета временных затрат оператора с . учетом структуры рабочегЬ места.

Цель изобретения - повышение точности устройства за счет учета структуры рабочего места при вычислении продолжительности освоения оператором структурной сложности аппаратуры,

10 а также повышение производительности, сокращение оборудования.

Поставленная цель достигается тем, что в устройство для расчета временных затрат оператора, содержащее генератор иштульсов, триггер, первый

15 и второй счетчики, первый и второй блоки памяти, блок умножения, первые входы блоков памяти и вход генератора импульсов являются соответственно первыми тремя входами устройства,

20 первый выход первого блока памяти соединен с первым входом первого блока умножения, введены блок регистров, два компаратора, четыре сумматора, второй триггер, четыре блока умноже25ния, блок деления и блок индикации, вход блока регистра является четвертым входом устройства, первый выход второго блока памяти соединен с первым входом второго блока умножения,

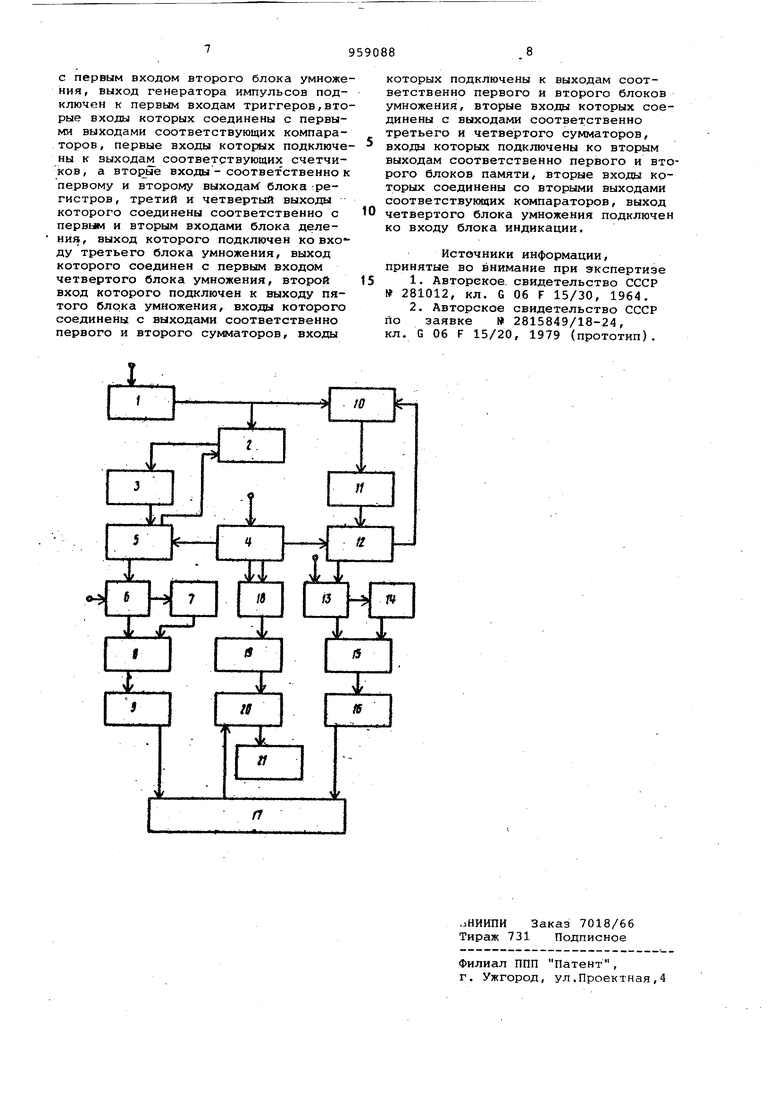

30 (выход генератора импульсов подключен к первым входам триггеров, вторые входы которых соединены с первыми выходами соответствующих компараторо первые входы которых подключены к вы ходам соответствующих счетчиков, а вторые - соответственно к первому и второму выходам блока регистров, тре тий и четвертый выходы которого соединены соответственно с первым и вто рым входами блока деления, выход которого подключен ко входу третьего блока умножения, выход которого соеци1 ен с первым входом четвертого бло ка умножения, второй вход которого подключен к выходу пятого блока умно жения, входы которого соединены с выходами соответственно первого и вт рого сумматоров, входы которых подключены к выходам соответственно пер вого и второго блоков умножения, вто рые входы которых соединены с выхода ми соответственно третьего и четвертого сумматоров, входы которых подключены ко вторым выходам соответственно первого и второго блоков памяти, вторые входы которых .соединены со вторыми выходами соответствующих компараторов, выход четвертого блока умножения подключен ко входу блока индикации. Математическая формулировка задачи состоит в следующем. Требуется определить То,..,.,(„,,„ где Т - временные затраты на освоение оператором структурной сложности аппаратуры; И - скорость восприятия и усвое ния оператором информации в одном знаке (слове); п - количество элементов рабоче го места, cLi - количество знаков (слов) в определении 1-го элемента; k - количество структурных подмножеств;п. - количество элементов в i-ом структурном подмножестве. На чертеже показана структурная схема устройства для вычисления вре-. манных затрат на освоение оператором структурной сложности аппаратуры. I Схема устройства содержит генераTcJp импульсов 1, триггер 2, первый счетчик 3, блок регистров 4 констант компаратор 5, блок памяти 6, сумматор 7, блок умножения 8, сумматор 9, три гер 10, счетчик 11, компаратор 12, блок памяти 13, сумматор 14, блок ум ножения 15, сумматор 16, блок умножения 17, блок деления 18, блок умноже ния 19, блок умножения 20, блок инди ;кации 21. Генератор импульсов 1, выполнен на интегральных схемах 155 серии. Первый вход eio является одним из входов устройства. Входами устройства являются также первые входы блока регистров 4 констант, блока памяти 6 и блока памяти 13. Выход генератора импульсов 1 соединен с первыми входами триггеров 2 и 10. Выход первого триггера 2 соединен с входом первого счетчика 3, выход которого соединен с первым входом компаратора 5, первый выход компаратора 5 соединен со вторым входом первого триггера 2. Второй вход компаратора 5 соединен со вторым входом блока памяти 6. Первый выход блока памяти б соединен с первым входом блокаиумножения 8. Второй выход блока памяти 6 соединен со входом сумматора 7, выход которого соединен со вторым входом блока умножения 8.Выход блока умножения 8 соединен с входом сумматора 9. Выход сумматора 9 соединен с первым входом блока умножения 17. Выход второго триггера 10 соединен с входом счетчика 11, выход которого соединен с первым входом компаратора 12. Второй вход компаратора 12 соединен с первым выходом блока регистров констант 4. Первый выход компаратора 12 соединен со вторым входом триггера 10. Второй выход компаратора 12 соединен со вторым входом второго блока памяти 13. Первый выход блока памяти 13 соединен с входом сумматора 14. Второй выход блока памяти 13 соединен с первым входом блока умножения 15. Второй вход блока умножения 15 соединен с выходом сумматора 14. Выход блока умножения 15 соединен с входом сумматора 1Б. Выход сумматора 16 соединен со вторым входом блока умножения 17, выход которого соединен с первым входом блока умножения 20.Второй выход блока регистров констант 4 соединен со вторым входом компаратора 5. Третий и четвертый выходы блока регистров констант 4 соединены соответственно с первым и вторым входами блока деления 18, выход которого соединен с входом блока умножения 19. Выход блока умножения 19 соединен со вторым входом блока умножения 20, выход которого соединен с входом блока индикации 21. Блок индикации представляет собой индикационную панель, на которой высвечивается результат. Выполнена на индикационных лампах типа ИН-14. Блоки памяти 6 и 13 представляют быстродействующую память, выполненную на интегральных схемах 133 серии. Устройство работает следующим образом. Перед началом работы в блок памятк б заносятся значения коэффициентов а, ck,2. -о/и - блок памяти 13 за- носятся значения коэффициентов п, , п 2., . ) пц. Значения констант п , k , г заносятся в блок регистров констант 4. В регистр множителя блока умножения 19 заносится значение 0,25 8регистр слагаемого сумматора 7 зано сится единица. В регистр слагаемого сумматора 14 заносится единица. Состояние счетчиков 3 и 11 устанавливается равным нулю. Триггеры 2 и 10 уетанавливаются в 1. В сумматоры 9и 16 записываются нули. По сигналу Пуск, поступающему на первый вход генератора импульсов 1, с генератора импульсов поступают сигналы на входы триггеров 2 и 10. С пер вого триггера 2 сигнал поступает на вход счетчика 3. При этом содержимое счетчика 3 устанавливается равным единице. На компаратор 5 поступает содержимое сметчика 3 и содержимое регистра блока регистров констант 4 (п). - Если содержимое счетчика 3 больше содержимого регистра блока регистров констант 4, то на триггер 2 поступает сигн&л с компаратора 5, вызывающий изменение его состояния (т.е. триггер 2 устанавливается в О) и запрещающий прохождение сигнала через триггер 2 с генератора импульсов 1. Если содержимое счетчика 3 меньше или равно содержимому первого регистра блока регистров констант 4, то на сумматор 7 поступает содержимое первой ячейки блока памяти 6. В суммато ре 7 производится сложение содержимо го первой ячейки блока памяти 6 и единицы. На блок умножения-8 поступа ет содержимое первой ячейки блока па мяти 6 и результат сумматора 7. Результат с блока умножения 8 поступает на сумматор 9. В сумматоре 9 произво дится сложение содержимого сумматора 9с результатом блока уг ножения 8 (т.е. накопление суммы .5. oL . Аналогично содержимоё счетчика 11 устанавливается равным единице. На компаратор 12 поступает содержимое счетчика 11 и содержимое второго регистра блока регистров 4 констант {к). Если содержимое второго счетчика 11 больше содержимого второго регистра блока регистров констант 4, то на триггер 10 поступает сигнал с компаратора 12, вызывающий изменение его состояния и запрещающий прохождение сигнала через триггер 10 с генератора импульсов 1. Если содержимое счетчика 11 меньше или равно содержимому второго регистра блока регистров 4 констант, то на сумматор 14 поступает содержимое первой ячейки блока памяти 13. 3 сумматоре 14 производится сложение содержимого первой ячейки блока памяти 13 и единицы. На блок умножения 15 поступает содержимое первой ячейки блока памяти 13 и результат сумматора 14. Результат с блока умножения 15 поступает на сумматор 16. В сумматоре 16 производится сложение содержимого сумматора 16 с результатом блока умножения 15, т.е. накопление суммы I И,- (г,,-ц . - Затем генератор импульсов 1 выдает второй импульс и устройство продолжает работу по указанному алгоритму; Генератор импульсов 1 выдает а тах|н,к импульсов. После этого на блок умножения .17. поступают результаты с суматоров 9 и 16. Результат с блока умножения 17 поступает на вход блока умножения 20. При этом содержимое третьего и первого регистров блока регистров 4 констант поступает на блок деления 18. В блоке деления 18 производится деление содержимого третьего регистра блока регистров констант 4 на содержимое первого регистра блока регистров 4 констант (т.е.Н(и-). Результат с блока деления 18 поступает на вход блока умножения 19, где производится умножение содержимого блока умножения 19 и результата блока деления 18 (т.е. 0,25т|и). Результат с блока умножения 19 поступает на вход блока умножения 20, где происходит перемножение результатов блока умножения 19 и блока умножения 17. На блоке индикации высвечивается результат работы устройства - значение временных затрат на освоение оператором структурной сложности аппаратуры. Устройство выполнено на интегральных схемах 155 и 133 серии и технической сложности при реализации не представляет. Использование изобретения позволяет расширить класс решаемых задач за счет возможности вычисления продолжительности освоения оператором структурной сложности аппаратуры. Формула изобретения Устройство для расчета временных затрат оператора, содержащее генератор импульсов, триггер, первый Уи второй счетчики, первый и второй блоки памяти, блок умножения, первые входы блоков памяти и вход генератора импульсов являются соответственно управляющим и информационным входами устройства, первый выход первого блока памяти соединен с первым входом блока умножения, отличающеес я тем, что, с целью повышения точности, в устройство введены блок регистров, два компаратора, четыре сумматора, второй триггер, четыре блока умножения, блок деления и блок индикации, вход блока регистров является четвертым входом устройства, первый выход второго блока памяти соединен

с первым входом второго блока умножения, выход генератора импульсов подключен к первым входам триггеров,вторые входы которых соединены с первыми выходами соответствующих компараторов , первые входы которых подключены к выходам соответствующих счетчиков, а вторые входы - соответственно к первому и второму выходам блока -регистров, третий и четвертый выходы которого соединены соответственно с первым и вторым входами блока деления, выход которого подключен ко входу третьего блока умножения, выход которого соединен с первым входом четвертого блока умножения, второй вход которого подключен к выходу пятого блока умножения, входы которого соединены с выходами соответственно первого и второго сумматоров, входы

которых подключены к выходам соответственно первого и второго блоков умножения, вторые входы которых соединены с выходами соответственно третьего и четвертого сумматоров, входы которых подключены ко вторым выходам соответственно первого и второго блоков памяти, вторые входы которых соединены со вторыми выходами соответствующих компараторов, выход четвертого блока умножения подключен ко входу блока индикации.

Источники информации, принятые во внимание при экспертизе 1- Авторское свидетельство СССР № 281012, кл. G Об F 15/30, 1964.

Авторы

Даты

1982-09-15—Публикация

1980-12-15—Подача