1

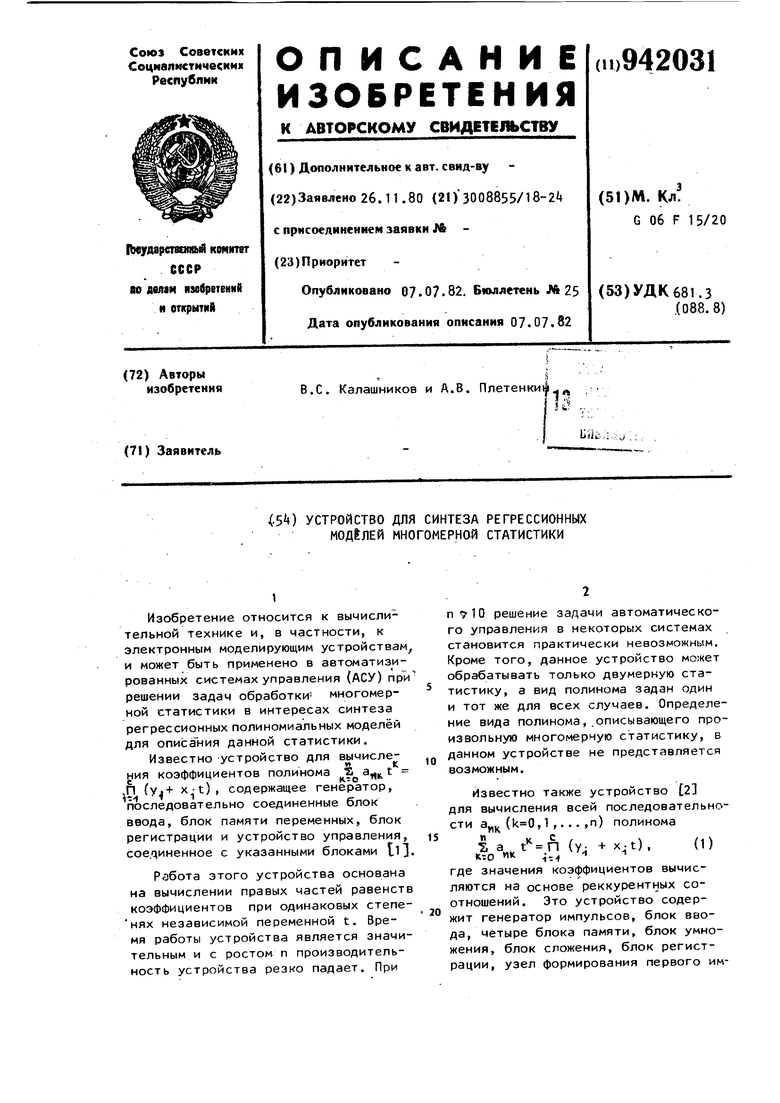

Изобретение относится к вычислительной технике и, в частности, к электронным моделирующим устройствам, и может быть применено в автоматизированных системах управления (АСУ) при решении задач обработки многомерной статистики в интересах синтеза регрессионных полиномиальных моделей для описёния данной статистики.

Известно устройство для вычисления коэффициентов полинома S а t П (Ул+ x-t), содержащее генератор, гюследовательно соединенные блок ввода, блок памяти переменных, блок регистрации и устройство управления, соединенное с указанными блоками til.

Работа этого устройства основана на вычислении правых частей равенств коэффициентов при одинаковых степенях независимой переменной t. Время работы устройства является значительным и с ростом п производительность устройства резко падает. При

П710 решение задачи автоматического управления в некоторых системах становится практически невозможным. Кроме того, данное устройство может обрабатывать только двумерную статистику, а вид полинома задан один и тот же для всех случаев. Определение вида полинома,.описывающего произвольную многомерную статистику, в данном устройстве не представляется

10 возможным.

Известно также устройство 2 для вычисления всей последовательности а,ц (,1 ,. ., ,п) полинома

IS

п

(Vi +

(1)

S

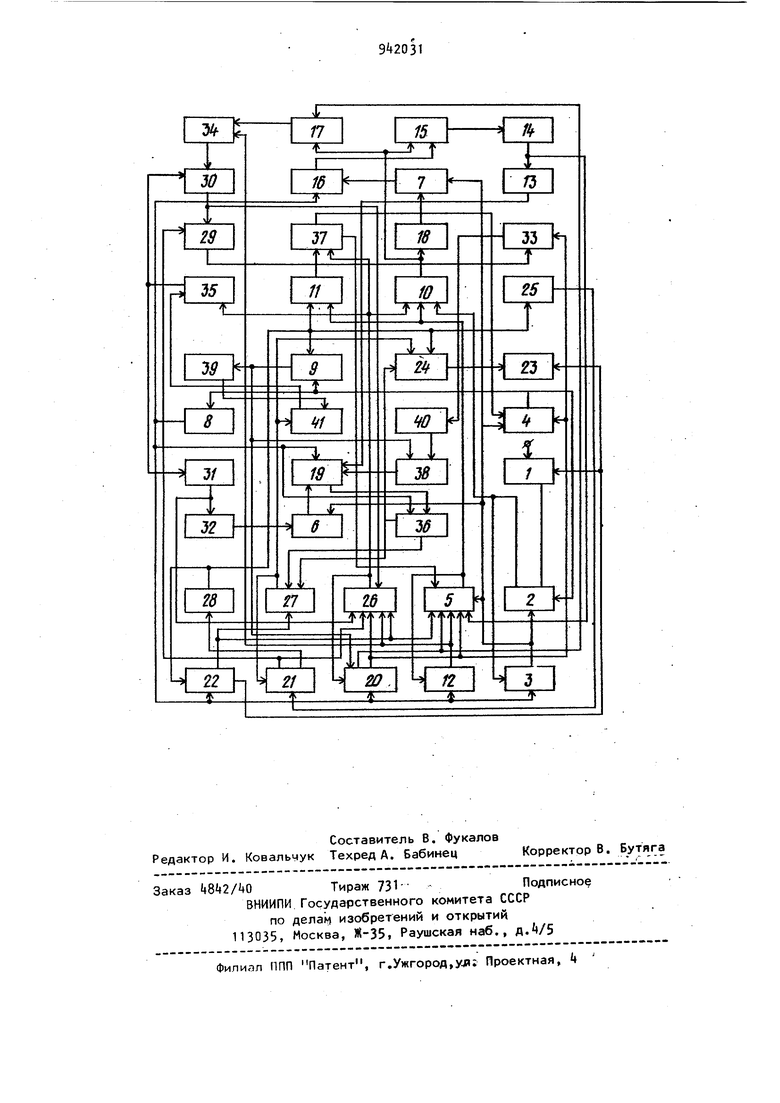

Кто ««t 4.-t где значения коэффициентов вычисляются на основе реккурентных соотношений. Это устройство содер20жит генератор импульсов, блок ввода, четыре блока памяти, блок умножения, блок сложения, блок регистрации, узел формирования первого импульса, семь элементов задержки, три счетчика, элемент НЕ, семь элементов И, три элемента ИЛИ, схему сравнения. Недостатком данного устройства является то, что оно позволяет вычислять коэффициенты полинома, заданного только в виде при этом с ростом п количество итераций значительно увеличивается, что ведет к увеличению времени решения задaчиv Кроме того, данное устройство как и предыдущее, в принципе не спо собно решать задачи определения (синтеза) вида регрессионных полино миальных моделей, которыми можно описать работу исследуемых сложных систем. Цель изобретения - увеличение бы родействия устройства при решении - задачи синтеза регрессионных моделей, При этом, устройство.обеспечивает синтез вида регрессивной модели из всего множества возможных в зависимости вида к э а. у S (2) j-1 J Поставленная цель достигается тем, что в устройство, содержащее генератор импульсов, четыре брока памяти, блок умножения, блок сложения, блок регистрации, три счетчика четыре элемента И, схему сравнения, введены три блока памяти, шесть схе сравнения, пять блоков сложения, блок вычитания, три блока возведения в степень, второй блок умножени два блока деления, два счетчика, блок регистров констант и блок триг геров, причем первый вход генератор импульсов является входом устройства, а выход генератора импульсов соединен со счетным входом первого счетчика, установочный вход которого подключен к выходу первой схемы сравнения и к первым входам блока триггеров, второго счетчика, первого и второго элементов И, выход блока триггеров соединен с входом блока регистров констант, управляю1ЦИМ входом блока памяти и управляющим входом первого счетчика, выход которого соединен с первым входом первой схемы сравнения и первым адресным входом второго блока памяти. Информационный вход которого подключен к первому адресному входу третьего блока памяти, первому входу второй схемы сравнения и выходу второго счетчика, второй счетный вход которого соединен с входом первого блока сложения и выходом первого блока возведения в степень, вход которого подключен к выходу блока вычитания, первый вход которого соединен с выходом первого блока деления, второй вход блока вычитания соединен с первым входом второго блока сложения, выходом второго блока памяти и входом третьего блока сложения, выход которого подключен ко второму входу второго элемента И, выход которого соединен с первым входом первого блока деления, второй вход которого подключен к выходу блока регистров констант, первым входам второго блока деления и вторым входам первой, второй, третьей, пятой и шестой схем сравнения, вход останова генератора импульсов соединен с первым выходом пятой схемы сравнения и управляющим входом блока регистрации, информационный вход которого подключен к выходу четвертого блока памяти, первый адресный вход которого соединен с входом пятого блока памяти, а также с адресным входом третьего блока памяти, вторым входом третьего блока памяти, вторым входом пятой схемы сравнения и выходом пятого счетчика, вход которого соединен с первым выходом четвертой схемы сравнения, второй выход которого подключен к первому установочному входу третьего счетчика и первому входу четвер того блока сложения, второй вход которого соединен с выходом первого блока умножения и первым счетным входом третьего счетчика, второй счетный вход которого подключен к выходу второго блока возведения в степень и входу пятого блока сложения, выход которого соединен со вторым входом второго элемента И, выход которого подключен к второму входу второго деления, второй установочный вход третьего счетчика соединен с первым выходом третьей схемы сравнения, первым входом третьего элемента И, вторым входом блока триггеров и первым установочным входом второго счетчика, третий счетный вход третьего счетчика соединен с выходом второй схемы сравнения, первым входом четвертого элемента И и вторым установочным входом второго счетчика,, третий установочный вход которого подключен ко второму выходу третьей схемы сравнения и втор му входу второго блока сложения, выход которого соединен со вторым входом четвертого элемента И, выход которого подключен к первому входу первого блока умножения, второй вхо которого соединен с выходом шестого блока памяти и входом второго блока возведения в степень, выход т тьего счетчика подключен к второму адресному входу второго блока памяти, первому входу седьмой схемы сра нения, второму входу третьей схемы сравнения и первому адресному входу шестого блока памяти, выход третьего блока памяти соединен с вторым входом седьмой схемы сравнения, пер вый выход которой подключен к треть ему счетному входу второго счетчика второй выход седьмой схемы сравнения соединен с третьим входом блока триггеров, второй выход пятой схемы сравнения подключен к четвертому установочному входу второго счетчика, третьему установочному входу третьего счетчика и первому установочному входу четвертого счетчика, первый счетный вход которого соединен с первым выходом шестой схемы сравнения, второй вход которо подключен к выходу второго блока де ления, третий вход которого соединен с выходом второго блока умножения, первый вход которого подключен к выходу первого блока памяти, адресному входу седьмого блока памяти и третьему входу третьей схемы сравнения, второй вход второго блок умножения соединен с выходом третье го блока возведения в степень, вход которого подключен к выходу третьег элемента И, второй вход третьего эл мента И соединен с выходом четвертого блока сложения, выход первого блока сложения подключен к четвертому входу второго блока деления, второй выход шестой схемы сравнения соединен с информационным входом четвертого блока памяти и вторым с четным входом четвертого счетчика, выход которого соединен с первыми входами четвертой схемы сравнения и шестого блока сложения, вторым адресным входом четвёртого блока памяти, второй вход четвертой схемы сравнения соединен с выходом пятого блока памяти.второй вход шестого блока сложения соединен с выходом седьмого блока памяти, а выход шестого блока сложения соединен со вторым адресным входом шестого блока памяти. Математическая постановка задачи. Пусть исследуется некоторая сложная система,.работа которой характеризуется некоторым показателем эффективности у, а состояния этой системы определяются некоторым множеством R независимых переменных (факторов) X |х:хе х ,. .. , Изучение работы данной сложной системы осуществляется путем постановки специального эксперимента по заранее спланированному плану Л(а..)Ц 11 а а к-( ма количество опытов эксперимента;1( - количество факторов: )- номер уровня варьиро вания, на котором устанавливается j-й фактор в i-ом опыте эксперимента; множество уровней варьирования J- о фактора;, количество уровней варьирования j-ro фактора. Результаты эксперимента, проведенного по плану А могут быть представлены в виде матрицы i 1 ,N Y(y. ) J 1 ,k N1 УМО где О. - количество повторения каждого опыта эксперимента; у - результат п-го повторения V i-ro опыта эксперимента. По результату Y эксперимента можо изучать физику работы исследуемой сложной системы и в случае описать ее работу L. виде регрессивной г эдели вида у f(x), (3) Однако определение самого вида функции распределения f(x) является сложной математической задачей, для решения которой не предложено хоро7ших универсальных алгоритмов. Обычно эта задача решается методом подбора (направленного или случайного) различных зависимостей. В частном случае зависимости могут быть полиномиального вида, этот вид зависимостей широко распространен. t Известно решение подобных задач на универсальных ЭВМ При этом, использование несовершенных алгоритмо основанных на различных методах перебора множества зависимостей до получения удовлетворительной зависи мости, не всегда приводит к положительному результату и требует больш затрат машинного времени, что не по воляет использовать ЭВМ для синтеза вида регрессионных моделей при обработке многомерной статистики в АСУ, работающих в реальном масштабе времени. В основу работы устройства полож следующий алгоритм синтеза регрессионных математических моделей поли номинального вида на основе многофакторного анализа результатов экспериментаДля каждого члена возможного полиноминального разложения ( 2) ищут )Сумму квадратов отклонений, соответ ствующую влиянию данного член li . 51 -яе г-илгЦ, k г - коэффициенты ортогональны 1 полиномов (их значения пр ведены в таблице); коэффициенты, определяемы условиями a,-j , , при ,1- - г г, - максимально возможная сте пень, которая может быть проверена для j-ro фактора; она определяется условием1 , при h; 2 (t).-l) .3 (() 8 Затем определяется оценка для дисперсии ошибки эксперимента ош--Д|,, -О где-y.-S |Q среднее значение 1 4-1 результатов 1-го о та эксперимента. Далее для каждой суммы квадратов О11слонений строится F-отношение Ч°% J r.. уГт.. которое сравнивается с критическим по условию Х- где FJ - критическое значение F-OTнouJeния, взятое при одной степени свободы числителя, Q(N-I) степеней свободы знаменателя и при уровне значимости о( . Если данное условие выполняется, то соответствующий член рносится в синтезируемый вид регрессивной полиномиальной модели. В противном случае - не вносится. На чертеже приведена функциональная схема устройства. Устройство содержит генератор 1 импульсов, первый счетчик 2, первая схема 3 сравнения, блок триггеров, второй счетчик 5, первый элемент И 6, второй элемент И 7, блок 8 регистров констант, первый блок 9 памяти, второй блок 10 памяти, третий блок 11 памяти, вторая схема 12 сравнения, первый блок 13 сложения, первый блок возведения в степень, блок 15 вычитания, первый блок 16 деления, второй блок 17 сложения, третий блок 18 сложения, второй блок 19 деления, третья схема 20 сравнения, четвертая схема 21 сравнения, пятая схема 22 сравнения, блок 23 регистрации, четвертый блок 24 памяти, пятый блок 25 памяти, третий счетчик 26, четвертый счетчик 27, пятый счетчик 28, четвертый блок 29 сложения, первый блок 30 умножения, второй блок 31 возведения 8 степень, пятый блок 32 сложения, третий элемент И 33 четвертый элемент И 3, шестой блок 35 памяти, шестая схема 36 сравнения, седьмая схема 37 сравнения, второй блок 38 умнохения, седьмой блок 39 памяти, третий блок возведения в степень и шестой блок 1 сложения. Блоки 10, 11, , 35 памяти представляют собой двухадресную память в виде матриц регистров. Блок 35 памяти содержит тридцать Две линейки по 10 регистров в каждой. Количество строк блоков 10, 11 памяти определяется максимальным количеством опытов в эксперименте (N), а блока 2k памяти - количеством факторов К. Количество столбцов блока 10 памяти определяется числом параллельных опытов (), блока 11 памяти - количес вом факторов К, блока 2k памяти равно 5. Блоки 9, 25, 39 памяти представляют собой одноадресную память, причем блоки 9, 25 памяти содер хат по К регистров, а блок 39 памяти - десять регистров. Cxef сравнения и элементы И выполнены на элементах И по числу раз дов чисел, причем схемы сравнения предназначены для сравнения двух чисел и выдачи соответствующих импу сов, а элементы И выполняют функции ключевых схем. Блок триггеров представляет собой набор триггеров, которые выполняют необходимые переключения. Блок 8 регистров констант представляет собой память на пяти регистрах. Блок 23 регистрации служит для сопряжения с аппаратурой АСУ, если информация используется в следующих устройствах или для отобр жения информации средствами индикации. Разрядность счетчика 28 определя ется максимально возможным количест вом факторов (k), разрядность счетчика 27 определяется максимальным показателем степени , третье го 28 и второго 5 счетчиков - количеством опытов N, а счетчика 2 - к личеством повторения опытов Q. Устройство работает следующим образом. Перед началом работы устройство приводится в исходное состояние, а именно: в блок 35 памяти заносят коэффициенты ортогональных полиномов, причем в z-ой строки (см. таблицу) в каждый г-й регистр линейки г-й элемент строки. В блок 11 памяти заносится план эксперимента А, прич в каждый j-й регистр i-ой строки заносится элемент матрицы А. В блок 10 памяти заносятся.результаты эксперимента, причем в «у-й регистр i-ой строки заносится элемент матрицы Y. В каждый j-й регистр блока 9 памяти заноЬи.тся величина hj , равная количеству уров ней варьирования j-ro фактора в пла не эксперимента. В (З-Ю) регистры 110 блока 39 памяти заносятся базовые адреса |l, 3, 6, 10, , 18, 23, 28. В каждый j-й регистр блока 25 памяти заносится максимальное значение Tj. для возможной степени j-ro фактора в синтезируемом полиноме. Все регистры блока 2k памяти обнуляются. Счетчики 5, 20, 27 и 28 устанавливаются в единицу, а счетчик 2 - в ноль. Сумматоры первого 13 второго 17, третьего 18, четвертого 29 и пятого 32 блоков сложения обнуляются. С помощью блока k триггеров коммутации пятая схема 22 сравнения подключается к.выходу третьего регистра, третья схема сравнения 20 к выходу первого регистра, вторая 12 и первая 3 схемы сравнения к выходу второго регистра блока 8 регистров констант. В блок 8 регистров констант заносится информация: в первый регистр - количество опытов (N) эксперимента; во второй регистр - количество параллельных опытов (Q,) эксперимента ; в третий регистр - количество факторов (k) эксперимента; в четвертый регистр - критическое значение (Рд);Q в пятый регистр - константа -QTi По сигналу Пуск запускается генератор 1 импульсов, первый импульс с которого поступает в счетчик 2 и устанавливает его в единит цу. Из второго блока 10 памяти по адресу, определяемому содержимым третьего 26 (выбор строки матрицу) и первого 2 (выбор столбца матрицы) счетчиков считывается число, которое поступает в третий блок 18 сложения и прибавляется к содержимому его сумматора. Очередной импульс с генератора 1 импульсов увеличивает содержимое счетчика 2 на единицу, и в блок 18 сложения поступает очередное число из блока 10 памяти. Как только содержимое счетчика 2 превысит значение (1, сигналом с выхода первой схемы сравнения 3 устанавливается в ноль первый счетчик 2, и разрешается перезапись содержимого сумматора третьего бло-. ка 18 сложения через вторую схему 7 совладения и в первый блок 1б деления., где поступившее числоделится на содержимое второго регистра блока 8 регистров констант, и далее резуль тат поступает в блок 15 вычитания) где вычитается из числа поступивше го из второго блока 10 памяти по адресу, определяемому содержимым третьего 26( выбор строки матрицы) и второго 5 вь|бор столбца матрицы счетчиков. Результат вычитания в первом блоке 1 возведения в степен возводится в квадрат и поступает в первый блок 13 сложения, где суммируется с содержимым сумматора. Одновременно стробирующий импульс с первого блока 14 возведения в сте пень поступает во второй счетчик 5 и увеличивает его содержимое на еди ницу. После этого все описанные опе рации повторяются до тех пор, пока содержимое второго счетчика 5 не превысит значения Q. При этом сигналом с выхода второй схемы 12 сравнения добавляется единица к содержимому третьего счетчика 2б и все описанные операции повторяются до тех пор, пока содержимое третьего счетчика 2б не превысит значение N. При этом сигнал с выхода третьей схемы 20 сравнения устанавливает третий 2б и второй 5 счетчики в единицу и одновременно rtecTyпает в блок 4 триггеров коммутации который обеспечивает отключение третьей 20 и второй 12 схем сравнения от соответствующих регистров блока 8 регистров констант, счет гчика 2 от генератора 1 импульсов и подключает третью схему сравнения 20 к выходу первого блока памяти 9 вторую схему 12 сравнения к выходу первого регистра блока 8 регистров констант. После этого из третьего блока 11 памяти считывается число, которое поступает в схему 37 сравнения,где сравнивается с содержимым третьего счетчика 2б. Если сравнения не прои зошло, то сигналом с выхода схемы 37 сравнения к содержимому счетчика 5 добавляется единица и происходит считывание очередного числа из третьего блока 11 памяти-. В случае, если содержимое ячейки блока 11 памяти и третьего счетчика 2б совпадают, то сигнал с другого выхода схемы 37 сравнения поступает в блок Ц триггеров коммутации, который обеспечивает подключение выхода ге1нератора 1 импульсов ко входу счетчика 2. С поступлением первого им- пульса на счетчик 2 из второго блока 10 памяти по адресу, определяемо-му содержимым второго 5 ( выбор строки матрицы) и первого 2 (выбор столбца матрицы) счетчиков, считывается число, которое поступает в блок 17 сложения и суммируется с содержимым сумматора. Как только содержимое счетчика 2 превысит значение Q, сигнал с выхода первой схемы 3 сравнения поступает в блок 4 триггеров коммутации, который отключает генератор 1 импульсов от входа счетчика 2, далее в счетчик 2, устанавливая его в ноль, и в счетчик 5, добавляя к его содержимому единицу. При этом из блока 11 памяти считывается очередное число, и описанные операции повторяются, пока содержимое счетчика 5 не превысит значения N. В этом случае сигнал с выхода второй схемы 12 сравнения поступает на вход четвертой схемы 3 совпадения и разрешает перезапись содержимого сумматора второго блока 17 сложения на вход первого блока 30 умножения, на второй вход которого поступает коэффициент из блока 35 памяти по адресу, определяемому содержимым третьего 26, четвертого 27 и пятого 28 счетчиков. Причем, содержимое пятого счетчика 28 поступает в первый блок 9 памяти, содержимое соответствующей ячейки которого поступает в седьмой блок 39 памяти и служит адресом считывания базового адреса из блока 39 памяти, который поступает в шестой блок 41 сложения, где складывается с содержимым четвертого счетчика 27, и результат сложения поступает на адресный вход шестого блока 35 памяти и служит для выбора линейки регистров, а содержимое третьего счетчика 26 служит для выбора соответствующего регистра в линейке регистров блока 35 памяти. Результат перемножения из первого блока 30 умножения поступает в блок 29 сложения, где добавляется к содержимому сумматора. Одновременно стробирующий импульс с первого блока 30 умножения поступает на вход третьего счетчика 2б и добавляет к его содержимому единицу. Если содержимое третьего счетчика 26 не превышает содержимого регистра первого блока 9 памяти (адрес регистра выбирается по содер жимому пятого счетчика 28), то сигналом с выхода третьей схемы 20 сравнения счетчик 5 устанавливается в единицу, а сумматор второго блока 17 сложения обнуляется, после чего из блока 11 памяти считывается очередное число, и описанные операции повторяются. Как только содержимое третьего счетчика 2б пр.евысит содержимое соответствующего регистра первого блока 9 памяти, сигнал со второго выхода третьей схемы 20 сравнения поступает на вход трет его счетчика 26 и устанавливает его в единицу и на вход третьей схемы 33 совпадения и разрешает перезапись содержимого сумматора четвертого блока 29 сложения в третий блок 40 возведения в степень, где число возводится в квадрат, после чего поступает на вход второго блока 38 умножения, на другой вход которого поступает число из первого блока 9 памяти. I Результат умножения с выхода вто рого блока 33 умножения поступает на вход второго блока 19 деления, где делится вначале на содержимое первого, затем пятого регистров бло ка 8 регистров констант, а затем результат делится на содержимое сум матора первого блока 13 сложения. Одновременно во втором блоке 31 возведения в степень возводится в квадрат коэффициент, поступивший из блока 35 памяти,после чего в пятом блоке 32 сложения добавляется к содержимому сумматора, а стробирующий импульс с второго блока 31 возведения в степень поступает на вход третьего счетчика 26 и добавляет к его содержимому единицу. После этого из блока 35 памяти считывается очередной коэффициент. Как только содержимое третьего счетчика 26 пре высит содержимое соответствующего регистра первого блока 9 памяти, сигналом с выхода третьей схемы 20 сравнения третий счетчик 26 устанавливается в единицу и разрешается перезапись содержимого сумматора пятого блока 32 сложения через первую схему 6 совпадения на вход второго блока 19 деления (содержимое сумматора пятого блока сложения после этого обнуляется). 8о втором блоке 19 деления на поступившее число делится ранее полученный . результат деления, и конечный результат поступает в шестую схему 20 сравнения, где сравнивается с критическим значением FQ/. Если поступившее число больше критического значения F(, то сигналом с выхода шестой схемы 20 сравнения в регистр, определяемый содержимым четвертого 27 и пятого 28 счетчиков, четвертого блока 2 памяти заносится единица, и добавляется единица к содержимому счетчика 27. В противном случае сигналом с другого выхода шестой схемы Зб сравнения единица поступает только на счетчик 27. В случае, если содержимое четвертого счетчика 27 не больше содержимого соответствующего регистра пятого блока 25 памяти, то сигналом с выхода четвертой схемы 21 сравнения третий счетчик 2б устанавливается в единицу и обну-. ляется сумматор четвертого блока 29 сложения, после чего из третьего блока 11 памяти считывается очередное число и повторяются описанные выше операции. Как только содержимое счетчика 27 превысит содержимое соответствующего регистра пятого блока 25 памяти, сигналом с другого выхода четвертой схемы 21 сравнения добавляется единица к содержимому счетчика 28. Если содержимое счетчика 28 не превышает содержимого третьего регистра блока 8 регистров констант, то сигналом с выхода схемы 22 сравнения второй 5, третий 6 и четвертый 27 счетмики устанавливаются в единицу, из блока 11 пгмяти считывается очередное число и повторяются вышеописанные операции. Если содержимое счетчика 28 превысит содержимое третьего регистра блока 8 регистров констант, то сигналом с другого выхода схемы 22 сравнения разрешается выдача содержимого блока 2k памяти в блок 21; регистрации, происходит прекращение работы генератора 1 импульсов и останов устройства. I ., Бхюк 23 регистрации выдает содержимое блока 2 памяти в виде двумерной матрицы 1J если коэффицент aj чительно отличен от нул О, если коэффициент а,.близок к нулю. Используя данную матрицу, мож записать вид регрессионной полин миальной модели. Пример. Пусть по резу там дисперсного анализа +-фактор го эксперимента матрица J имеет 10110 00011 00000 01001 В этом случае регрессионная модель имеет вид У ,,, л Л- Q Vji 14 i5 2. V VlОценка технико-экономического эффекта от использования изобретения проведена теоретически и м тодом математического моделирова

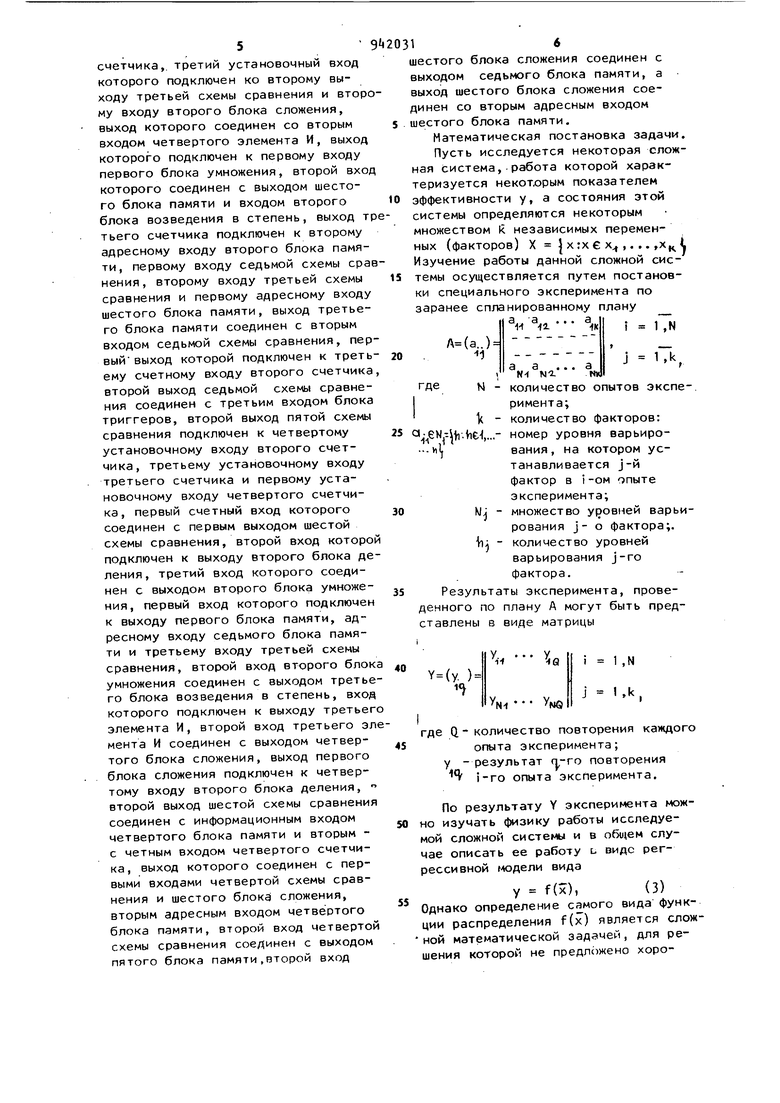

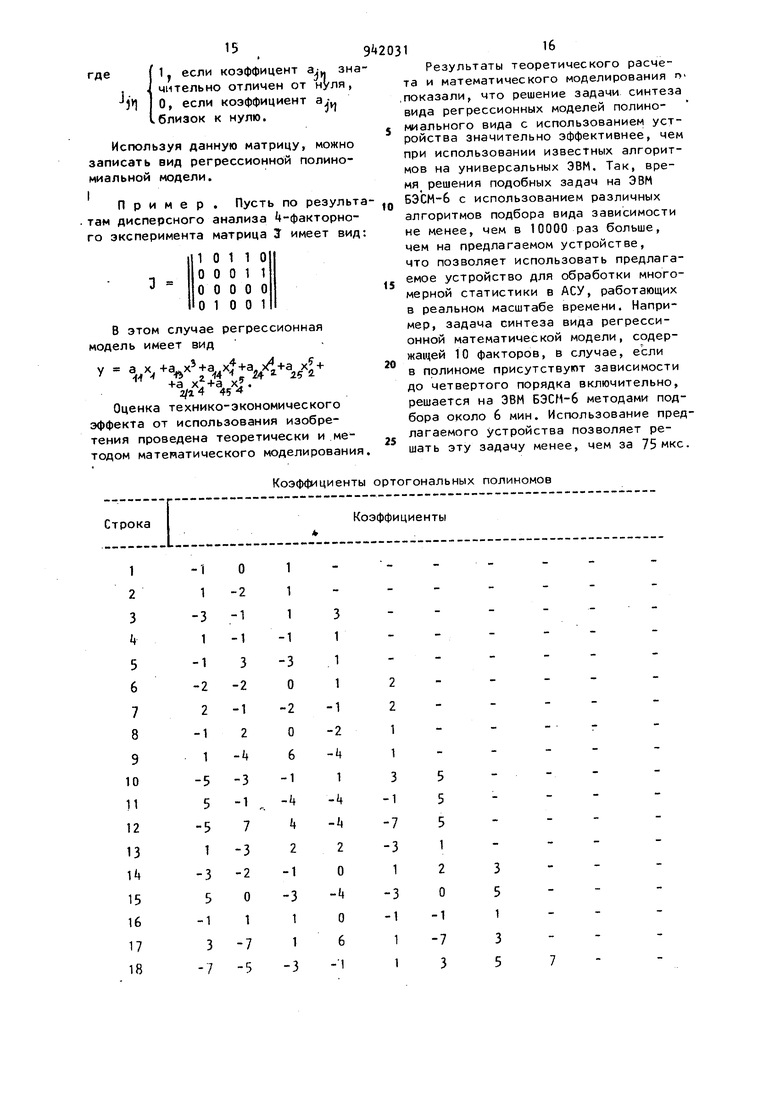

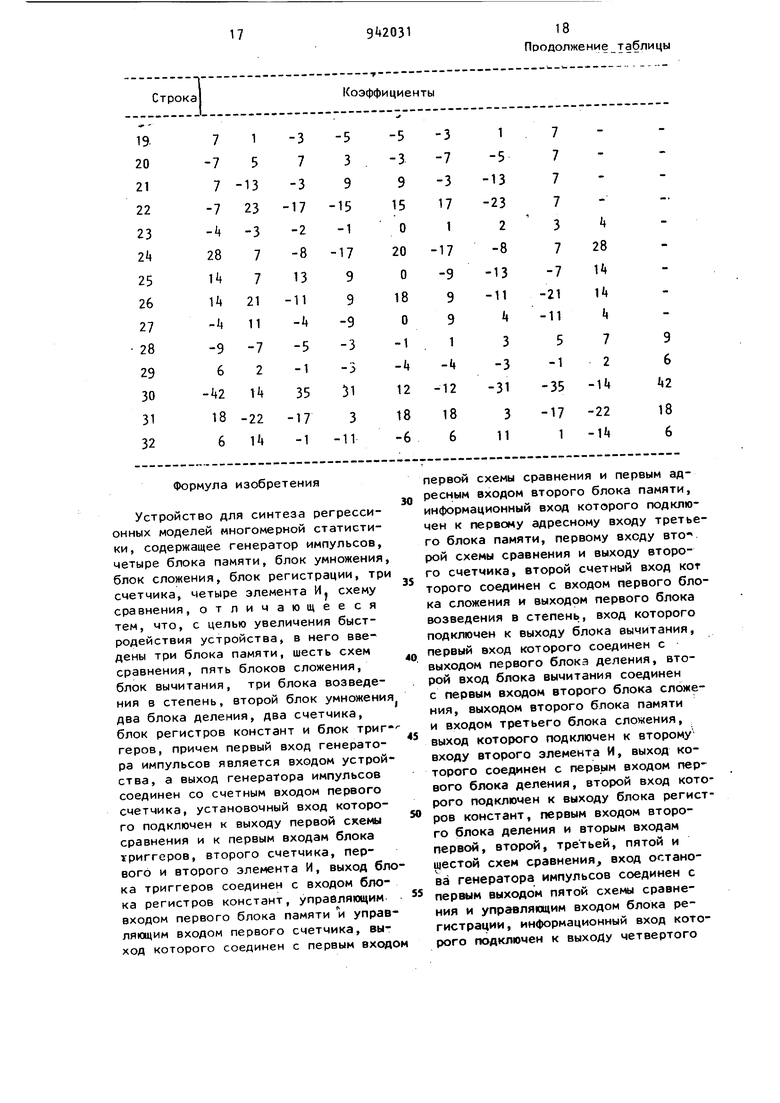

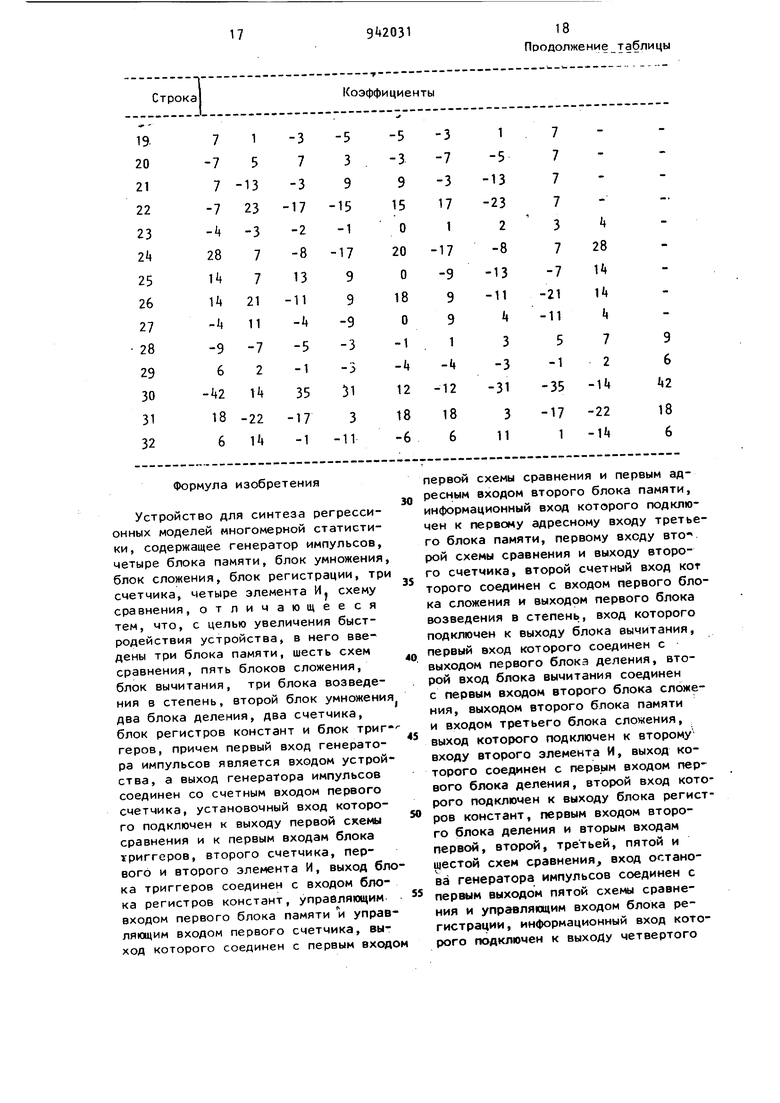

Коэффициенты ортогональных полиномов 116 Результаты теоретического расчета и математического моделирования опоказали, что решение задачи синтеза вида регрессионных моделей полиномиального вида с использованием устройства значительно эффективнее, чем при использовании известных алгоритмов на универсальных ЭВМ. Так, время решения подобных задач на ЭВМ БЭСМ-6 с использованием различных алгоритмов подбора вида зависимости не менее, чем в 10000 раз больше, чем на предлагаемом устройстве, что позволяет использовать предлагаемое устройство для обработки многомерной статистики в АСУ, работающих в реальном масштабе времени. Например, задача синтеза вида регрессионной математической модели, содержащей 10 факторов, в случае, если в полиноме присутствуют зависимости до четвертого порядка включительно, решается на ЭВМ БЭСМ-6 методами подбора около 6 мин. Использование предлагаемого устройства позволяет peшать эту задачу менее, чем за 75мкс.

17

942031

18 Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций в модулярной системе счисления | 1985 |

|

SU1291977A1 |

| Устройство для вычисления коэффициентов полинома | 1983 |

|

SU1130876A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Цифровой измеритель задержки | 1981 |

|

SU951228A1 |

| Устройство для возведения в п-ую степень | 1982 |

|

SU1132287A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство подготовки данных для машин управления процессами электронно-лучевой микрообработки | 1983 |

|

SU1154257A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Устройство для вычисления функции обученности человека-оператора | 1988 |

|

SU1553991A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

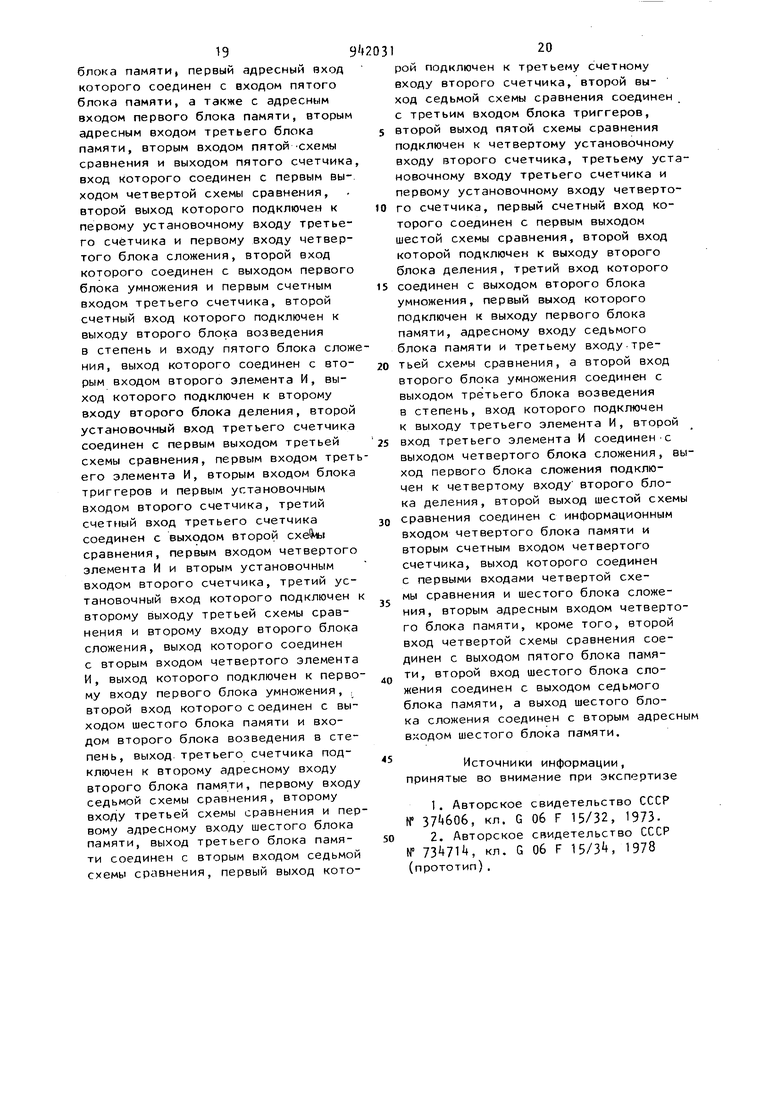

Формула изобретения Устройство для синтеза регрессионных моделей многомерной статистики, содержащее генератор импульсов, четыре блока памяти, блок умножения блок сложения, блок регистрации, тр счетчика, четыре элемента Hj схему сравнения, отличающееся тем, что, с целью увеличения быстродействия устройства, в него введены три блока памяти, шесть схем сравнения, пять блоков сложения, блок вычитания, три блока возведения в степень, второй блок умножени два блока деления, два счетчика, блок регистров констант и блок триг геров, причем первый вход генератора импульсов является входом устрой ства, а выход генератора импульсов соединен со счетным входом первого счетчика, установочный вход которого подключен к выходу первой скемы сравнения и к первым входам блока г-риггеров, второго счетчика, первого и второго элемента И, выход бл ка триггеров соединен с входом блока регистров констант, управляющим входом первого блока памяти и управ ляющим входом первого счетчика, выход которого соединен с первым вход первой схемы сравнения и первым адресным входом второго блока памяти, информационный вход которого подключен к первому адресному входу третьего блока памяти, первому входу вто- рой схемы сравнения и выходу второго счетчика, второй счетный вход кот торого соединен с входом первого блока сложения и выходом первого блока возведения в степень, вход которого подключен к выходу блока вычитания, первый вход которого соединен с выходом первого блока деления, второй вход блока вычитания соединен с первым входом второго блока сложения, выходом второго блока памяти и входом третьего блока сложения, выход которого подключен к второму входу второго элемента И, выход которого соединен с первым входом первого блока деления, второй вход которого подключен к выходу блока регистров констант, первым входом второго блока деления и вторым входам первой, второй, третьей, пятой и цестой схем сравнения, вход останова генератора импульсов соединен с першам выходом пятой схемы сравнения и управляющим входом блока регистрации , информационный вход которого подключен к выходу четвертого 19 блока памяти, первый адресныГ1 вход которого соединен с входом пятого блока памяти, а также с адресным входом первого блока памяти, вторым адресным входом третьего блока памяти, вторым входом пятой Схемы сравнения и выходом пятого счетчика вход которого соединен с первым выходом четвертой схемы сравнения, второй выход которого подключен к первому установочному входу третьего счётчика и первому входу четвертого блока сложения, второй вход которого соединен с выходом первого блока умножения и первым счетным входом третьего счетчика, второй счетный вход которого подключен к выходу второго блока возведения в степень и входу пятого блока слож ния, выход которого соединен с вторым входом второго элемента И, выход которого подключен к второму входу второго блока деления, второй установочный вход третьего счетчика соединен с первым выходом третьей схемы сравнения, первым входом трет его элемента И, вторым входом блока триггеров и первым установочным входом второго счетчика, третий счетный вход третьего счетчика соединен с выходом второй схе()мы сравнения, первым входом четвертого элемента И и вторым установочным входом второго счетчика, третий установочный вход которого подключен второму выходу третьей схемы сравнения и второму входу второго блока сложения, выход которого соединен с вторым входом четвертого элемента И, выход которого подключен к перво му входу первого блока умножения, , второй вход которого соединен с выходом шестого блока памяти и входом второго блока возведения в степень, выход третьего счетчика подключен к второму адресному входу второго блока памяти, первому входу седьмой схемы сравнения, второму входу третьей схемы сравнения и пер вому адресному входу шестого блока памяти, выход третьего блока памяти соединен с вторым входом седьмой схемы сравнения, первый выход кото20рой подключен к третьему счетному входу второго счетчика, второй выход седьмой схемы сравнения соединен с третьим входом блока триггеров, второй выход пятой схемы сравнения подключен к четвертому установочному входу второго счетчика, третьему установочному входу третьего счетчика и первому установочному входу четвертого счетчика, первый счетный вход которого соединен с первым выходом шестой схемы сравнения, второй вход которой подключен к выходу второго блока деления, третий вход которого соединен с выходом второго блока умножения, первый выход которого подключен к выходу первого блока памяти, адресному входу седьмого блока памяти и третьему входу-третьей схемы сравнения, а второй вход второго блока умножения соединен с выходом третьего блока возведения в степень, вход которого подключен к выходу третьего элемента И, второй вход третьего элемента И соединение выходом четвертого блока сложения, выход первого блока сложения подключен к четвертому входу второго блока деления, второй выход шестой схемы сравнения соединен с информационным входом четвертого блока памяти и вторым счетным входом четвертого счетчика, выход которого соединен с первыми входами четвертой схемы сравнения и шестого блока сложения, вторым адресным входом четвертого блока памяти, кроме того, второй вход четвертой схемы сравнения соединен с выходом пятого блока памяти, второй вход шестого блока сложения соединен с выходом седьмого блока памяти, а выход шестого блока сложения соединен с вторым адресным входом шестого блока памяти. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № , кл. G 06 F 15/32, 19732.Авторское свидетельство СССР № , кл. G Об F 15/34, 1978 (прототип).

Авторы

Даты

1982-07-07—Публикация

1980-11-26—Подача