Предполагаемое изобретение относится к области вычислительной техники и может найти применение в конвейерных потоковых машинах и многопроцессорных вычислительных системах.

Известно устройство доступа к памяти в процессоре ADSP-TS203S (см. http://www.analog.com/static/imported-files/data_sheets/ADSP-TS203S.pdf). Система обращения к памяти, принятая для архитектуры процессора ADSP-TS203S, содержит два адресных генератора, состоящих из целочисленных АЛУ и регистровых файлов; логику статического предсказания переходов, буфер адресов переходов и внутреннюю память DRAM. АЛУ используются для адресации данных, вычисления значений указателей, а также для выполнения простых вычислительных операций с целыми числами. Внутренняя память DRAM разбита на 4 независимых блока, предназначенных для хранения как инструкций, так и данных. Каждый блок внутренней памяти имеет собственный кэш. Имеется выход на контроллер внешней памяти SDRAM. Устройство доступа к памяти позволяет осуществлять сложные процедуры обращения как к внутренней, так и к внешней памяти.

Недостатком данного устройства является то, что оно не может быть использовано самостоятельно (без дополнительных средств) для организации доступа к памяти.

Причина недостатка состоит в том, что устройство доступа к памяти является составной частью процессора ADSP-TS203S.

Наиболее близким к предполагаемому изобретению является мультиконтроллер распределенной памяти (патент на изобретение №2210804) содержащий память программ, устройство управления, регистр операторов, счетчик условий, счетчик возврата, два регистровых файла начальных адресов и адресных приращений. В состав прототипа также входят сумматоры текущего адреса, адреса пороговой адресации и модифицируемых полей оператора, а также ортогональная регистровая память и вспомогательные мультиплексоры и счетчики.

Данное устройство позволяет обеспечивать автономный произвольный доступ к памяти по нескольким параллельным каналам без использования дополнительных ресурсов, в том числе, процессора. Порядок доступа к памяти строго регламентирован. Он описывается программой, хранящейся в памяти программ устройства и не требует механизма запросов от процессора. Поддерживается процедура изменения адресов каналов, заключающаяся в увеличении (уменьшении) адреса по каждому каналу на некоторый адресный параметр (приращение), а также более сложная процедура пороговой адресации. Кроме того, имеется возможность для модификации начальных адресов доступа и адресных приращений, а также средства для организации вложенных циклов, что позволяет организовывать сложные процедуры обращения к памяти.

Заявляемое устройство является результатом модификации описанного выше мультиконтроллера распределенной памяти с целью расширения возможностей программирования и повышения быстродействия. Рассмотрим преимущества заявляемого устройства перед своим прототипом.

В прототипе константа цикла указывается непосредственно в поле оператора, то есть используется непосредственная адресация. Число значений операндов при этом ограничивается разрядностью поля. В заявляемом устройстве используется прямая адресация, когда в соответствующем поле оператора указывается полный адрес константы цикла. Это дает возможность увеличить разрядность данного операнда. Кроме того, расширяются возможности программирования, так как значение параметра может изменяться при неизменной исполняемой программе.

В прототипе операторы и их параметры, такие как начальный адрес и адресное приращение, хранятся в одной памяти программ параметров. В заявляемом устройстве используется три независимых блока памяти для операторов, параметров адресации и констант цикла соответственно. Каждый блок памяти реализован в виде двухпортовой статической памяти. Такое решение обеспечивает более быстрый доступ к требуемым операндам.

В заявляемом устройстве счетчик возврата, используемый в прототипе, был заменен на стек глубиной 64 слова. Это позволяет организовывать подпрограммы большей вложенности.

В заявляемом устройстве было добавлено четыре регистра общего назначения.

Были расширены возможности пересчета полей операторов и параметров. В прототипе для модификации полей оператора использовалась только операция сложения. В заявляемом устройстве добавлены операции обнуления и замещения полей оператора. В прототипе для пересчета параметров оператора были доступны операции сложения и перемещения. В заявляемом устройстве были добавлены операции вычитания, умножения и деления параметров, а также существенно увеличен список операторов перемещения параметров между блоками памяти напрямую и между регистрами.

Был добавлен регистр сегмента для осуществления сегментной адресации памяти.

Задача на решение которой направлено заявляемое изобретение, заключается в расширении функциональных возможностей, обеспечении автономного произвольного доступа к памяти без использования дополнительных ресурсов, в том числе, процессора.

Технический результат, достигаемый при осуществлении изобретения, состоит в том, что расширение функциональных возможностей достигается за счет более сложной организации внутренней памяти, а именно, в разделении ее на три независимых блока, перехода от непосредственной к прямой адресации для константы цикла, перехода от счетчика возврата к стеку адресов возврата, использования в изобретении арифметико-логического устройства для выполнения арифметических действий над параметрами операторов, а именно, сложения, вычитания, умножения и деления, добавления быстродействующих регистров общего назначения, оптимизации связей между различными блоками изобретения для более рационального перемещения параметров, расширения системы команд.

Для достижения указанного технического результата заявляемое устройство содержит устройство управления, блок памяти операторов, блок памяти параметров, блок памяти циклов, блок основного мультиплексора, устройство арифметическое, процессор адресный, причем вход управляющего сигнала устройства соединен с первым входом устройства управления, двунаправленный вывод которого соединен с двунаправленными выводами блоков памяти операторов, памяти параметров, памяти циклов, процессора адресного, устройства арифметического и блока основного мультиплексора, выход которого соединен с первыми входами блоков памяти операторов, памяти параметров, памяти циклов и процессора адресного, второй вход которого соединен с первым входом устройства арифметического и с первым выходом блока памяти параметров, второй выход которого соединен с третьим входом процессора адресного, вторым входом устройства арифметического, первым входом блока основного мультиплексора и вторым входом блока памяти оператора, первый выход которого разрядами поля V1 связан соответственно с второго по шестой входами устройства управления, разрядами полей V2, V3 с вторым входом блока памяти параметров и разрядами полей V2, V3, V4 с вторым входом блока памяти циклов, третий вход которого соединен с третьим входом блока памяти параметров и выходом устройства арифметического, четвертый вход процессора адресного соединен с первым выходом блока памяти циклов, второй выход которого соединен с третьим входом устройства арифметического, четвертый вход которого соединен с третьим выходом блока памяти циклов и вторым входом блока основного мультиплексора, третий вход которого соединен с вторым выходом блока памяти операторов, с первого по четвертый выходы процессора адресного соединены соответственно с четвертого по седьмой входами блока основного мультиплексора, второй выход устройства управления соединен с первым выходом устройства, с второго по восьмой входы которого соединены соответственно с пятого по одиннадцатый входами процессора адресного, с пятого по одиннадцатый выходы которого соединены соответственно с второго по восьмой выходами устройства.

Причинно-следственная связь между совокупностью существенных признаков заявляемого изобретения и достигаемым техническим результатом заключается в следующем: введение в устройство прямой адресации константы цикла, переход от регистра возврата к стеку, добавление регистров общего назначения, добавление арифметико-логического устройства для модификации параметров и добавление новых операторов расширяют возможности программирования. Добавление трех независимых блоков памяти для операторов, параметров адресации и констант цикла, а также оптимизация связей между отдельными блоками позволяет реализовать процедуру обращения к памяти на более высокой тактовой частоте по сравнению с прототипом.

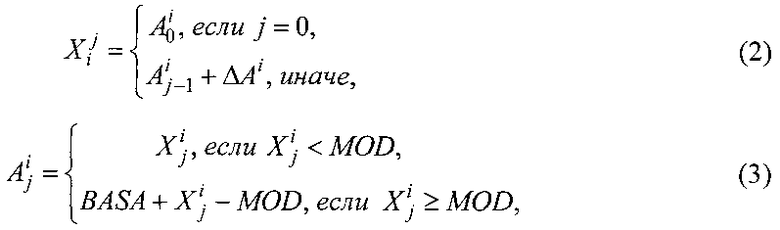

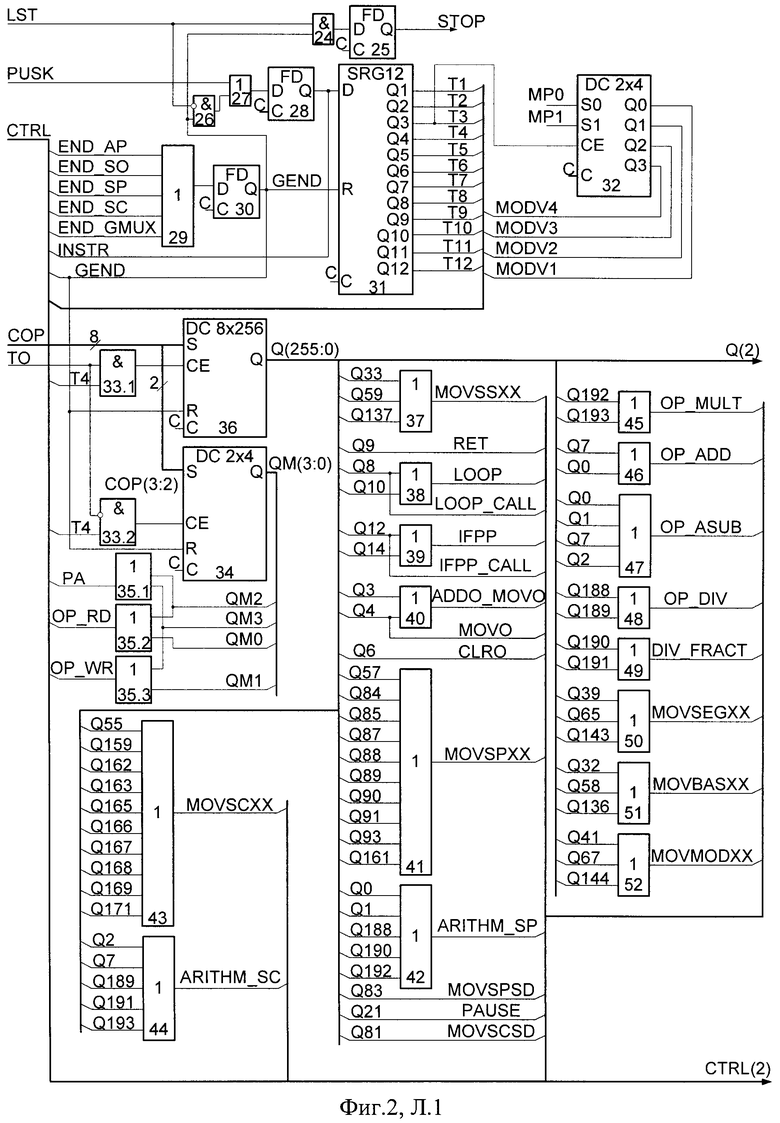

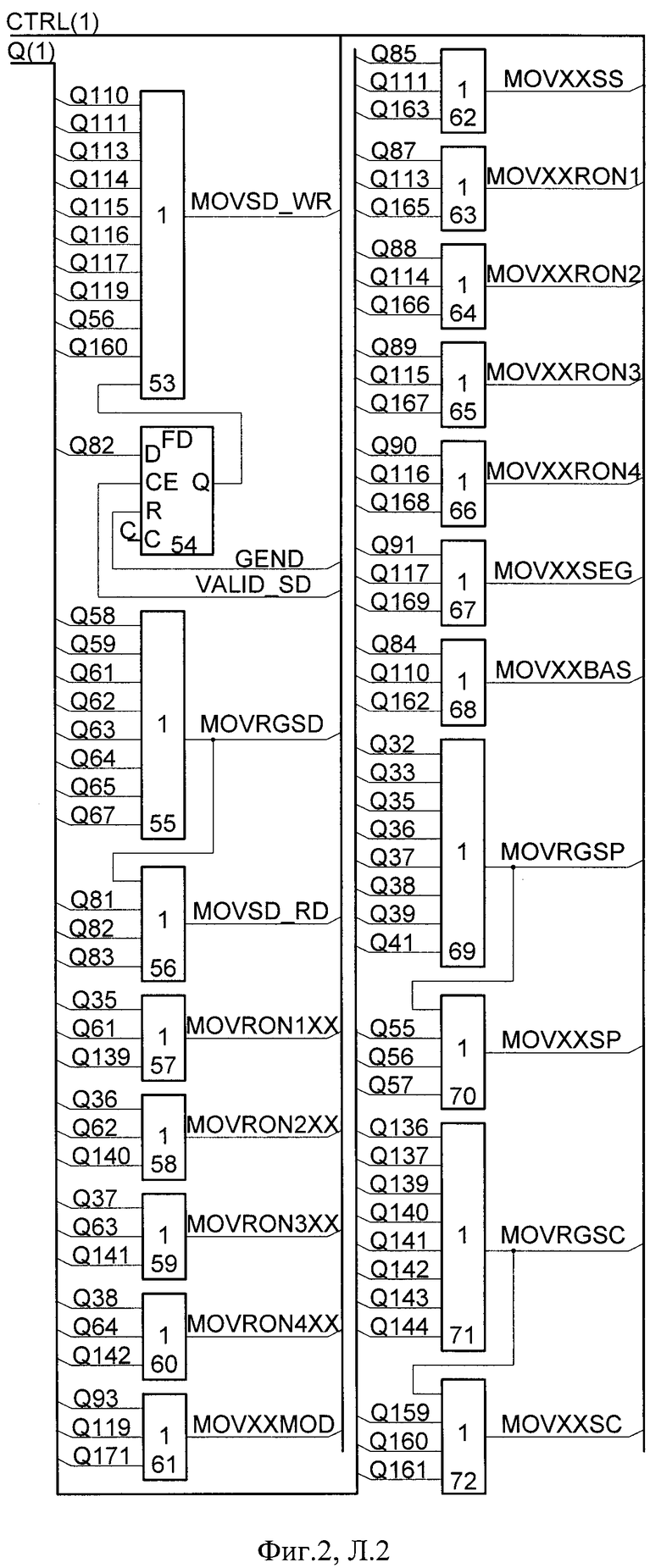

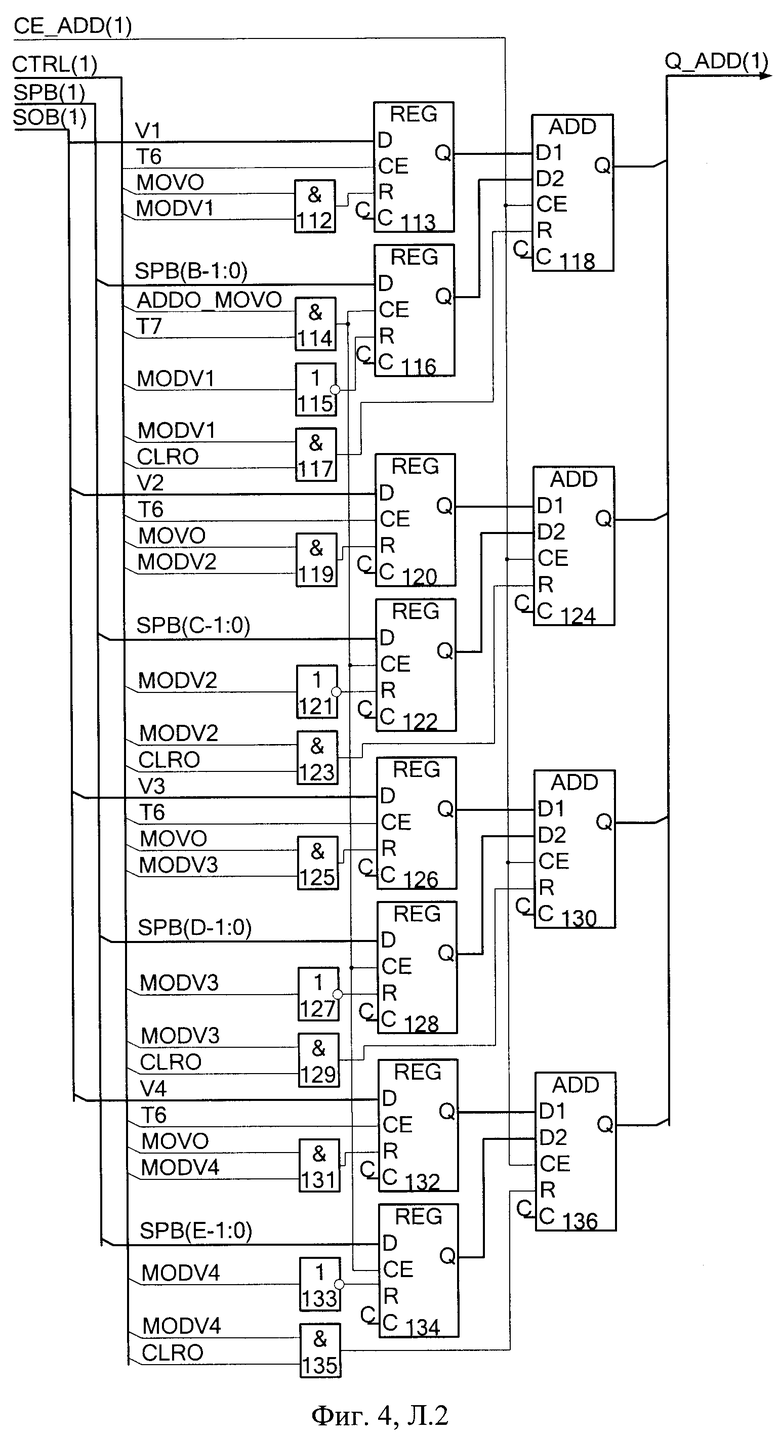

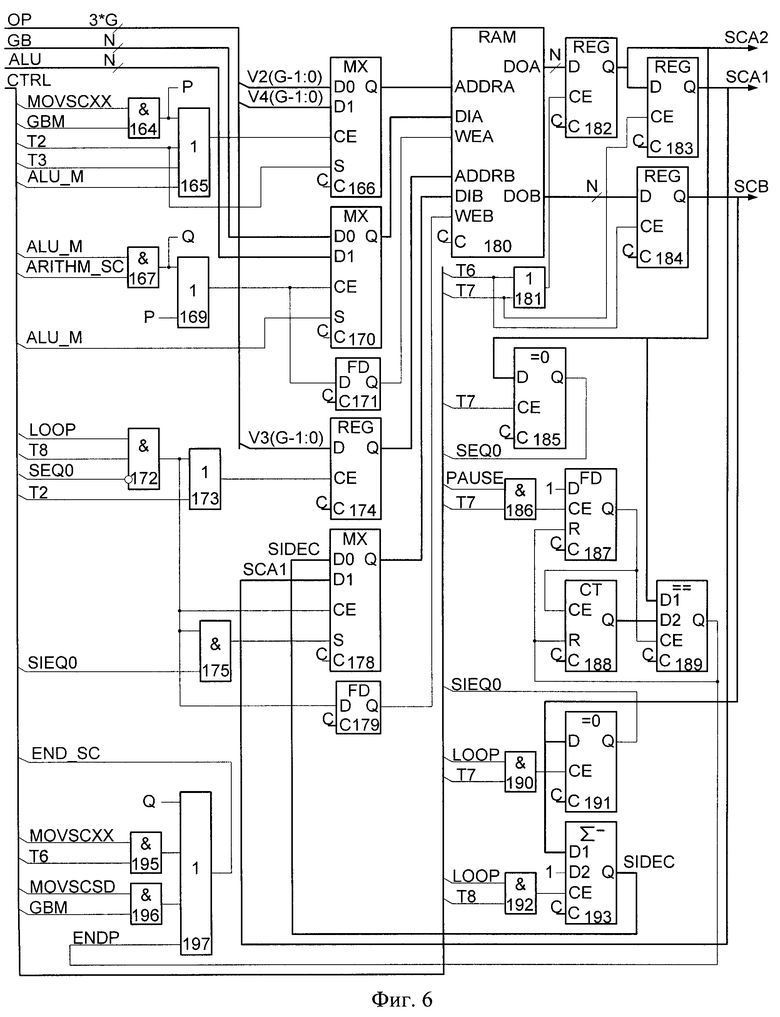

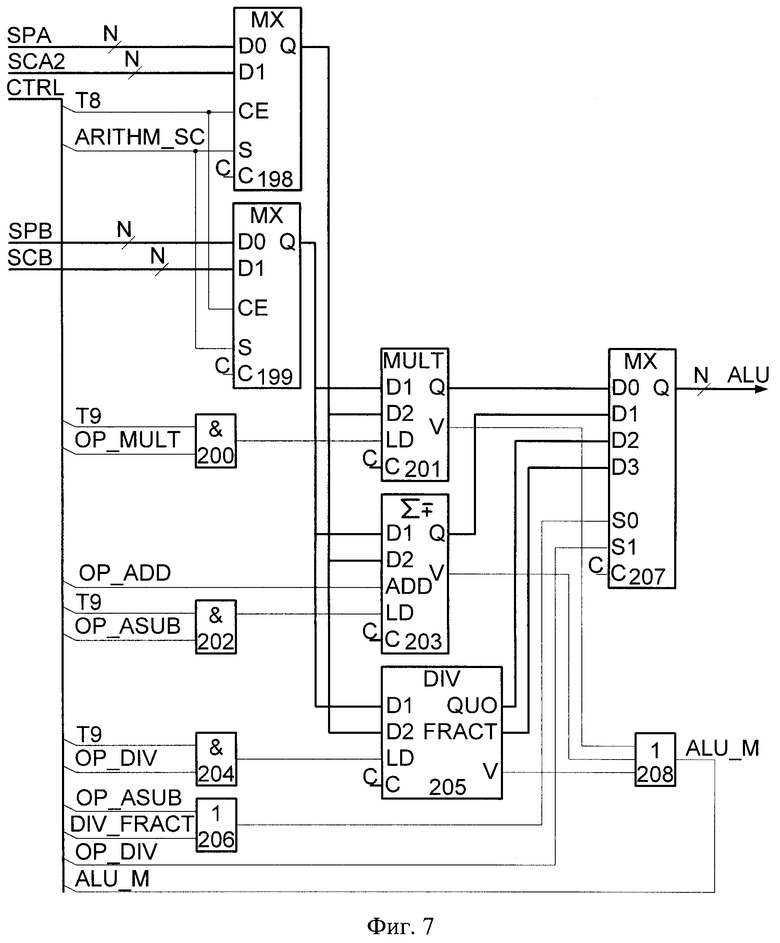

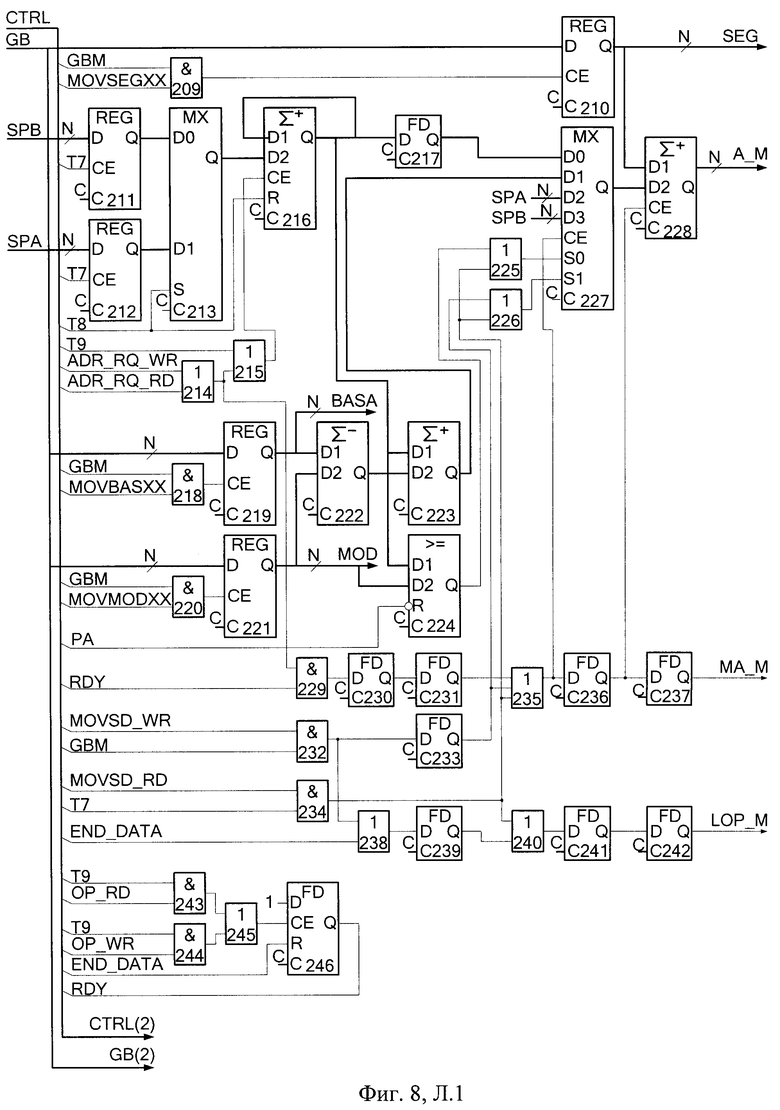

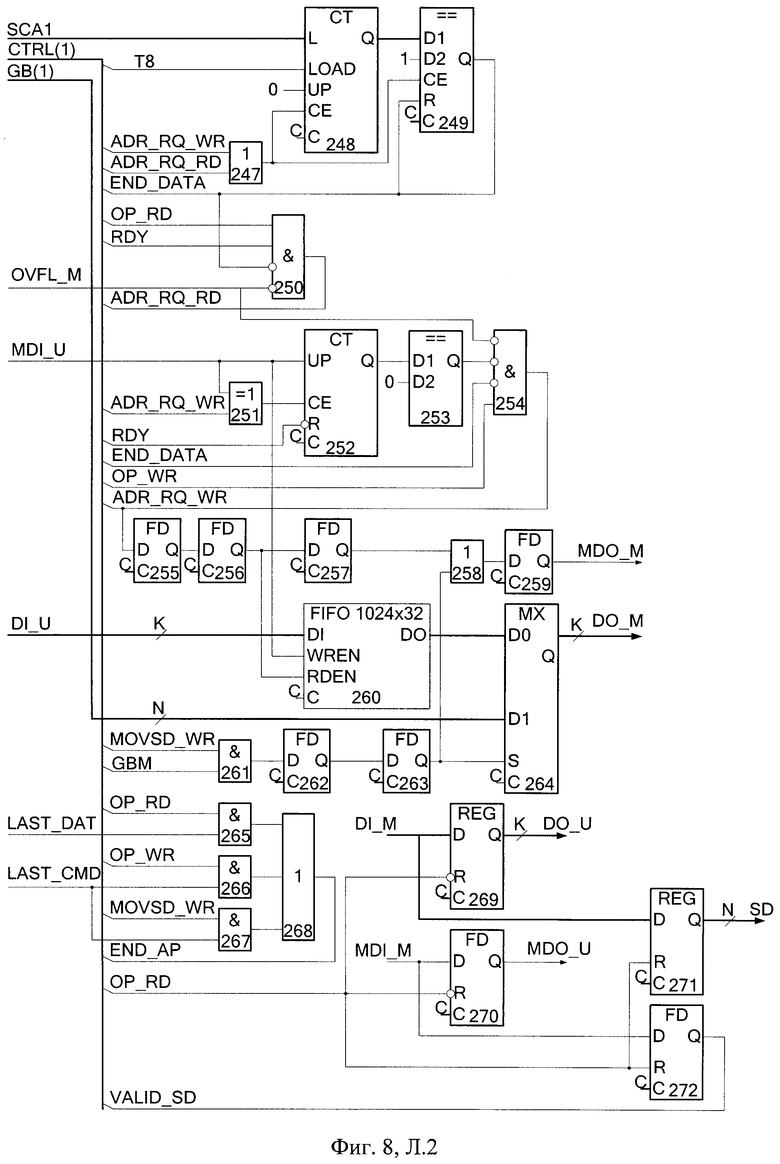

Изобретение поясняется чертежами, где на фиг. 1 представлена схема устройства мультиконтроллер распределяемой памяти (DMC), на фиг. 2 (Л. 1, Л. 2) - устройство управления (CTRL), на фиг. 3-блок основного мультиплексора (GMUX), на фиг. 4 (Л. 1, Л. 2) - блок памяти операторов (SO), на фиг. 5 - блок памяти параметров (SP), на фиг. 6 - блок памяти циклов (SC), на фиг. 7 - устройство арифметическое (ALU), на фиг. 8 (Л. 1, Л. 2) - процессор адресный (АР).

Устройство содержит вход 1 - вход поступления управляющего сигнала PUSK; вы ход 2 - выход статусного сигнала STOP; устройство 3 управления; блок 4 памяти операторов; блок 5 памяти параметров; блок 6 памяти циклов; блок 7 основного мультиплексора, устройство 8 арифметическое; процессор 9 адресный; вход 10 - вход маркера данных от контроллера внешней памяти данных MDI_M; вход 11 - вход данных от контроллера внешней памяти данных DI_M; вход 12 - сигнал LAST_CMD, подтверждающий выполнение контроллером внешней памяти всех запросов; вход 13 - сигнал LAST_DAT, подтверждающий поступление от контроллера внешней памяти последнего данного; вход 14 - сигнал переполнения контроллера внешней памяти OVFL_M; вход 15 - вход маркера данных от вычислительной схемы MDI_U; вход 16 - вход данных от вычислительной схемы DI_U; выход 17 - выход маркера адреса МА_M для контроллера внешней памяти; выход 18 - выход адреса A_M для контроллера внешней памяти; выход 19 - выход маркера данных MDO_M для контроллера внешней памяти; выход 20 - выход данных DO_M для контроллера внешней памяти; выход 21 - выход последнего запроса для контроллера внешней памяти LOP_M; выход 22 - выход маркера данных для вычислительной схемы MDO_U; выход 23 - выход данных для вычислительной схемы DO_U.

Устройство 3 управления (фиг. 2 Л1, Л2) содержит четыре элемента И24, 26, 33.1, 33.2 четыре триггера FD25, 28, 30, 54, сдвиговый регистр SRG31, три дешифратора DC32, 34, 36, сорок элементов ИЛИ27, 29, 35.1-35.3, 37-53, 55-72.

Блок 7 основного мультиплексора (фиг. 3) содержит восемь элементов И73, 75, 77, 79, 86, 89-91, семь элементов ИЛИ81-85, 87, 92, четыре регистра REG74, 76, 78, 80, триггер FD88, мультиплексор МХ93.

Блок 4 памяти операторов (фиг. 4 Л1, Л2) содержит двадцать два элемента И94.1-94.3, 98, 101-103, 106, 112, 114, 117, 119, 123, 125, 129, 131, 135, 137, 138, 142-144, пять элементов ИЛИ95, 104, 105, 139, 145, четыре инвертора НЕ115, 121, 127, 133, два мультиплексора МХ96, 107, два блока памяти RAM100, ПО, пять триггеров FD97, 99, 108, 140, 141, счетчик СТ109, девять регистров REG111, 113, 116, 120, 122, 126, 128, 132, 134, четыре сумматора ADD118, 124, 130, 136.

Блок 5 памяти параметров (фиг. 5) содержит семь элементов И146, 149, 150, 158, 160-162, три элемента ИЛИ147, 151, 163, мультиплексор МХ152, блок памяти RAM155, триггер FD153, четыре регистра REG148, 154, 156, 157, компаратор 159.

Блок 6 памяти циклов (фиг. 6) содержит девять элементов И164, 167, 172, 175, 195, 196, 186, 190, 192, пять элементов ИЛИ165, 169, 173, 181, 197, три мультиплексора МХ166, 170, 178, три триггера FD171, 179, 187, счетчик СТ188, блок памяти RAM 180, четыре регистра REGI74, 182-184, три компаратора 185, 189, 191, вычитатель 193.

Устройство 8 арифметическое (фиг. 7) содержит три мультиплексора МХ198, 199, 207, три элемента И200, 202, 204, два элемента ИЛИ206, 208, умножитель MULT201, сумматор-вычитатель 203, делитель DIV205.

Процессор 9 адресный (фиг. 8 Л1, Л2) содержит четырнадцать элементов И209, 218, 220, 229, 232, 234, 243, 244, 250, 254, 261, 265-267, одиннадцать элементов ИЛИ214, 215, 225, 226, 235, 238, 240, 245, 247, 258, 268, семь регистров REG210-212, 219, 221, 269, 271, восемнадцать триггеров FD217, 230, 231, 233, 236, 237, 239, 241, 242, 246, 255-257, 259, 262, 263, 270, 272, три мультиплексорами 13, 227, 264, три сумматора 216, 223, 228, вычитатель 222, три компаратора 224, 249, 253, элемент XOR251, два счетчика СТ248, 252, блок памяти FIFO260.

Вход 1 управляющего сигнала PUSK устройства (фиг. 1) соединен с первым входом устройства 3 управления, двунаправленный вывод CTRL которого соединен с двунаправленными выводами CTRL блоков 4 памяти операторов, 5 памяти параметров, 6 памяти циклов, процессора 9 адресного, устройства 8 арифметического и блока 7 основного мультиплексора, выход GB которого соединен с первыми входами GB блоков 4 памяти операторов, 5 памяти параметров, 6 памяти циклов и процессора 9 адресного, второй вход SPA которого соединен с первым входом устройства 8 арифметического и с первым выходом SPA блока 5 памяти параметров, второй выход SPB которого соединен с третьим входом процессора 9 адресного, вторым входом устройства 8 арифметического, первым входом блока 7 основного мультиплексора и вторым входом блока 4 памяти оператора, первый выход OP которого разрядами поля VI связан соответственно с второго по шестой входами устройства 3 управления, разрядами полей V2, V3 с вторым входом ОР блока 5 памяти параметров и разрядами полей V2, V3, V4 с вторым входом ОР блока 6 памяти циклов, третий вход ALU которого соединен с третьим входом блока 5 памяти параметров и выходом ALU устройства 8 арифметического, четвертый вход SCA1 процессора 9 адресного соединен с первым выходом блока 6 памяти циклов, второй выход SCA2 которого соединен с третьим входом устройства 8 арифметического, четвертый вход SCB которого соединен с третьим выходом SCB блока 6 памяти циклов и вторым входом блока 7 основного мультиплексора, третий вход SS которого соединен с вторым выходом SS блока 4 памяти операторов, с первого по четвертый выходы SD, SEG, BASA и MOD процессора 9 адресного соединены соответственно с четвертого по седьмой входами блока 7 основного мультиплексора, второй выход STOP устройства 3 управления соединен с первым выходом 2 устройства, с второго по восьмой входы 10÷16 которого соединены соответственно с пятого по одиннадцатый входами процессора 9 адресного, с пятого по одиннадцатый выходы которого соединены соответственно с второго по восьмой выходами 17÷23 устройства.

Первый вход PUSK устройства 3 управления (фиг. 2 Л1, Л2) соединен с первым входом элемента ИЛИ27, второй вход которого соединен с выходом элемента И26, первый вход которого соединен с вторым входом LST устройства управления и первым входом элемента И24, второй вход которого соединен с вторым входом элемента И26, выходом триггера FD30, входами сброса сдвигового регистра SRG31, дешифраторов DC36, DC34 и выходом GEND двунаправленного вывода CTRL, выход элемента И24 соединен с входом триггера FD25, выход которого соединен с выходом статусного сигнала STOP устройства управления, выход триггера FD28 соединен с выходом INSTR двунаправленного вывода CTRL и информационным входом сдвигового регистра SRG31, выходы с первого Q1 по двенадцатый Q12 которого соединены соответственно с выходами Τ1÷T12 двунаправленного вывода CTRL, выход Q3 регистра SRG31 соединен с управляющим входом дешифратора DC32, первый и второй информационные входы которого соединены соответственно с третьим и четвертым входами MPO, MPI устройства управления, с первый по четвертый выходы дешифратора DC32 соединены соответственно с выходами MODV1÷MODV4 двунаправленного вывода CTRL, вход триггера FD30 соединен с выходом элемента ИЛИ29, с первого по пятый входы которого соединены соответственно с входами END_AP÷END_GMUX двунаправленного вывода CTRL, пятый вход СОР устройства управления восемью битами соединен с информационным входом дешифратора DC36 и двумя битами СОР(3:2) с информационным входом дешифратора DC34, управляющий вход которого соединен с выходом элемента И33.2, выход элемента И33.1 соединен с управляющим входом дешифратора DC36, шестой вход ТО устройства управления соединен с первыми входами элементов И33.1, И33.2, вторые входы которых соединены с входом Т4 двунаправленного вывода CTRL, выход QM2 дешифратора DC34 соединен с первыми входами элементов ИЛИ35.1, ИЛИ35.2, первый вход элемента ИЛИ35.3 соединен с выходом QM1 дешифратора DC34, выход QM3 которого соединен с вторыми входами элементов ИЛИ35.1, ИЛИ35.3, второй вход элемента ИЛИ35.2 соединен с выходом QM0 дешифратора DC34, выходы элементов ИЛИ35.1, ИЛИ35.2, ИЛИ35.3 соединены соответственно с выходами PA, OP_RD, OP_WR двунаправленного вывода CTRL, выходы Q33, Q59, Q157 дешифратора DC36 соединены соответственно с первого по третий входами элемента ИЛИ37, выход которого соединен с выходом MOVSSXX двунаправленного вывода CTRL, выход LOOP которого соединен с выходом элемента ИЛИ38, входы которого соединены с выходами Q8, Q10 дешифратора DC36, выходы Q12, Q14 которого соединены с входами элемента ИЛИ39, выход которого соединен с выходом IFPP двунаправленного вывода CTRL, выход ADDO_MOVO которого соединен с выходом элемента ИЛИ40, входы которого соединены с выходами Q3, Q4 дешифратора DC36, выходы Q9, Q8, Q12, Q4, Q6 которого соединены соответственно с выходами RET, LOOP_CALL, IFPP_CALL, MOVO, CLRO двунаправленного вывода CTRL, выходы Q57, Q84, Q85, Q87÷Q91, Q93, Q161 дешифратора DC36 соединены соответственно с входами элемента ИЛИ41, выход которого соединен с выходом MOVSPXX двунаправленного вывода CTRL, выход ARITHM_SP которого соединен с выходом элемента ИЛИ42, входы которого соединены соответственно с выходами Q0, Q1, Q188, Q190, Q192 дешифратора DC36, выходы Q83, Q21, Q81 которого соединены соответственно с выходами MOVSPSD, PAUSE, MOVSCSD двунаправленного вывода CTRL, выход MOVSCXX которого соединен с выходом элемента ИЛИ43, входы с первого по десятый которого соединены соответственно с выходами Q55, Q159, Q162, Q163, Q165-Q169, Q171 дешифратора DC36, выходы Q2, Q7, Q189, Q191, Q193 которого соединены соответственно с первого по пятый входы элемента ИЛИ44, выход которого соединен с выходом ARITHM_SC двунаправленного вывода CTRL устройства управления, выход OP_MULT которого соединен с выходом элемента ИЛИ45, входы которого соединены с выходами Q192, Q193 дешифратора DC36, выходы Q7, Q0 которого соединены с входами элемента ИЛИ46, выход которого соединен с выходом OP ADD двунаправленного вывода CTRL, выход OP_ASUB которого соединен с выходом элемента ИЛИ47, входы с первого по четвертый которого соединены с выходами Q0-Q2, Q7 дешифратора DC36, выходы Q188, Q189 которого соединены с входами элемента ИЛИ48, выход которого соединен с выходом OP_DIV двунаправленного вывода CTRL, выход DIV_FRACT которого соединен с выходом элемента ИЛИ49, входы которого соединены с выходами Q190, Q191 дешифратора DC36, выходы Q39, Q65, Q143 которого соединены с входами элемента ИЛИ50, выход которого соединен с выходом MOVSEGXX двунаправленного вывода CTRL, выход MOVBASXX которого соединен с выходом элементом ИЛИ51, входы которого соединены с выходами Q32, Q58, Q136 дешифратора DC36, выходы Q41, Q67, Q144 которого соединены с входами элемента ИЛИ52, выход которого соединен с выходом MOVMODXX двунаправленного вывода CTRL, выход MOVSD_WR двунаправленного вывода CTRL устройства управления (Л2) соединен с выходом элемента ИЛИ53, входы с первого по десятый которого соединены с выходами QUO, QUI, Q113÷Q117, Q119, Q56, Q160 дешифратора DC36, одиннадцатый вход элемента ИЛИ53 соединен с выходом триггера FD54, информационный вход которого соединен с выходом Q82 дешифратора DC36, управляющий вход и вход сброса триггера FD54 соединены соответственно с входами VALID_SD и GEND двунаправленного вывода CTRL, выходы Q58, Q59, Q61÷Q65, Q67 дешифратора DC36 соединены соответственно с входами с первого по восьмой элемента ИЛИ55, выход которого соединен с выходом MOVRGSD двунаправленного вывода CTRL и первым входом элемента ИЛИ56, входы со второго по четвертый которого соединены соответственно с выходами Q81-Q83 дешифратора DC36, выход элемента ИЛИ56 соединен с выходом MOVSD_RD двунаправленного вывода CTRL, выходы MOVRON1XX, MOVRON2XX, MOVRON3XX, MOVRON4XX, MOVXXMOD, MOVXXSS которого соединены соответственно с выходами элементов ИЛИ57-ИЛИ62, входы элемента ИЛИ57 соединены соответственно с выходами Q35, Q61, Q139 дешифратора DC36, выходы Q36, Q62, Q140 которого соединены с входами элемента ИЛИ58, входы элемента ИЛИ59 соединены с выходами Q37, Q63, Q141 дешифратора DC36, выходы Q38, Q64, Q142 которого соединены с входами элемента ИЛИ60, входы элемента ИЛИ61 соединены с выходами Q93, Q119, Q171 дешифратора DC36, выходы Q85, Q111, Q163 которого соединены с входами элемента ИЛИ62, выходы MOVXXRON1, MOVXXRON2, MOVXXRON3, MOVXXRON4, MOVXXSEG, MOVXXBAS двунаправленного вывода CTRL соединены соответственно с выходами элементов ИЛИ63÷ИЛИ68, входы элемента ИЛИ63 соединены с выходами Q87, Q113, Q165 дешифратора DC36, выходы Q88, Q114, Q166 которого соединены с входами элемента ИЛИ64, входы элемента ИЛИ65 соединены с выходами Q89, Q115, Q167 дешифратора DC36, выходы Q90, Q116, Q168 которого соединены с входами элемента ИЛИ66, входы элемента ИЛИ67 соединены с выходами Q91, Q117, Q169 дешифратора DC36, выходы которого Q84, QUO, Q162 соединены с входами элемента ИЛИ68, выходы дешифратора Q32, Q33, Q35÷Q39, Q41 соединены с входами элемента ИЛИ69, выход которого соединен с выходом MOVRGSP двунаправленного вывода CTRL и первым входом элемента ИЛИ70, входы с второго по четвертый которого соединены соответственно с выходами Q55÷Q57 дешифратора DC36, выход элемента ИЛИ70 соединен с выходом MOVXXSP двунаправленного вывода CTRL, выходы дешифратора Q136, Q137, Q139÷Q144 соединены с входами элемента ИЛИ71, выход которого соединен с выходом MOVRGSC двунаправленного вывода CTRL и первым входом элемента ИЛИ72, входы с второго по четвертый которого соединены с выходами Q159÷Q161 дешифратора DC36, выход элемента ИЛИ72 соединен с выходом MOVXXSC двунаправленного вывода CTRL.

С первого BASA по седьмой SD входы блока 7 основного мультиплексора (фиг. 3) соединены соответственно с первого DO по седьмой D6 информационными входами мультиплексора МХ93, с восьмого D7 по одиннадцатый D10, информационные входы которого соединены соответственно с выходами регистров REG74, REG76, REG78, REG80, выходы элементов ИЛИ81÷ИЛИ84 соединены соответственно с адресными входами мультиплексора МХ93, выход которого соединен с выходом GB блока и с информационными входами регистров REG74, REG76, REG78, REG80, управляющие входы которых соединены соответственно с выходами элементов И73, И75, И77, И79, первые входы которых соединены с входом GBH двунаправленного вывода CTRL, входы MOVRON1XX÷MOVRON4XX соединены соответственно с вторыми входами элементов И73, И75, И77, И79, выход элемента ИЛИ87 соединен с управляющим входом мультиплексора МХ93 и входом триггера FD88, выход которого соединен с выходом GBM двунаправленного вывода CTRL, входы VALID_SD и Т7 которого соединены соответственно с первыми входами элементов ИЛИ87 и И86, выход элемента И86 соединен с вторым входом элемента ИЛИ 87, второй вход элемента И86 соединен с выходом элемента ИЛИ85, входы с первого по десятый которого соединены соответственно с входами MOVXXMOD, MOVXXSC, MOVXXSEG, MOVXXSS, MOVXXSP, MOVXXRON1÷MOVXXRON4, MOVXXBAS двунаправленного вывода CTRL, входы MOVXXMOD, VALID_SD, MOVXXSS, MOVXXRON1, MOVXXRON3 которого соединены с входами элемента ИЛИ81, входы элемента ИЛИ82 соединены с входами MOVXXSEG, MOVXXSP, VALID SD, MOVXXRON1, MOVXXRON4 двунаправленного вывода CTRL, входы MOVXXSC, MOVXXSS, VALIDSD, MOVXXRON1 которого соединены с входами элемента ИЛИ83, входы элемента ИЛИ84 соединены с входами MOVXXRON2÷MOVXXRON4 двунаправленного вывода CTRL, вход Т6 которого соединен с первыми входами элементов И89, И90, вторые выводы которых соединены соответственно с входами MOVRGSP и MOVRGSC двунаправленного вывода CTRL, входы GBM и MOVRGSD которого соединены с входом элемента И91, входы элемента И92 соединены с выходами элементов И89÷И91, выход И92 соединен с выходом END_GMUX двунаправленного вывода CTRL.

Первый вход GB блока 4 памяти операторов (фиг. 4 Л1, Л2) соединен с первым информационным входом мультиплексора МХ96, второй информационный вход которого соединен с первым входом памяти RAMI 10 и выходом счетчика СТ109, входы LOOP_CALL, IFPP_CALL двунаправленного вывода CTRL соединены соответственно с входами элемента И94.1, выход которого соединен с первым входом элемента И94.2, выход которого соединен с первым входом элемента ИЛИ95 и адресным входом мультиплексора МХ96, управляющий вход которого соединен с входом триггера FD97 и выходом элемента ИЛИ95, второй вход которого соединен с выходом элемента И94.3, первый и второй входы которого соединены соответственно с входами MOVSSXX и GBM двунаправленного вывода CTRL, выход мультиплексора МХ96 соединен с первым входом памяти RAM100, второй вход которого соединен с выходом триггера FD97, третий вход памяти RAM100 соединен с выходом триггера FD99, вход которого соединен с выходом элемента И98, первый и второй входы которого соединены соответственно с входами RET и T4 двунаправленного вывода CTRL, входы LOOP и T8 которого соединены соответственно с первыми и вторыми входами элементов И101, И102, третьи входы которых соединены соответственно с входами SIEQ0 и SEQ0 двунаправленного вывода CTRL, входы IFPP, T8. HEQ0 которого соединены соответственно с первого по третий входы элемента И103, выход которого соединен с первым входом элемента ИЛИ104, второй и третий входы которого соединены соответственно с выходами элементов И101, И102, выход элемента ИЛИ104 соединен с вторым входом элемента И94.2 и первым входом элемента ИЛИ105, второй вход которого соединен с адресным входом мультиплексора МХ107 и выходом элемента И106, входы которого соединены соответственно с входами RET и ТИ двунаправленного вывода CTRL, выход регистра REG111 соединен с выходом ОР блока памяти операторов, вторым входом памяти RAM110 и первым информационным входом мультиплексора MX107, второй информационный вход которого соединен с выходом памяти RAM100 и выходом SS блока памяти операторов, управляющий вход мультиплексора MX107 соединен с выходом элемента ИЛИ105 и входом триггера FD108, выход мультиплексора МХ107 соединен с первым входом счетчика СТ109, второй вход которого соединен с выходом триггера FD108, вход INSTR двунаправленного вывода CTRL соединен с управляющими входами счетчика СТ109 и регистра REG111, информационный вход которого соединен с первым выходом памяти RAM110, вход записи WEB которого соединен с первым входом элемента ИЛИ145 и выходом триггера FD141, вход которого соединен с выходом триггера FD140 и с управляющими входами (Л. 2) сумматоров ADD118, ADD124, ADD130, ADD136, выходы Q_ADD которых соединены с третьим входом памяти RAM110 (Л. 1), вход триггера FD140 соединен с выходом элемента ИЛИ139, входы которого соединены соответственно с выходами элементов И137, И138, входы которых соединены соответственно с входами ADDO_MOVO, Т7, CLRO, Т6 двунаправленного вывода CTRL, входы RET, Т4, LOOP, Т8, IFPP, Τ 8 которого соединены соответственно с входами элементов И142-И144, выходы которых соединены соответственно с второго по четвертый входы элемента ИЛИ145, выход которого соединен с выходом END_SO двунаправленного вывода CTRL, второй выход SOB памяти RAM110 соединен соответственно разрядами поля V1 (Л. 2) с информационным входом регистра REG113, разрядами поля V2 с информационным входом регистра REG120, разрядами поля V3 - с информационным входом регистра REG126, разрядами поля V4 - с информационным входом регистра REG132, управляющие входы CE которых соединены с входом Т6 двунаправленного вывода CTRL, второй вход SPB сектора памяти операторов соединен соответственно с информационными входами регистров REG116 разрядами SPB(B-1:0), регистра REG122 - разрядами SPB(C-1:0), регистра REG128 -разрядами SPB(D-1:0), регистра REG134 - разрядами SPB(E-1:0), управляющие входы СЕ которых соединены с выходом элемента И114, входы которого соединены соответственно с входами ADDO_MOVO и Т7 двунаправленного вывода CTRL, вход MOVO двунаправленного вывода CTRL соединен с первыми входами элементов И112, И119, И125, И131, вторые входы которых соединены соответственно с входами MODV1-MODV4 двунаправленного вывода CTRL, выходы элементов И112, И119, И125, И131 соединены соответственно с входами сброса регистров REG113, REG120, REG126, REG132, выходы которых соединены соответственно с первыми информационными входами сумматоров ADD118, ADD124, ADD130, ADD136, вторые информационные входы которых соединены соответственно с выходами регистров REG116, REG122, REG128, REG134, входы сброса которых соединены соответственно с выходами элементов НЕ115, НЕ121, НЕ127, НЕ133, входы которых соединены соответственно с входами MODV1-MODV4 двунаправленного вывода CTRL, входы сброса сумматоров ADD118, ADD124, ADD130, ADD136 соединены соответственно с выходами элементов И117, И123, И129, И135, первые входы которых соединены соответственно с входами MODV1-MODV4 двунаправленного вывода CTRL, вход CLRO которого соединен с вторыми входами элементов И117, И123, И129, И135.

Первый вход ОР блока 5 памяти параметров (фиг. 5) соединен разрядами поля V2(F-1:0) с информационным входом регистра REG148, управляющий вход которого соединен с выходом элемента ИЛИ147, первый вход которого соединен с выходом элемента ИЛИ146, первый и второй входы которого соединены соответственно с входами MOVSPXX и GBH двунаправленного вывода CTRL, входы Т2 и ALU_M которого соединены соответственно с вторым и третьим входами элемента ИЛИ146, выход регистра REG148 соединен с первым входом памяти RAM155, второй вход которой соединен с выходом мультиплексора MX152, первый и второй информационные входы которого соединены соответственно с вторым GB и третьим ALU входами блока памяти параметров, управляющий вход мультиплексора МХ152 соединен с входом триггера FD153 и выходом элемента ИЛИ151, первый и второй входы которого соединены с выходами элементов И149, И150, входы которых соединены соответственно с входами ALU_M, ARITHM_SP, MOVSPXX, GBM двунаправленного вывода CTRL, вход ALU_M которого соединен с адресным входом мультиплексора МХ152, выход триггера FD153 соединен с входом записи WEA памяти RAM155, третий вход которой соединен с выходом регистра REG154, информационный вход которого соединен с первым входом ОР блока памяти параметров разрядами поля V3(F-1:0), управляющий вход регистра REG154 соединен с входом Т2 двунаправленного вывода CTRL, вход Т8 которого соединен с управляющими входами регистров REG156, REG157, информационные входы которых соединены соответственно с первым и вторым выходами памяти RAM155, выход регистра REG156 соединен с первым выходом SPA блока памяти параметров, второй выход SPB которого соединен с выходом регистра REG157 и информационным входом компаратора 159, управляющий вход которого соединен с выходом элемента И158, входы которого соединены с входами IFPP и Т7 двунаправленного вывода CTRL, входы ARITHM_SP, ALU_M, MOVSPXX, Т6, MOVSPSD, GBM соединены соответственно с входами элементов И160-И162, выходы которых соединены с входами элемента ИЛИ 163, выход которого соединен с выходом END_SP двунаправленного вывода CTRL, выход HEQ0 которого соединен с выходом компаратора 159.

Первый вход ОР блока 6 памяти циклов (фиг. 6) разрядами поля V2(G-1:0) и поля V4(G-1:0) соединен соответственно с первым и вторым информационными входами мультиплексора MX166, управляющий вход которого соединен с выходом элемента ИЛИ165, первый вход которого соединен с выходом элемента И164, входы которого соединены соответственно с входами MOVSCXX и GBM двунаправленного вывода CTRL, вход Т2 которого соединен с адресным входом мультиплексора MX166 и вторым входом элемента ИЛИ165, третий и четвертый входы которого соединены соответственно с входами Т3 и ALU_M двунаправленного вывода CTRL, второй GB и третий ALU входы блока памяти циклов соединены соответственно с первым и вторым информационными входами мультиплексора МХ170, управляющий вход которого соединен с входом триггера FD171 и выходом элемента ИЛИ169, входы которого соединены соответственно с выходами элементов И167, И164, входы элемента И169 соединены с входами ALU_M, ARITHM_SC двунаправленного вывода CTRL, вход ALU M которого соединен с адресным входом мультиплексора MX 170, с первого по третий входы памяти RAM180 соединены соответственно с выходами мультиплексоров МХ166, MX170 и триггера FD171, четвертый вход памяти RAM180 соединен с выходом регистра REG174, информационный вход которого соединен с входом ОР блока памяти циклов разрядами поля V3(G-1:0), управляющий вход регистра REG174 соединен с выходом элемента ИЛИ173, первый вход которого соединен с выходом элемента ИЛИ172, входы которого соединены соответственно с входами LOOP, Т8, SEQ0 двунаправленного вывода CTRL, вход Т2 которого соединен с вторым входом элемента ИЛИ173, первый информационный входы мультиплексора MX178 соединен с выходом SIDEC вычитателя 193, второй информационный вход мультиплексора MX178 соединен с выходом REG183 и первым выходом SCA1 блока памяти циклов, управляющий вход мультиплексора MX178 соединен с выходом элемента И172, входом триггера FD179 и первым входом элемента И175, второй вход которого соединен с входом SIEQ0 двунаправленного вывода CTRL, выход элемента И175 соединен с адресным входом мультиплексора MX178, выход которого соединен с пятым входом памяти RAM180, шестой вход которой соединен с выходом триггера FD179, первый выход памяти RAM180 соединен с информационным входом регистра REG182, управляющий вход которого соединен с выходом элемента ИЛИ181, первый вход которого соединен с входом Т6 двунаправленного вывода CTRL и управляющим входом регистра REG184, информационный вход которого соединен с вторым выходом памяти RAM180, выход регистра REG182 соединен с информационными входами регистра REG183 и компаратора 185, первым информационным входом компаратора 189 и вторым выходом SCA2 блока памяти циклов, первый вход элемента И186 соединен с входом PAUSE двунаправленного вывода CTRL, вход LOOP которого соединен с первыми входами элементов И190, И192, вход Т7 двунаправленного вывода CTRL соединен с вторыми входами элементов ИЛИ181, И186, И190, управляющими входами компаратора 185 и регистра REG183, выход регистра REG184 соединен с информационным входом компаратора 191, первым информационным входом вычитателя 193 и третьим выходом SBC блока памяти циклов, выход компаратора 185 соединен с выходом SEGO двунаправленного вывода CTRL, выход элемента И186 соединен с управляющим входом триггера FD187, информационный вход которого соединен с логической «1», выход триггера FD187 соединен с информационным входом счетчика СТ188 и управляющим входом компаратора 189, второй информационный вход которого соединен с выходом счетчика СТ188, вход сброса которого соединен с выходом компаратора 189, входом сброса триггера FD187 и первым входом элемента ИЛИ197, второй вход которого соединен с выходом Q элемента И167, третий и четвертый входы элемента ИЛИ 197 соединены соответственно с выходами элементов И195, И196, входы MOVSCXX и Т6, MOVSCSD и GBM двунаправленного вывода CTRL соединены соответственно с входами элементов И195, И196, выход элемента ИЛИ197 соединен с выходом END_SC двунаправленного вывода CTRL, выход элемента И190 соединен с управляющим входом компаратора 191, выход которого соединен с выходом SIEQ0 двунаправленного вывода CTRL, вход Т8 которого соединен с вторым входом элемента И192, выход которого соединен с управляющим входом вычитателя 193, второй информационный вход которого соединен с логической «1».

Первый SPA и второй SCA2 входы устройства 8 арифметического (фиг. 7) соединены соответственно с первым и вторым информационными входами мультиплексора MX198, управляющий вход которого соединен с управляющим входом мультиплексора MX199 и входом Т8 двунаправленного вывода CTRL, вход ARITHM_SC которого соединен с адресными входами мультиплексоров МХ198, МХ199, первый и второй информационные входы мультиплексора MX199 соединены соответственно с третьим SPB и четвертым SCB входами двунаправленного вывода CTRL, выход мультиплексора MX199 соединен с первыми входами умножителя 201, сумматора-вычитателя 203, делителя 205, вторые входы которых соединены с выходом мультиплексора MX198, третий вход умножителя 201 соединен с выходом элемента И200, входы которого соединены с входами Т9 и OP_MULT двунаправленного вывода CTRL, вход OP_ADD которого соединен с третьим входом сумматора-вычитателя 203, четвертый вход которого соединен с выходом элемента И202, входы которого соединены с входами Т9 и OP_ASUB двунаправленного вывода CTRL, входы Т9 и OP_DIV которого соединены с входами элемента И204, выход которого соединен с третьим входом делителя 205, первый и второй информационные входы мультиплексора МХ207 соединены соответственно с первыми входами умножителя 201 и сумматора-вычитателя 203, третий и четвертый информационные входы мультиплексора МХ207 соединены соответственно с первым и вторым выходами делителя 205, третий выход которого соединен с первым входом элемента ИЛИ208, второй и третий входы которого соединены соответственно с вторыми выходами сумматора-вычитателя 203 и умножителя 201, первый адресный вход мультиплексора МХ207 соединены с выходом элемента ИЛИ206, входы которого соединены с входами OP_ASUB и DIV FRACT двунаправленного вывода CTRL, вход OP_DIV которого соединен с вторым адресным входом мультиплексора МХ207, выход которого соединен с выходом ALU устройства 8 арифметического, выход элемента ИЛИ208 соединен с выходом ALU_M двунаправленного вывода CTRL.

Первый вход GB процессора 9 адресного (фиг. 8 Л1, Л2) соединен с информационными входами регистров REG210, REG219, REG221, управляющие входы которых соединены соответственно с выходами элементов И209, И218, И220, первые входы которых соединены с входом GBM двунаправленного вывода CTRL, входы MOVSEGXX, MOVBASXX, MOVMODXX которого соединены соответственно с вторыми входами элементов И209, И218, И220, второй SPA и третий SPB входы процессора адресного соединены соответственно с информационными входами регистров REG211, REG212, управляющие входы которых соединены соответственно с входом Т7 двунаправленного вывода CTRL, вход Т8 которого соединен с входом установки в ноль сумматора 216 и с адресным входом мультиплексора МХ213, первый и второй информационные входы которого соединены соответственно с выходами регистров REG211, REG212, выход сумматора 216 соединен с первыми информационными входами сумматора 223 и компаратора 224, с входом триггера FD217 и первым информационным входом сумматора 216, второй информационный вход которого соединен с выходом мультиплексора МХ213, управляющий вход сумматора 216 соединен с выходом элемента ИЛИ215, вход Т9 двунаправленного вывода CTRL соединен с первым входом элемента ИЛИ215 и первыми входами элементов И243, И244, вторые входы которых соединены соответственно с входами OP_RD, OP_WR двунаправленного вывода CTRL, входы ADR_RQ_WR, ADR_RQ_RD, которого соединены с входами элемента ИЛИ214, выход которого соединен с вторым входом элемента ИЛИ215 и первым входом элемента И229, второй вход которого соединен с входом RDY двунаправленного вывода CTRL, входы MOVSD_WR, GBM, MOVSD_RD, Т7 которого соединены соответственно с входами элементов И232, И234, выход регистра REG219 соединен с выходом BASA процессора адресного и с первым входом вычитателя 222, второй вход которого соединен с выходом регистра REG221, выходом MOD процессора адресного и вторым информационным входом компаратора 224, вход установки в ноль которого соединен с входом РА двунаправленного вывода CTRL, выход триггера FD217 соединен с первым информационным входом мультиплексора МХ227, второй вход которого соединен с выходом сумматора 223, второй вход которого соединен с выходом вычитателя 222, третий и четвертый информационные входы мультиплексора МХ227 соединены соответственно с входами SPA и SPB процессора адресного, выход регистра REG210 соединен с выходом SEG процессора адресного и первым информационным входом сумматора 228, второй информационный вход которого соединен с выходом мультиплексора МХ227, выход сумматора 228 соединен с выходом A_M процессора адресного, первый и второй адресные входы мультиплексора МХ227 соединены соответственно с выходами элементов ИЛИ225, ИЛИ226, управляющий вход мультиплексора МХ227 соединен с входом триггера FD236 и выходом элемента ИЛИ235, первый вход которого соединен с выходом триггера FD231, вход которого соединен с выходом триггера FD230, вход которого соединен с выходом элемента И229, выход элемента И232 соединен с первым входом элемента ИЛИ238 и входом триггера FD233, выход которого соединен с вторым входом элемента ИЛИ235 и первым входом элемента ИЛИ226, выход компаратора 224 соединен с первым входом элемента ИЛИ225, второй вход которого соединен с вторым входом элемента ИЛИ226, третьим входом ИЛИ235, первым входом элемента ИЛИ240 и выходом элемента И234, второй вход элемента ИЛИ240 соединен с выходом триггера FD239, вход которого соединен с выходом элемента ИЛИ238, второй вход которого соединен с входом END_DATA двунаправленного вывода CTRL, выход триггера FD236 соединен с управляющим входом сумматора 228 и входом триггера FD237, выход которого соединен с выходом MA_M процессора адресного, выход элемента ИЛИ240 соединен с входом триггера FD241, выход которого соединен с входом триггера FD242, выход которого соединен с выходом LOP_M процессора адресного, выходы элементов И243, И244 соединены с входами элемента ИЛИ245, выход которого соединен с управляющим входом триггера FD246, информационный вход которого соединен с логической «1», выход триггера FD246 соединен с выходом RDY двунаправленного вывода CTRL, вход END_DATA которого соединен с входом установки в ноль триггера FD246, четвертый вход SCA1 процессора адресного (Л. 2) соединен с первым входом счетчика СТ248, второй вход которого соединен с входом Т8 двунаправленного вывода CTRL, третий вход счетчика СТ248 соединен с логическим «0», входы ADR_RQ_WR и ADR_RQ_RD соединены с входами элемента ИЛИ247, выход которого соединен с управляющими входами компаратора 249 и счетчика CT248, выход которого соединен с первым информационным входом компаратора 249, второй информационный вход которого соединен с логической «1», входы OP_RD и RDY двунаправленного вывода CTRL соединены с первым и вторым входами элемента И250, выход компаратора 249 соединен с выходом END_DATA двунаправленного вывода CTRL, с входом установки в ноль компаратора 249 и третьим входом элемента И250, четвертый вход которого соединен с первым входом элемента И254 и входом OVFL_M процессора адресного, выход элемента И250 соединен с выходом ADR_RQ_RD двунаправленного вывода CTRL, вход MDI_U процессора адресного соединен с первым входом элемента XOR251, входом записи памяти FIFO260 и первым входом счетчика СТ252, управляющий вход которого соединен с выходом элемента XOR251, второй вход которого соединен с входом ADR_RQ_WR двунаправленного вывода CTRL, вход RDY которого соединен с входом установки в ноль счетчика СТ252, выход которого соединен с первым входом компаратора 253, второй вход которого соединен с логическим нулем, выход компаратора 253 соединен с вторым входом элемента И254, третий и четвертый входы которого соединены соответственно с входами END_DATA, OP_WR двунаправленного вывода CTRL, выход ADR_RQ_WR которого соединен с выходом элемента И254 и входом триггера FD255, выход которого соединен с входом триггера FD256, выход которого соединен с входом чтения памяти FIFO260 и входом триггера FD257, выход которого соединен с первым входом элемента ИЛИ258, второй вход которого соединен с выходом триггера FD263 и адресным входом мультиплексора МХ264, выход элемента ИЛИ258 соединен с входом триггера FD259, выход которого соединен с выходом MDO_M процессора адресного, вход DI_U которого соединен с информационным входом памяти FIFO260, выход которой соединен с первым информационным входом мультиплексора МХ264, второй вход которого соединен с входом GB процессора адресного, выход DO_M которого соединен с выходом мультиплексора МХ264, входы MOVSD_WR и GBM двунаправленного вывода CTRL соединены с входами элемента И261, выход которого соединен с входом триггера FD262, выход которого соединен с входом триггера FD263, первые входы элементов И265, И266, И267 соединены соответственно с входами OP_RD, OP_WR и MOVSD_WR двунаправленного вывода CTRL, вторые входы элементов И266, И267 соединены с входом LAST_CMD процессора адресного, вход LAST_DAT которого соединен с вторым входом элемента И265, выходы элементов И265-И267 соединены с входами элемента ИЛИ268, выход которого соединен с выходом END_AP двунаправленного вывода CTRL, вход OP_RD которого соединен с входами установки в ноль регистров REG269, REG271 и триггеров FD270, FD272, вход DI_M процессора адресного соединен с информационными входами регистров REG269, REG271, выходы которых соединены соответственно с выходами DO_U и SD процессора адресного, вход MDI_M которого соединены с информационными входами триггеров FD270, FD272, выход триггера FD272 соединен с выходом VALID SD двунаправленного вывода CTRL, выход триггера FD270 соединен с выходом MDO_U процессора адресного.

Мультиконтроллер распределяемой памяти (DMC) обеспечивает передачу данных между внешней оперативной памятью данных (SD) и устройством обработки информации (процессором). В SD располагаются данные, представляющие собой исходные значения величин, промежуточные и окончательные результаты. Внутренняя оперативная память DMC делится на три блока: память операторов (SO), память параметров (SP), память циклов (SC) и служит для хранения программы и вспомогательных параметров.

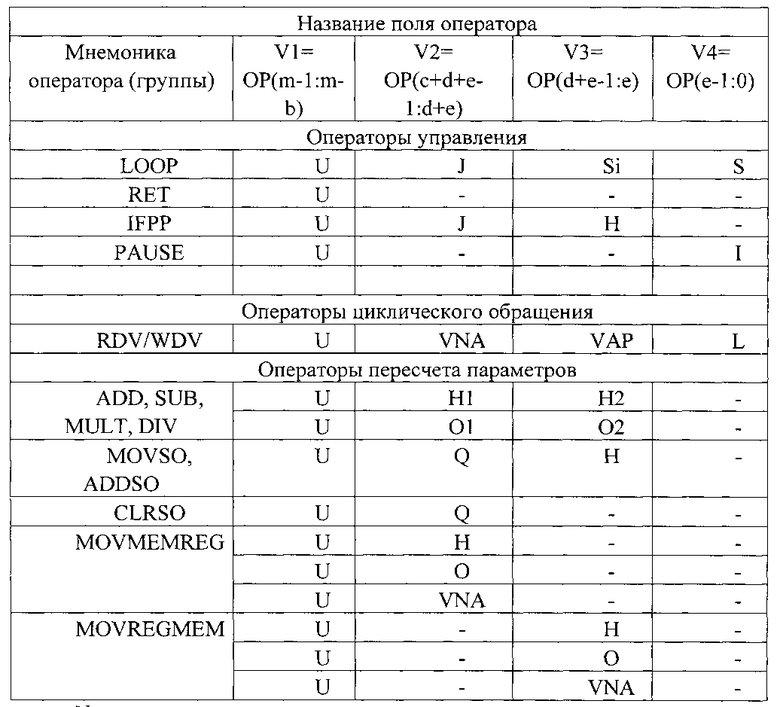

SO содержит четырехкомпонентные операторы. Каждому оператору в зависимости от его типа могут соответствовать параметры, хранящиеся в SP и/или SC. В SP хранятся x-компонентные вектора начальных адресов SD и x-компонентные вектора адресных приращений, где x - количество каналов доступа к SD, а также вспомогательные переменные для организации условных переходов. В SC хранятся x-компонентные вектора длин потоков данных и вспомогательные переменные для организации циклов. Для определенности в дальнейшем примем x=1.

DMC осуществляет управление циклическим чтением/записью потока данных с типом адресации инкрементная или пороговая и выполняет модификацию полей оператора и параметров оператора. В результате этого операторы можно разделить на три группы:

- операторы управления;

- операторы циклического обращения;

- операторы пересчета параметров.

Формат операторов, хранящихся в SO, содержит т разрядов и имеет следующий вид:

где U - поле управления;

J - адрес оператора, к которому осуществляется переход;

Si - адрес текущей константы цикла в SC;

S - адрес константы цикла в SC;

H - адрес переменной в SP;

I - адрес длительности паузы в SC;

L - адрес длины потока в SC;

O - адрес переменной в SC;

Q - адрес модифицируемого оператора в SO;

VNA - адрес вектора начальных адресов в SP;

VNP - адрес вектора адресных приращений в SP;

OP(m-1:0) - выход памяти операторов;

m - разрядность оператора;

b - разрядность поля V1;

c - разрядность поля V2;

d - разрядность поля V3;

e - разрядность поля V4.

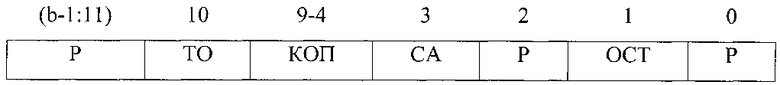

Формат поля U оператора обращения содержит Ь разрядов и имеет следующий вид:

Формат поля U операторов управления и пересчета содержит b разрядов и имеет следующий вид:

где P - резерв;

ТО - тип оператора; КОП - код операции;

СА - признак сохранения следующего адреса;

ОСТ - признак последнего оператора;

МП - код модифицируемого поля оператора.

Для операторов обращения бит ТО=0, для операторов управления и пересчета бит ТО=1.

При СА=1 после выполнения соответствущего оператора обращения выполняется модификация содержимого памяти операторов вида SP(VNA)=LA+SP(VAP), где LA - последний адрес обращения к памяти при выполнении данного оператора.

При ОСТ=1 после выполнения соответствующего оператора следующий оператор из памяти операторов не считывается, и вырабатывается признак STOP.

Код МП может принимать следующие значения:

МП=00 - модификация поля U оператора;

МП=01 - модификция поля V1 оператора;

МП=10 - модификция поля V2 оператора;

МП=11 - модификция поля V3 оператора.

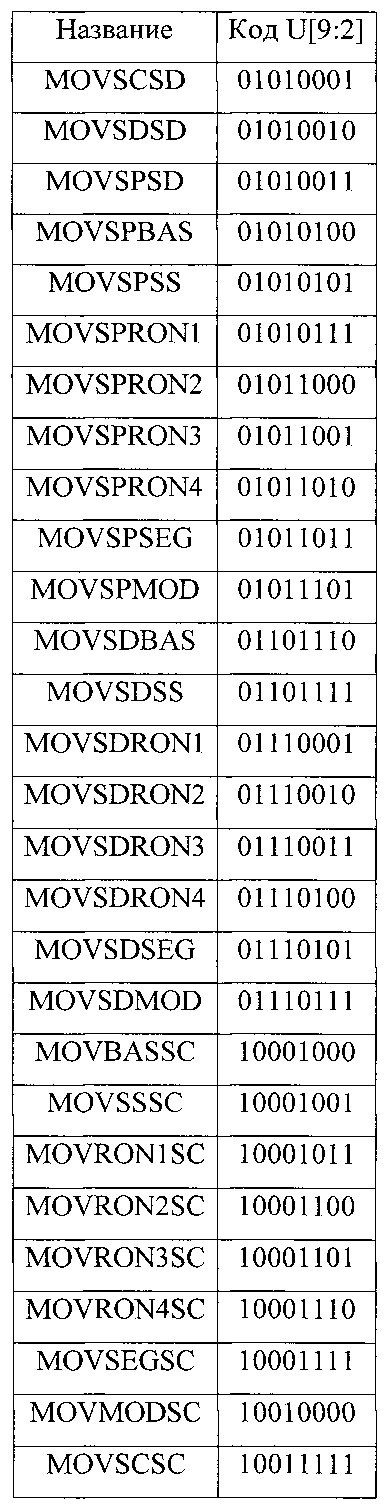

Мультиконтроллер распределяемой памяти выполняет алгоритмы операторов, кодировки которых приведены в таблицах 1-3.

Для инициализации процедуры обращения на вход 1 устройства поступает сигнал PUSK. В устройстве 3 управления по сигналу PUSK вырабатываются управляющие сигналы: импульс INSTR (триггер 28) и серия импульсов Т1-Т12 (сдвиговый регистр 31). В блоке 4 памяти операторов по импульсу INSTR происходит прием оператора в регистр 111 и наращивание счетчика адреса 109. Поле V1 оператора из регистра 111 поступает в устройство 3 управления, поля V2-V3 поступают в блок 5 памяти параметров и блок 6 памяти циклов. Поле V4 поступает в блок 6 памяти циклов. В устройстве 3 управления поле V1 дешифрируется. Вырабатываются соответствующие признаки и управляющие сигналы. Если тип оператора ТО=1, то используется дешифратор операторов пересчета и управления 36. Если тип оператора ТО=0, то используется дешифратор 34 операторов обращения к памяти. В блоках 5 памяти параметров и 6 памяти циклов поля V2-V4 используются в качестве адресов для чтения из памяти соответствующих параметров. В блоке 4 памяти операторов поле V1 используется в качестве адреса перехода J при выполнении операторов цикла и условного перехода. Далее выполняется определенный алгоритм, соответствующий исполняемому оператору. Выполнение любого оператора заканчивается формированием одного из сигналов: END_SO (элемент ИЛИ145), END_SP (элемент ИЛИ163), END_SC (элемент ИЛИ197), END_GMUX (элемент ИЛИ92) или END AP (элемент ИЛИ268). Эти сигналы объединяются на элементе ИЛИ29 в устройстве 3 управления и формируют сигнал GEND (триггер 30). Если признак последнего оператора U(1)=0, то по сигналу GEND вырабатываются новый импульс INSTR, последовательность импульсов Т1-Т12 и начинается выполнение следующего оператора. В том случае если U(1)=1, то по сигналу GEND на триггере 25 вырабатывается импульс STOP, который передается в УЭВМ.

Рассмотрим порядок выполнения операторов обращения. В операторах циклического чтения/записи потока данных формируются вектора адресов данных по следующим алгоритмам.

Операторы с типом инкрементная адресация IA выполняются по следующему алгоритму:

где i - номер канала памяти данных i=0,1, …, x-1;

j - номер вектора j=0,1, …, SC(L)-1;

- вектор начальных адресов ВНА;

- i-й элемент ВНА;

- i-й элемент ВНА;

ΔA - вектор адресных приращений ВАП;

ΔAi - i-й элемент ВАП;

Aj - вектор текущего адреса;

- i-й элемент вектора текущего адреса.

- i-й элемент вектора текущего адреса.

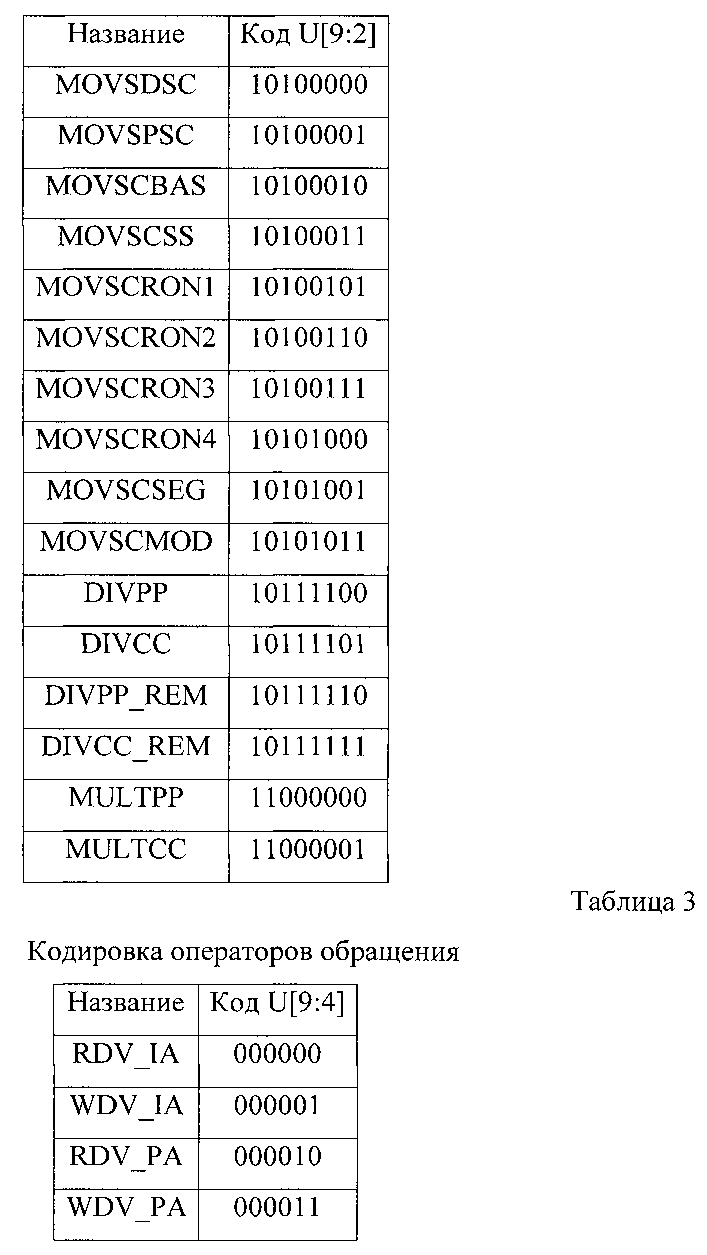

Операторы с типом пороговая адресация РА выполняются по следующему алгоритму

где  - i-й элемент ВНА;

- i-й элемент ВНА;

- i-й элемент вектора текущего адреса;

- i-й элемент вектора текущего адреса;

Ai - i-й элемент ВАП;

BASA, MOD - константы в соответствующих регистрах DMC;

i - номер канала памяти данных i=0,1, …, x-1;

j - номер вектора j=0,1, …, SC(L)-1.

За время одного цикла выполнения оператора циклического обращения осуществляется операция чтение/запись одного вектора адресов данных. По адресу, расположенному в поле V2, из блока 5 памяти параметров считывается вектор начальных адресов, который через регистр 156 по шине SPA поступает в процессор 9 адресный и далее через регистр 212 и мультиплексор 213 сохраняется в сумматоре 216, складываясь с нулем по управляющему сигналу Т9. По адресу, расположенному в поле V3, из блока 5 памяти параметров считывается вектор адресных приращений, который через регистр 157 по шине SPB поступает в процессор 9 адресный и сохраняется в регистре 211 по управляющему сигналу Т7. С регистра 211 ВАП через мультиплексор 213 подается на вход D2 сумматора 216. По адресу, расположенному в поле V4, из блока 6 памяти циклов считывается вектор количества обращений ВКО, который через регистры 182 и 183 по шине SCA1 поступает в процессор 9 адресный и далее загружается в счетчик количества обращений 248 по управляющему сигналу Т8. По сигналу Т9 в процессоре 9 адресном в триггере 246 устанавливается управляющий сигнал RDY.

При OP_RD=l выполняется оператор чтения. По сигналу RDY на элементе И250 в процессоре адресном начинает вырабатываться внутренняя команда чтения ADR_RQ_RD. По этому сигналу на сумматоре 216 формируется поток адресов согласно алгоритмам операторов циклического обращения. Полученные адреса с выхода A_M процессора адресного поступают на контроллер внешней памяти данных в сопровождении маркера адресов MA_M. Также по сигналу ADR_RQ_RD происходит декрементация счетчика количества обращений 248. После генерации заданного количества обращений на компараторе 249 вырабатывается сигнал ENDDATA, сбрасывающий сигналы RDY и ADR_RQ_RD. Адрес последнего обращения передается контроллеру внешней памяти с признаком LOPJV1. Данные, прочитанные из памяти, поступают на вход DI_M процессора 9 адресного в сопровождении маркера MDI_M. Далее через регистр 269 они передаются пользователю на шину DO_U в сопровождении маркера MDO_U. Последнее данное передается из контроллера внешней памяти в адресный процессор с признаком LAST_DAT. По этому признаку на элементах И265 и ИЛИ268 вырабатывается признак окончания оператора чтения END_AP.

При OP_WR=1 выполняется оператор записи. Данные, предназначенные для записи в память, поступают от пользователя по шине DI_U в сопровождении маркера MDI_U и сохраняются в буфере FIFO 260. При наличии данных и сигнала RDY=1 вырабатывается внутренняя команда записи ADR_RQ_WR. По этому сигналу на сумматоре 216 формируется поток адресов согласно алгоритмам операторов циклического обращения. Полученные адреса с выхода A_M процессора адресного поступают на контроллер внешней памяти данных в сопровождении маркера адресов MA_M. Также по сигналу ADR_RQ_WR происходит декрементация счетчика количества обращений 248 и чтение данных из буфера FIFO 260. Данные из буфера 260 через мультиплексор 264 поступают на выход DO_M и далее на контроллер внешней памяти. Сопровождаются данные стробом MDO_M, получаемым на триггере 259. Количество данных в буфере 260 подсчитывается с помощью счетчика 252. При MDI_U=1 и ADR_RQ_WR=0 выполняется инкремент содержимого счетчика, а при MDI_U=0 и ADR_RQ_WR=1 выполняется декремент содержимого счетчика, при условии, что RDY=1. После генерации заданного количества обращений на компараторе 249 вырабатывается сигнал END_DATA, сбрасывающий сигналы RDY и ADR RQ WR. Адрес последнего обращения передается контроллеру внешней памяти с признаком LOP_M. Обработав обращение к памяти с признаком LOP_M, контроллер возвращает в процессор 9 адресный импульс LAST_CMD, по которому на элементах И266 и ИЛИ268 вырабатывается признак окончания оператора записи END_AP.

Для операторов обращения с инкрементной адресацией каждый следующий адрес формируется на сумматоре 216 в соответствии с выражением (1).

В случае операторов обращения с пороговой адресацией каждый следующий адрес формируется в два этапа в соответствии с выражениями (2,3). Значение

Рассмотрим порядок выполнения операторов управления.

В операторе цикла LOOP_J происходит вычисление адреса следующего оператора. В блоке 6 памяти циклов из памяти 180 считывается переменная по адресу S, которая сохраняется в регистрах 182 и 183. Значение этой переменной сравнивается с нулем с помощью компаратора 185. В результате вырабатывается признак SEQ0, который передается в блок 4 памяти операторов. Также в блоке 6 памяти циклов из памяти 180 считывается переменная по адресу SI, которая сохраняется регистре 184. Значение этой переменной сравнивается с нулем с помощью компаратора 191. В результате вырабатывается признак SIEQ0, который также передается в блок 4 памяти операторов, где при SEQ0=1 осуществляется безусловный переход по адресу J. Для этого указанный адрес из регистра 111 через мультиплексор 107 загружается в счетчик 109. Если же SEQ0=0, то анализируется признак SIEQ0. При SIEQ0=0 (SC(SI)>0) также осуществляется переход к оператору по адресу J. Дополнительно в блоке 6 памяти значение переменной в регистре 184 уменьшается на единицу в вычитателе 193 и записывается через мультиплексор 178 в память 180 по адресу SI, т.е. происходит декремент значения ячейки SC(SI). При SIEQ0=1 (SC(SI)=0) осуществляется переход к следующему по порядку оператору. Для этого счетчик 109 в блоке 4 памяти операторов просто наращивается на единицу по импульсу INSTR. Дополнительно в блоке 6 памяти циклов переменная из регистра 183 через мультиплексор 178 записывается в память 180 по адресу SI, т.е. происходит восстановление ячейки SC(SI) значением SC(S).

В том случае, если выполняется вызов подпрограммы (оператор LOOP_J_CALL), то адрес выполняемого оператора цикла с выхода счетчика 109 в блоке 4 памяти операторов через мультиплексор 96 записывается в стек 100 по команде PUSH как адрес возврата. При выполнении оператора RETURN этот адрес считывается из стека 100 по команде POP и через мультиплексор 107 загружается в счетчик 109, где используется для возврата к исходному оператору цикла.

В операторе условного перехода IFPP_J происходит вычисление адреса следующего оператора по следующему алгоритму. В блоке 5 памяти параметров по адресу H из памяти 155 считывается переменная, которая сохраняется в регистре 157. Значение этой переменной сравнивается с нулем с помощью компаратора 159. В результате вырабатывается признак HEQ0, который передается в блок 4 памяти операторов. Если HEQ0=0 (SP(H)>0), осуществляется переход к оператору по адресу J. Для этого указанный адрес из регистра 111 через мультиплексор 107 загружается в счетчик 109. Если HEQ0=1 (SP(H)=0), осуществляется переход к следующему по порядку оператору. Для этого счетчик 109 в блоке 4 памяти операторов наращивается на единицу по импульсу INSTR.

В том случае если выполняется вызов подпрограммы (оператор IFPP_J_CALL), то адрес выполняемого оператора условного перехода с выхода счетчика 109 в блоке 4 памяти операторов через мультиплексор 96 записывается в стек 100 по команде PUSH как адрес возврата. При выполнении оператора RETURN этот адрес считывается из стека 100 по команде POP и через мультиплексор 107 загружается в счетчик 109, где используется для возврата к исходному оператору условного перехода.

Оператор PAUSE используется для генерации пустых тактов. Количество тактов определяется значением переменной, расположенной в блоке 6 памяти циклов в памяти 180 по адресу I. Эта переменная сохраняется в регистре 182, откуда поступает на вход D1 компаратора 189. По импульсу Т7 на триггере 187 вырабатывается сигнал СЕ для счетчика 188. Выход этого счетчика подключен к входу D2 компаратора 189. Счет продолжается до тех пор, пока значение на выходе счетчика 188 не совпадет со значением SC(I), хранящемся в регистре 182. При совпадении этих значений на выходе компаратора 189 вырабатывается сигнал ENDP, который сбрасывает триггер 187, счетчик 188 и формирует сигнал END_SC.

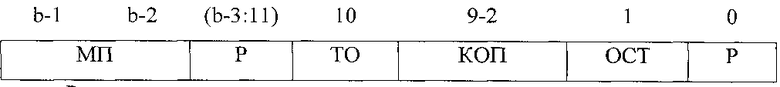

Рассмотрим порядок выполнения операторов пересчета. Группу операторов пересчета можно разбить на следующие подгруппы: арифметические операторы модификации отдельных ячеек памяти параметров и памяти циклов; операторы модификации отдельных полей выбранного оператора в памяти операторов; операторы переноса данных между сегментами памяти и регистрами DMC.

В операторе ADDPP производится модификация сложения ячейки памяти параметров H1:

SP(H1):=SP(H1)+SP(H2),

где SP(H1) - ячейка памяти параметров по адресу H1, SP(H2) - ячейка памяти параметров по адресу H2.

В память 155 блока 5 памяти параметров адрес H1 поступает через регистр 148. Адрес H2 поступает через регистр 154. Считываемые переменные сохраняются соответственно в регистрах 156 и 157. С этих регистров переменные по шинам SPA и SPB поступают в устройство 8 арифметическое и далее через мультиплексоры 198 и 199 на сумматор 203. Управляющий сигнал OP_ADD используется для выбора операции сложения. Управляющие сигналы Т9 и OP_ASUB используются для загрузки операндов в сумматор. Результат сложения через мультиплексор 207 поступает на шину ALU. Также сумматор формирует сигнал V, подтверждающий верность результата, который с помощью элемента ИЛИ208 преобразуется в сигнал ALU_M. Результат по шине ALU в сопровождении строба ALU_M передается в блок 5 памяти параметров и через мультиплексор 152 в память 155. Запись результата осуществляется по адресу H1. Сигнал записи формируется из сигналов ALU_M и ARITHM_SP с помощью элементов И149, ИЛИ151 и триггера 153.

В операторе ADDCC производится модификация сложения ячейки памяти циклов O1:

SC(O1):=SC(O1)+SC(O2),

где SC(O1) - ячейка памяти циклов по адресу O1, SC(O2) - ячейка памяти циклов по адресу 02.

В память 180 блока 6 памяти циклов адрес O1 поступает через мультиплексор 166. Адрес 02 поступает через регистр 174. Считываемые переменные сохраняются соответственно в регистрах 182 и 184. С этих регистров переменные по шинам SCA2 и SCB поступают в устройство 8 арифметическое и далее через мультиплексоры 198 и 199 на сумматор 203. Управляющий сигнал OP_ADD используется для выбора операции сложения. Управляющие сигналы Т9 и OP_ASUB используются для загрузки операндов в сумматор. Результат сложения через мультиплексор 207 поступает на шину ALU. Также сумматор формирует сигнал V, подтверждающий верность результата, который с помощью элемента ИЛИ208 преобразуется в сигнал ALU_M. Результат по шине ALU в сопровождении строба ALU_M передается в блок 6 памяти циклов и через мультиплексор 170 в память 180. Запись результата осуществляется по адресу O1. Сигнал записи формируется из сигналов ALU_M и ARITHMSC с помощью элементов И167, ИЛИ169 и триггера 171.

В операторах SUBPP/SUBCC, MULTPP/MULTCC, DIVPP/DIVCC, DIVPP_REM/DIVCC_REM аналогичным образом выполняются модификации вычитания, умножения, деления и остатка от деления для памяти параметров и памяти циклов соответственно. Для этих целей в устройстве 8 арифметическом используются сумматор-вычитатель 203, умножитель с фиксированной запятой 201 и делитель с фиксированной запятой 205.

Далее рассмотрим операторы модификации отдельных полей выбранного оператора. Выбор поля для модификации i осуществляется в соответствии с таблицей 4.

В операторах ADDSO производится модификация полей оператора Q:

SO(Q)i:=SO(Q)i+SP(H),

где SO(Q)i - i-e поле оператора по адресу Q, i=1, 2, 3, 4;

SP(H) - переменная в памяти параметров по адресу Н.

Адрес Q поступает на вход ADDRB памяти 110, входящей в состав блока 4 памяти операторов. Модифицируемые поля оператора V1-V4 с выхода DOB памяти 110 поступают на регистры 113, 120, 126 и 132 соответственно. Адрес H поступает на вход ADDRB памяти 155, входящей в состав блока 5 памяти параметров. Переменная SP(H) через регистр 157 по шине SPB передается в блок 4 памяти операторов на вход регистров 116, 122, 128, 134. Все эти регистры, за исключением регистра соответствующего модифицируемому полю оператора, находятся в состоянии сброса, т.е. на выходе этих регистров нуль. Сигналы сброса формируется с помощью инверторов 115, 121, 127 и 133. С помощью сумматоров 118, 124, 130 и 136 выполняется сложение модифицируемого поля оператора SO(Q)1 с переменной SP(H) и сложение остальных полей оператора SO(Q) с нулем. В результате чего изменяется только модифицируемое поле оператора, а остальные поля остаются прежними. Результат сложения поступает на вход DIB памяти ПО и записывается по адресу Q по сигналу с триггера 141. По этому же сигналу на элементе ИЛИ145 формируется сигнал END_SO.

В операторах MOVSO производится модификация полей оператора Q:

SO(Q)i:=SP(H),

где SO(Q)i - i-e поле оператора по адресу Q, i=1, 2, 3, 4;

SP(H) - переменная в памяти параметров по адресу H.

Оператор выполняется аналогично рассмотренному выше оператору ADDSO за следующим исключением. С помощью элементов И112, 119, 125, 131 формируется сигнал сброса для регистра, хранящего модифицируемое поле оператора SO(Q)i. В результате с помощью сумматоров 118, 124, 130 и 136 выполняется сложение нуля с переменной SP(H) для модифицируемого поля и сложение остальных полей оператора SO(Q) с нулем. Таким образом, модифицируемое поле просто замещается переменной SP(H).

В операторах CLRSO производится модификация полей оператора Q:

SO(Q)i:=0,

где SO(Q)i - i-e поле оператора по адресу Q, i=1, 2, 3, 4.

Оператор выполняется аналогично рассмотренному выше оператору ADDSO за следующим исключением. С помощью элементов И117, 123, 129, 135 формируется сигнал сброса для сумматора, обрабатывающего модифицируемое поле оператора SO(Q)i. В результате этот сумматор на выходе даст нуль. Остальные сумматоры на выходе дадут исходные поля оператора. Таким образом, обнуляется только модифицируемое поле оператора SO(Q)i.

Операторы группы MOV делятся на следующие виды: MOVREGMEM, MOVMEMREG, MOVMEM1MEM2.

В операторе MOVREGMEM происходит замена содержимого регистра REG содержимым ячейки памяти MEM, расположенным по адресу A:

REG:=MEM(A).

В состав DMC входят следующие регистры. В блок 7 основного мультиплексора входят четыре регистра общего назначения RON1-RON4: 74, 76, 78, 80. В процессор 9 адресный входят регистры SEG, BASA и MOD: 210, 219 и 221 соответственно. В блок 4 памяти операторов входит стек адресов 100, с которым также работают операторы перемещения. С другой стороны операторы группы MOV работают с блоком 5 памяти параметров, блоком 6 памяти циклов и внешней памятью данных.

Рассмотрим порядок выполнения оператора MOVREGMEM при работе с блоком 5 памяти параметров. Адрес A поступает через регистр 154 на вход ADDRB памяти 155. Переменная SP(A) через регистр 157 по шине SPB передается в блок 7 основного мультиплексора на мультиплексор 93. С выхода мультиплексора 93 по шине GB эта переменная попадает на входы всех регистров DMC. Наличие на шине GB верной информации подтверждается стробом GBM, который формируется на триггере 88. По сигналу GBM информация с шины GB записывается в выбранный регистр в соответствии с исполняемым оператором.

Рассмотрим порядок выполнения оператора MOVREGMEM при работе с блоком 6 памяти циклов. Адрес А поступает через регистр 174 на вход ADDRB памяти 180. Переменная SC(A) через регистр 184 по шине SCB передается в блок 7 основного мультиплексора на мультиплексор 93. Далее порядок выполнения оператора аналогичен случаю работы с блоком памяти параметров.

Рассмотрим порядок выполнения оператора MOVREGMEM при работе с внешним сегментом данных. Адрес A поступает через регистр 154 на вход ADDRB памяти 155, входящей в состав блока 5 памяти параметров. Переменная SP(A) через регистр 157 по шине SPB передается в процессор 9 адресный на вход D3 мультиплексора 227. И далее через сумматор 228 попадает на шину адреса A_M в сопровождении строба MA_M. Строб формируется из сигналов MOVSD_RD и Т7 на элементах 234, 235, 236 и 237. Из этих же сигналов на элементах 234, 240, 241 и 242 формируется признак LAST_OP. Совокупность сигналов A_M, MA_M, LOP_M образует команду чтения из внешней памяти данных переменной SD(SP(A)). Считанное значение возвращается в процессор адресный по шине DI_M в сопровождении строба MDI_M. С шины DI_M информация через регистр 271 попадает на шину SD. Из строба MDI_M на триггере 272 формируется строб VALID_SD. По шине SD информация в сопровождении строба VALID_SD поступает в блок 7 основного мультиплексора на мультиплексор 93. Далее порядок выполнения оператора аналогичен случаю работы с блоком памяти параметров.

В операторе MOVMEMREG происходит замена содержимого ячейки памяти MEM по адресу A содержимым регистра REG:

MEM(A):=REG.

Рассмотрим порядок выполнения оператора MOVMEMREG при работе с блоком 5 памяти параметров. Все регистры DMC подключены ко входам мультиплексора 93, входящего в состав блока 7 основного мультиплексора. При выполнении оператора информация с соответствующего регистра поступает на шину GB в сопровождении строба GBM. По шине GB содержимое регистра поступает на вход DO мультиплексора 152 и далее - на вход DIA памяти 155 в блоке 5 памяти параметров. Адрес A поступает через регистр 148 на вход ADDRA памяти 155. Сигнал записи формируется на элементе И150 из сигналов GBM и MOVSPXX и через элемент ИЛИ151 и триггер 153 поступает на вход WEA памяти 155.

При работе с блоком 6 памяти циклов информация с соответствующего регистра поступает на шину GB в сопровождении строба GBM. По шине GB содержимое регистра поступает на вход D0 мультиплексора 170 и далее - на вход DIA памяти 180 в блоке 6 памяти циклов. Адрес А поступает через мультиплексор 166 на вход ADDRA памяти 180. Сигнал записи формируется на элементе И164 из сигналов GBM и MOVSCXX и через элемент ИЛИ169 и триггер 171 поступает на вход WEA памяти 155.

Рассмотрим порядок выполнения оператора при перемещении содержимого одного из регистров во внешнюю память данных. В блоке памяти параметров адрес A через регистр 148 поступает на вход ADDRA памяти 155. Информация с выхода DOA памяти 155 через регистр 156 по шине SPA передается в процессор 9 адресный. Там она попадает на вход D2 мультиплексора 227. И далее через сумматор 228 попадает на шину адреса A_M. В блоке 7 основного мультиплексора информация с соответствующего регистра через мультиплексор 93 поступает на шину GB в сопровождении строба GBM. По этой шине она передается в процессор 9 адресный на вход D1 мультиплексора 264 и далее - на шину DO_M. Из строба GBM и признака MOVSD_WR на элементах 232, 233, 235, 236 и 237 формируется строб адреса MA_M. Из этих же сигналов на элементах 232, 238, 239, 240, 241 и 242 формируется признак LAST_OP, а на элементах 261, 262, 263, 258, 259 - строб данных MDO_M. Совокупность сигналов A_M, MA_M, LOP_M, MDO_M, DO_M образует команду записи перемещаемого данного во внешнюю память данных. После выполнения этой команды контроллер памяти возвращает признак LAST_CMD, из которого на элементах И267 и ИЛИ268 формируется сигнал END_AP.

В операторе MOVMEM1MEM2 происходит замена содержимого ячейки памяти MEM1 по адресу A содержимым ячейки памяти MEM2 по адресу B:

MEM1(A):=MEM2(B).

При выполнении оператора чтение данного из выбранной памяти осуществляется в том же порядке, что и при выполнении оператора MOVREGMEM и было рассмотрено выше. Запись данного в выбранную память осуществляется в том же порядке, что и при выполнении оператора MOVMEMREG и также было рассмотрено выше.

Блоки заявляемого устройства могут быть полностью реализованы на программируемых логических интегральных схемах (ПЛИС) зарубежного производства. Например, ПЛИС семейства Virtex-6 фирмы Xilinx (см. http://xilinx.com) или ПЛИС семейства Stratix V фирмы Altera (см. http://www.altera.com).

Введение в устройство новых элементов, соединенных соответствующим образом, позволяет, во-первых, за счет разделения внутренней памяти на три независимых блока обеспечить прямую адресацию константы цикла и более быструю скорость доступа к распределенной памяти.

Во-вторых, замена регистра возврата на стек позволяет организовывать подпрограммы большей вложенности.

В-третьих, введение арифметико-логического устройства и соответствующих операторов пересчета совместно с дополнительными операторами перемещения параметров существенно расширяет возможности программирования.

Приложение - принятые обозначения.

n - основная разрядность, соотв. разрядности адреса памяти (32)

m - разрядность оператора (64)

k - разрядность данных памяти (32)

a - разрядность адреса памяти операторов (10)

b - разрядность поля V1 (16)

c - разрядность поля V2 (12)

d - разрядность поля V3 (16)

e - разрядность поля V4 (20)

f - разрядность адреса памяти параметров (8)

g - разрядность адреса памяти циклов (8)

x - число каналов доступа к памяти, обслуживаемых одним КРП

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| МУЛЬТИКОНТРОЛЛЕР РАСПРЕДЕЛЕННОЙ ПАМЯТИ | 2001 |

|

RU2210804C2 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

Изобретение относится к области вычислительной техники. Технический результат заключается в обеспечении автономного произвольного доступа к памяти без использования дополнительных ресурсов. Указанный технический результат достигается за счет более сложной организации внутренней памяти, а именно в разделении ее на три независимых блока, использования в предлагаемом изобретении арифметико-логического устройства для выполнения арифметических действий над параметрами операторов, оптимизации связей между различными блоками для более рационального перемещения параметров, расширения системы команд. 11 ил., 4 табл.

Устройство мультиконтроллер распределяемой памяти, обеспечивающее сложную автономную процедуру доступа к каналам распределяемой памяти, отличающееся тем, что устройство содержит устройство управления, блок памяти операторов, блок памяти параметров, блок памяти циклов, блок основного мультиплексора, устройство арифметическое, процессор адресный, причем вход управляющего сигнала устройства соединен с первым входом устройства управления, двунаправленный вывод которого соединен с двунаправленными выводами блоков памяти операторов, памяти параметров, памяти циклов, процессора адресного, устройства арифметического и блока основного мультиплексора, выход которого соединен с первыми входами блоков памяти операторов, памяти параметров, памяти циклов и процессора адресного, второй вход которого соединен с первым входом устройства арифметического и с первым выходом блока памяти параметров, второй выход которого соединен с третьим входом процессора адресного, вторым входом устройства арифметического, первым входом блока основного мультиплексора и вторым входом блока памяти оператора, первый выход которого разрядами поля V1 связан соответственно с второго по шестой входами устройства управления, разрядами полей V2, V3 с вторым входом блока памяти параметров и разрядами полей V2, V3, V4 с вторым входом блока памяти циклов, третий вход которого соединен с третьим входом блока памяти параметров и выходом устройства арифметического, четвертый вход процессора адресного соединен с первым выходом блока памяти циклов, второй выход которого соединен с третьим входом устройства арифметического, четвертый вход которого соединен с третьим выходом блока памяти циклов и вторым входом блока основного мультиплексора, третий вход которого соединен с вторым выходом блока памяти операторов, с первого по четвертый выходы процессора адресного соединены соответственно с четвертого по седьмой входами блока основного мультиплексора, второй выход устройства управления соединен с первым выходом устройства, с второго по восьмой входы которого соединены соответственно с пятого по одиннадцатый входами процессора адресного, с пятого по одиннадцатый выходы которого соединены соответственно с второго по восьмой выходами устройства.

| МУЛЬТИКОНТРОЛЛЕР РАСПРЕДЕЛЕННОЙ ПАМЯТИ | 2001 |

|

RU2210804C2 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Шланговое соединение | 0 |

|

SU88A1 |

| Способ защиты системы водяного отопления от замораживания | 1988 |

|

SU1548606A1 |

Авторы

Даты

2015-05-10—Публикация

2014-07-21—Подача