(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ ЛОГИЧЕСКИХ БЛОКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный измеритель | 1973 |

|

SU485458A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| Многоканальный измеритель аналоговых сигналов | 1982 |

|

SU1069152A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Многоканальное устройство ввода аналоговой информации | 1987 |

|

SU1418726A1 |

| Многоканальный аналого-цифровой процессор | 1983 |

|

SU1120375A1 |

| Устройство для счета штучных изделий | 1986 |

|

SU1367024A1 |

| МНОГОКАНАЛЬНЫЙ ПАНОРАМНЫЙ ПРИЕМНИК | 1996 |

|

RU2115997C1 |

| Многоканальное устройство для ввода аналоговых данных | 1988 |

|

SU1501025A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

1

Изобретение относится к области вычислительной техники и может найти применение в различных системах контроля и управления, а также в устройствах сопряжения аналоговой аппаратуры с цифровыми системами.

Известно устройство автоматического контроля, содержащее коммутатор, формирователь сигналов, блок уставок, логический блок, цифровой преобразователь, кодер адреса, параметров 1.

Недостатком данного устройства является низкое быстродействие, обусловленное последовательным обслуживанием - цепей параметров, текущие значения которых вышли за пределы допусков.

Наиболее близким по технической сущности к данному является устройство для контроля параметров, содержащее блоки сравнения, триггеры,блок приоритета, генератор импульсов, запоминающий блок, счетчик импульсов, цифроаналоговый преобразователь, элемент задержки и элемент ИЛИ. На каждом такте развертки напряжение с выхода цифроаналогового преобразователя (ЦАП) подается на. все блоки сравнения одновременно. Если напряжение развертки

превосходит по величине напряжения на некоторых шинах устройства, то в соответствующих каналах срабатывают блоки сравнения, после чего через блок приоритета в блок памяти по адресам сработавших каналов последовательно записывается значение кода развертки 2.

Недостатком устройства является низкая достоверность контроля, обусловленная тем, что на каждом последующем такте развертки выходное напряжение однозначно превосходит напряжение на входах уже сработавших блоков, поэтому этим каналам приписываются значения напряжений развертки- последующих тактов, что не от,вечает действительности. Кроме того, дан15ное устройство не обеспечивает параллельной записи кода напряжения развертки в блок памяти, а также прервание развертки при контроле напряжений всех каналов на первых тактах, что снижает быстродей20 ствие устройства.

Цель изобретения - повышение быстродействия и точности контроля.

Поставленная цель достигается тем, что в устройство для контроля параметров, содержащее блок памяти, генератор импульсов, счетчик импульсов, цифроаналоговый преобразователь, элемент ИЛИ, элемент задержки, многоканальный блок приоритета и группу схем сравнения, причем информационные входы устройства соединены соответственно с первыми входами схем сравнения группы, выход каждой схемы сравнения группы соединен с информационным входом соответствующего канала многоканального блока приоритета, первая группа выходов многоканального блока приоритета соединена с группой информационных входов блока памяти, первая и вторая группы информационных выходов счетчика импульсов соединены соответственно с группой адресных входов блока памяти и группой входов цифроаналогового преобразователя, выход цифроаналогового преобразователя соединен со вторыми входами схем сравнения групы, выход элемента задержки соединен с первым -входом элемента ИЛИ, выход которого соединен со входом генератора импульсов, управляющий выход блока памяти соединен со вторым входом элемента ИЛИ, введен в элемент И, причем выход генератора импульсов соединен со счетным входом счетчика импульсов, со входом элемента И, со входом элемента задержки и с первым установочным входом многоканального блока приоритета, выход элемента И соединен с установочным входом счетчика импульсов и вторым установочным входом многоканального блока приоритета, вторая группа выходов многоканального блока приоритета соединена с группой входов элемента И.

Многоканальный блок приоритета содержит в каждом канале первый и второй элемент И, первый и второй триггер, причем первый .вход первого элемента И каждого канала является информационным входом блока, выход второго элемента И каждого канала соединен с первыми входами первого и второго триггеров соответствующего канала и является выходом группы вы ходов блока приоритета, выход первого элемента И каждого канала соединен со вторым входом второго триггера соответствующего канала, выход которого соединен с первым входом второго элемента И соответ ствующего канала, второй вход второго элемента И является первым установочным входом блока, второй установочный вход блока соединен со вторыми входами вторых триггеров всех каналов, первый выход первого триггера каждого канала соединен со вторым входом первого элемента И соответствующего канала, вторые выходы первого триггера каждого канала образуют вторую группу выходов многоканального блока приоритета.

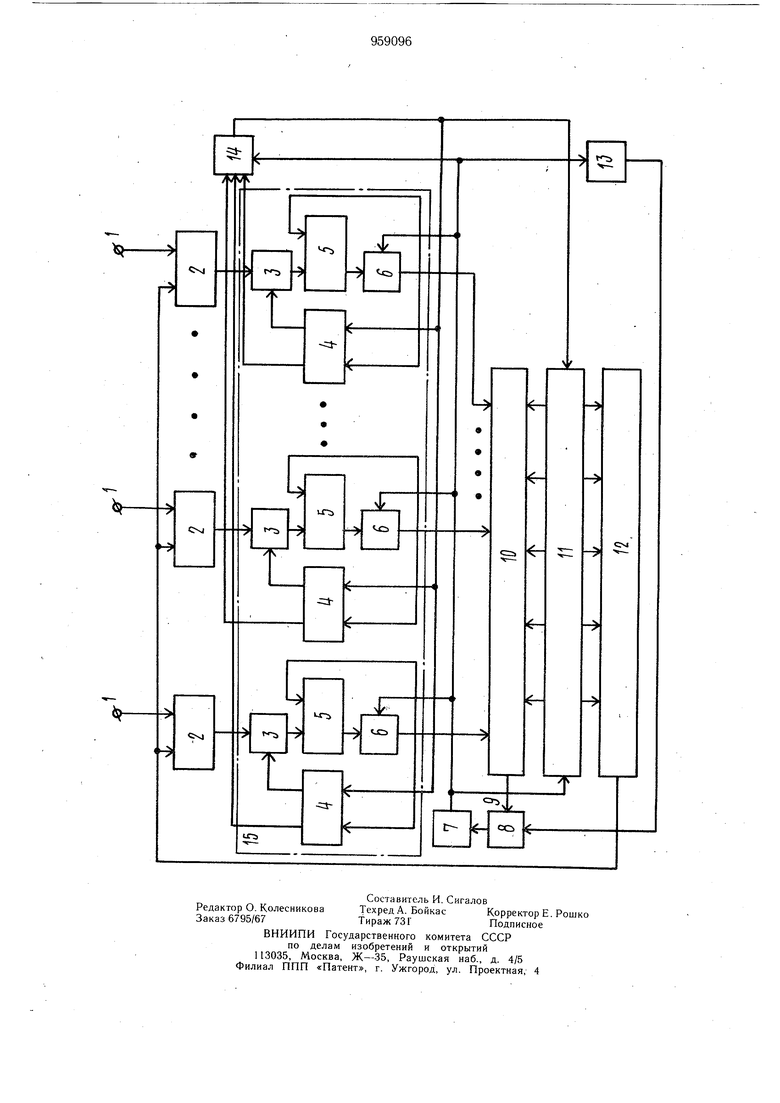

На чертеже приведена функциональная схема устройства для контроля параметров.

Схема устройства включает входы 1, контролируемых параметров, группу схем

сравнения 2, первый элемент И 3, первый триггер 4, второй триггер 5, второй элемент И 6, генератор 7 импульсов, элемент ИЛИ 8, управляющий выход блока памяти 9, блок 10 памяти, счетчик 11 импульсов, ЦАП 12, элемент 13 задержки, элемент И 14 и многоканальный блок 15 приоритета. Каждый канал многоканального блока 15 приоритета содержит в каждом канале первый и второй элементы И 3 и б и триггеры 5.

Устройство работает следующим образом.

В исходном состоянии счетчик импульсов 11 и триггеры 4 и 5 установлены в «О, элементы И 3 открыты, а элементы И 6 и элемент И 14 закрыты, на входы 1 поданы контролируемые параметры.

Запуск многоканального измерителя производится через блок 10 памяти. Запускающий импульс появляется на его выходе 9 и через элемент ИЛИ 8 возбуждает генератор 7 импульсов. Выходной импульс последнего поступает на входы элемента задержки 13 и счетчика импульсов 11, изменяя на единицу его цифровое значение, в результате чего с выхода ЦАП 12 на входы схем сравнения. 2 подается напряжение первого такта развертки.

Если это напряжение превосходит по величине напряжения на некоторых входах 1, то в соответствующих каналах срабатывают схемы сравнения и через элементы И 3 устанавливают триггера 5 этих каналов в единичное состояние, открывая соответствующие элементы И 6, в противном случае многоканальный блок приоритета 15 остается в исходном состоянии.

Импульс, поступивщий на вход элемента -задержки 13, задерживается последним на время переходных процессов в схе.ме сравнения 2 и многоканальном блоке 15 приоритета, после чего через элемент ИЛИ 8 вновь возбуждает генератор импульсов 7.

Импульс с выхода последнего поступает снова на вход элемента задержки 13 и счетчика импульсов 11, одновременно через открытые элементы И 6 производя запись информации со счетчика импульсов 11 в ячейки памяти блока 10, соответствующие номерам сработавщих каналов. Этим же сигналом триггеры 4 и 5 сработавших каналов перебрасываются соответственно в единичное и нулевое состояние, блокируя эти каналы до конца развертки и открывая по соответствующим входам элемент И 14. На входы схем сравнения 2 подается новое напряжение и следует очередной такт развертки. После нескольких тактов все каналы устройства окажутся заблокированными, что означает, что все поданные на входы 1 параметры замерены, поэтому очередной импульс с выхода элемента задержки 13, возбудив генератор импульсов 7, установит через открывшийся элемент И 14 счетчик импульсов 11 и триггеры 4 многоканального блока приоритета 15 в нулевое состояние. Устройство будет подготовлено к очередному циклу работы.

Таким образом, в предлагаемом устройстве исключается искажение информации за счет приписывания ряду каналов значений напряжений развертки последующих тактов, что повышает доставерность измерений, а также обеспечивается параллельная запись информации в блок памяти о всех сработавших на данном такте каналах и прерывание цикла развертки при измерении всех поданных на вход устройства напряжений, что повышает быстродействие устройства.

Формула изобретения

со вторым входом элемента ИЛИ, отличающееся тем, что, с целью повышения быстродействия и точности контроля, в устройство введен элемент И, причем выход генератора импульсов соединен со счетным входом счетчика импульсов, со входом элемента И, с входом элемента задержки и с первым установочным входом многоканального блока приоритета, выход элемента И соединен с установочным входом счетчика импульсов, и вторым установочным входо.м многоканаль0 ног,о блока приоритета, вторая группа выходов многоканального блока приоритета соединена с группой входов элемента И.

5 содержит в каждом канале первый и второй элемент И, первый и второй триггер, причем первый вход первого элемента И каждого канала является информационным входом блока, выход второго элемента И каждого канала соединен с первыми входами

° первого и второго триггеров соответствующего канала и является выходом группы выходов блока приоритета, выход первого элемента И каждого канала соединен со вторым входом второго триггера соответствующего канала, выход которого соединен с первым входом второго элемента И соответствующего канала, второй вход второго элемента И является первым установочным входом блока, второй установочный вход блока соединен со вторыми входами вторых

0 триггеров всех каналов, первый вход первого триггера каждого канала соединен со вторым входом первого элемента И соответствующего канала, вторые выходы первого триггера каждого канала образуют вторую группу выходов блока приоритета.

5Источники информации,

принятые во внимание при экспертизе

Авторы

Даты

1982-09-15—Публикация

1981-02-02—Подача