исключения избыточности вводимой информации. Многоканальное устройство для ввода аналоговой информации содержит коммутаторы 1 и 6, аналого- цифровой преобразователь 2, цифроана- логовый преобразователь 4, блок 3 анализа приращений сигнала, блоки памяти 5 и 19, блок 11 синхронизации, счетчики 7 и 10, регистр состояния 20, буферный регистр 24, элементы

сравнения 8 и 16, компаратор 13, генератор импульсов 18, триггеры 12 и 17, элементы И 9, 21 и 23, элементы ИЛИ 15, 22, 25 и 26. Сжатие данных в аналоговой форме позволяет исключить избыточные отсчеты во времени, а значит, сократить время ввода информации и увеличить полосу пропускания части высокочастотных каналов устройства. 1 з.п. ф-лы, 5 ил„

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Устройство для передачи телеметрической информации | 1982 |

|

SU1030830A1 |

| Устройство для контроля монтажа | 1985 |

|

SU1352505A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1988 |

|

SU1499389A1 |

| Устройство для контроля температуры | 1988 |

|

SU1515176A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1494778A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

Изобретение относится к вычислительной технике и может быть использовано в информационно-измери-ч тельных системах и гибридных вычислительных комплексах для связи аналоговой и цифровой вычислительных машин. Целью изобретения является расширение области применения за счет

Изобретение относится к вычисли™ тельной технике и может быть использовано в информационно-измерительных системах и в гибридных вычислитель- ных комплексах для связи аналоговой и цифровой вычислительных машин.

Целью изобретения является расширение области применения за счет исключения избыточности вводимой ин-

формации.

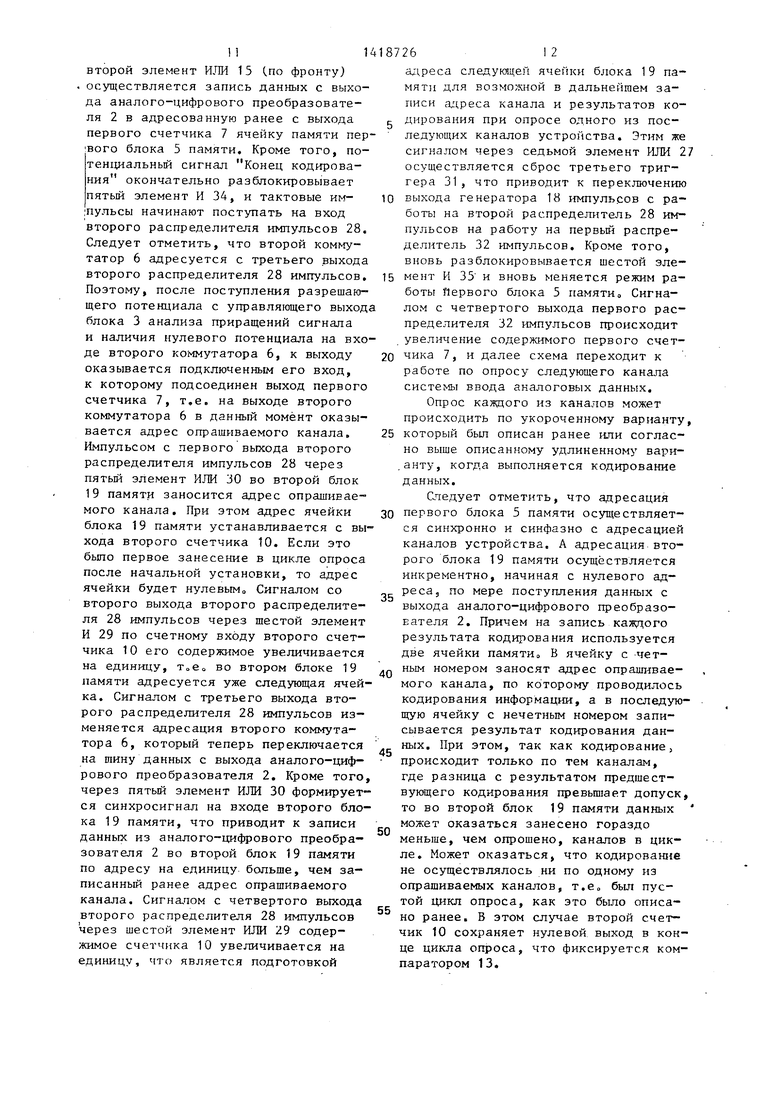

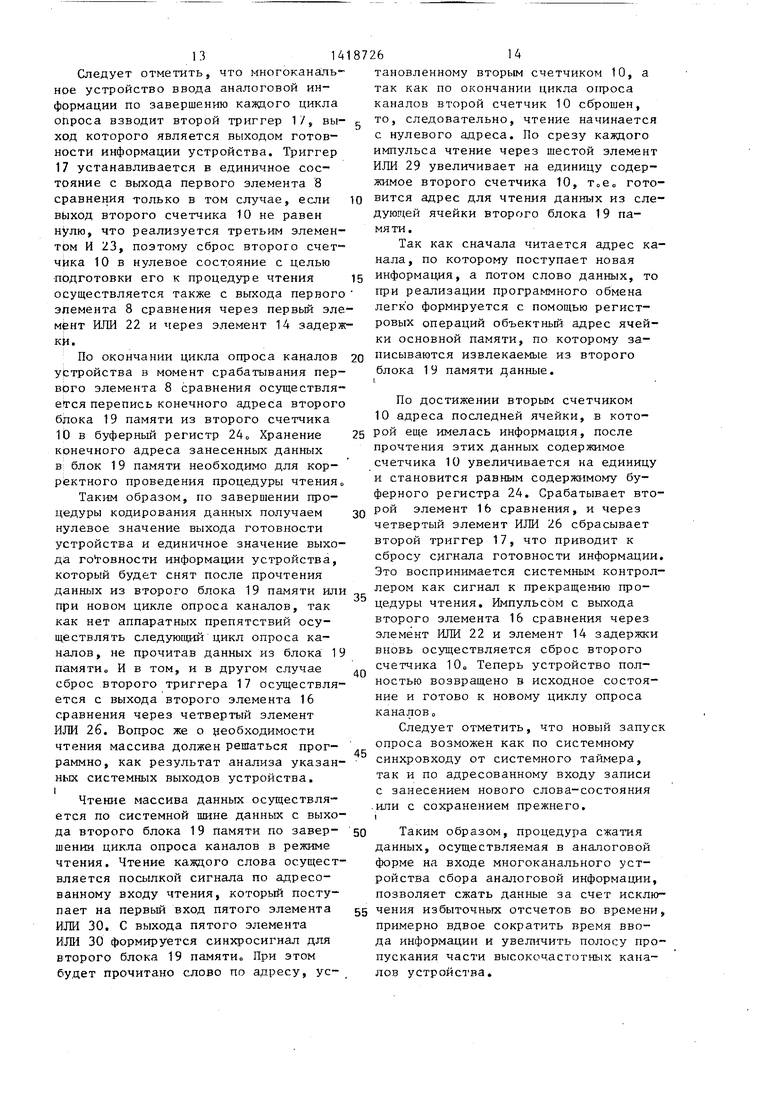

На фиг.1 приведена схема многоканального устройства ввода аналоговой информации; на фиг.2 - схема блока синхронизации; на фиг.З - схема блока анализа приращений сигнала; на фиг.4 - блок тсхема алгоритма, поясняющая работу устройства в процессе кодирования; на фиг.5 - блок-схема алгоритма работы устройства в процес се чтения.

Многоканальное устройство для ввода аналоговой информации (фиг.1) содержит первьй коммутатор 1, аналого-цифровой преобразователь 2, блок 3 анализа приращений-сигнала, цифро- аналоговьй преобразователь 4, первый блок 5 памяти, второй коммутатор 6, первьй счетчик 7, первьй элемент 8 сравнения, первьй элемент И 9, второ счетчик 10, блок 11 синхронизахщи, первый триггер 12, компаратор 13s элмент 14 задержки, второй элемент ИЛИ 15, второй элемент 16 сравнения, второй триггер 17, генератор 18 импульсов, второй блок 1.9 памяти, регистр 20 состояния, второй элемент И 21, первый элемент ИЛИ 22, Т1)етий элемент И 23, буферный регистр 24, третий элемент ИЛИ 25 четвертьй эле мент ИЛИ 26.

с

Q

j 0

5 о .

5

Блок 11 синхронизации содержит (фиг.2) седьмой элемент ИЛИ 27, второй распределитель- 28 импульсов, шестой элемент ИЛИ 29, пятый элемент ИЛИ 30, третий триггер 31, первьй распределитель 32 импульсов, четвертый элемент И 33, пятьй элемент И 34, шестой элемент И 35.

Блок 3 анализа приращений сигнала содержит (фиг.З) операционный усилитель 36, пороговый элемент 37, эм- митерный повторитель 38, узел 39 согласования уровней сигнала, элемент 40 памяти. I

Устройство работает следующим образомо

Входные аналоговые сигналы через коммутатор 1 последовательно во времени поступают на вход аналого-цифрового преобразователя 2 и на первьй вход блока 3 анализа приращений сигнала, на второй аналоговьй вход которого через цифроаналоговьй преобразователь 4 поступает в аналоговой форме значение сигнала по опрашиваемому каналу, полученное в предьщущем цикле опроса. Блок анализа приращений сигнала вьшолняет функцию контроля изменения сигнала на входе опрашиваемого канала. Так как последовательно включенные операционный усилитель 36 и эммитерньй повторитель 36 охвачены глубокой отрицательной обратной связью, то сигнал на выходе эммитер- ного повторителя 38 полностью соответствует сигналу на неинвертирукядем входе операционного усилителя 36, Соответственно потенциалы на базах выходньк транзисторов эммитерного

3141

повторителя с плавающим входом равны .

и; UBX + и; ;

uj Ue. - и;.

где и-„ - напряжение на неинвертиОл

рующем входе операционного усилителя Зб;

и, ,U,g- - соответственно напряжения эммитер-база верхнего и нижнего выходных транзисторов эммитерного повторителя .

Напряжения U и U являются установочными потенциалами для порогового элемента 37, Схема порогового элемента с зоной нечувствительности состоит из резисторов, диодного ключа и инвертирующего усилителя. Вход порогового элемента 37 является вторым аналоговым входом блока 3 анализа приращений. Принимая во внимание тот факт, что и U, для порогового элемента с зоной нечувствительности справедливы соотношения

и

и

-Si RO - Ил

S

где А и В - ширина зоны нечувствительности в вольтах для напряжений на втором аналоговом входе блока 3 анализа приращений сигнала и соответственно больших и меньших величины Ug. Например, если (Uj ) (.Ug. ) 0,6 в, а R,, то (А)(В)30 мВ, т.е пороговый элемент с зоной нечувствительности 37 не реагирует на разницу значений сигналов на первом и втором аналоговых входах блока 3 анализа приращений сигнала в диапазоне + 30 мВ. Это происходит от того, что пока разница входных сигналов невелика, ток через резистор R, меньше тока управления диодным ключом и, спе довательно, ток обратной связи, кото рый замыкается через диодный клим, обеспечивает глубокую отрицательную обратную связь инвертирующего усилителя, а напряжение на его выходе мало отличается от напряжения на потенциальном входе порогового элемента с зоной нечувствительности Но как

6

только ток обратной связи вследствие возрастающего разбаланса на аналоговых входах блока 3 анализа приращеьнй сигнала начинает приближаться и превышать управляющий ток диодного ключа, происходит разрыв обратной связи инвертирующего усилителя порогового элемента 37, что при достаточно высоком коэффициенте усиления усилителя приводит к резкому возрастанию напряжения на его выходе, вплоть до напряжения источников питания „ В зависимости от алгебраического значения разбаланса сигналов напрй ение на выходе порогового элемента 37 с зоной нечувствительности близко к значению напряжения положительного или отрицательного источника питания.

Узел 39 согласования уровней сигнала позволяет привести разнополяр- ньш выходной сигнал порогового элемента 37 к стандартному сигналу одной полярности. Резистором Rj устанавливается уровень срабатывания узла, так как например, при диапазоне аналоговых сигналов устройства +10 В и напряжении питания инвертирующего

усилителя порогового элемента с зоной нечувствительности +15 В узел согласования уровней должен срабатывать в диапазоне +10 15 В или 10 - -15 В, Выходной сигнал узла 39 согласования

уровней сигналов поступает на элемент 40 памяти. Запись в элемент 40 памяти происходит сигналом по синхровходу блока 3 анализа приращений сигнала. Выход элемента 40 памяти является

управляющим выходом блока 3 анализа приращений сигнала.

Таким образом, состояние управляющего выхода блока 3 анализа приращений сигнала соответствует соотноше-

нию аналоговых сигналов на его первом и втором аналоговых входах на момент прихода сигнала по синхровходуо Если разница между аналоговыми сигналами превысила допустимый уровень, то на

управляющем выходе блока анализа приращения сигналов будет логическая единица, в противном случае - логический нуль

Выход блока 3 анализа приращений

сигнала разрешает (или не разрешает) ,

работу второго коммутатора о и осуществление запуска аналого-цифрового .преобразователя 2. Если разница в сигналах по опрашиваемому сигналу в

5U

настоящий момент и в момент предыду- щего кодирования в пределах допуска, to аналого-цифровой преобразователь 2 не кодирует, а устройство переходит к опросу следующего канала. Если же разница в сигналах превышает уста.нов- ленный допуск, то аналого-цифровой преобразователь 2 осуществляет координирование сигнала, результат кодирования записывается в первый блок 5 памяти, где он обновляет хранящуюся информацию о сигнале по данному каналу, затем во второй блок 19 памяти последовательно заносят адрес опращи- ваемого канала и результат кодирования по каналу Внешнее устройство прочитывает собранную информацию из второго блока 19 памяти. Причем каждое слово данных сопровождается адресом канала, по которому оно получено Если изменений сигнала от момента предыдущего цикла опроса не произошло, то новых данных во второй блок 19 памяти по таким каналам не

заносится. I

Такая логика работы многоканального устройства ввода аналоговой информации обеспечивается следующим образом. Сигналом начальной установ ки обеспечивается сброс в нулевое состояние буферного регистра 24, регистра 20 состояния, через элемент ИЛИ 26 второго триггера 17, через элемент ИJM 22 первого триггера 12 и через элемент ИЛИ 27 третьего триггера 31, Выход первого триггера 12 информирует внешнее устройство о готовности измерительной части устройства ввода аналоговой информации. Нулевое состояние выхода триггера 12 свидетельствует об отсутствии процесса ввода данных, осуществляемого измерительной частью устройства. Выход второго триггера 17 показывает состояние второго блока 19 памяти. Единичный выход триггера 17 свидетельствует о наличии во втором блоке 19 памяти несписанной информации после очередного цикла опроса. Выходы триггеров 12 и 17 в системе могут быть использованы как инициаторы прерываний или выходы регистра состояния при асинхронном программном обмене.

Б рабочее состояние многоканальное устройство ввода аналоговой информации приводится записью в регистр 20 состояния слова-состояния устройства. При этом при системной шине

87266

данных в регистр 20 состояния записывается единица в старший разряд, адрес канала, до которого должен осус ществляться опрос источников в цикле, адрес первого канала опроса в цикле. Следовательно, устройство позволяет устанавливать число опрашиваемых ка-. налов в цикле в пределах физически

0 существующих каналов коммутатора 1 аналоговых сигналов В регистр 20 состояния информация с системной шины данных записывается по переднему фронту адресованного системного синх5 роимпульса Запись Срезом этого же импульса через элемент ИЛИ 25 осуществляется перепись из регистра 20 состояния в первьй счетчик 7 адреса первого канала в 1щкле опроса. При0 чем с выхода первого триггера 12 в момент параллельной записи счетчик 7 удерживается в режиме параллельной записи. Таким образом, слово-состояние, заносимое в регистр 20 состоя5 ния, состоит из трех частей: старший бит - рабочее состояние измеритель- ,ной части устройства; группа битов, соответствующая второму выходу регистра 20 состояния - адрес первого

3Q канала в цикле опроса; группа битов, соответствующая третьему выходу регистра 20 состояния - адреса канала с номером на единицу больше, чем адрес последнего канала в цикле опроса

35 После записи слова-состояния в регистр 20 состояния старшим битом слова-состояния с первого выхода регистра 20 разрещается запуск генератора 18 импульсов через элемент И 21

40 системных синхроимпульсов, которыми стробируется запуск цикла опроса каналов устройством. Импульсы с генератора 18 импульсов поступают на чет- вертьм 33 и пятьш 34 элементы И блока

45 11, но, так как третий триггер 31 предварительно установлен в нулевое состояние5 импульсы с генератора 18 импульсов приходят только на выход четвертого элемента И 33 и, следова50 тельно, поступают на вход первого распределителя 32 импульсов Сигнал с первого выхода первого распределителя 32 импульсов блока 11 поступает на синхровход коммутатора 1 и

155 через второй элемент ИЛИ 15 на синхровход первого блока 5 памяти. Следует отметить, что поскольку перед этим в первый счетчик 7 параллельно записан адрес первого канала в цикле

11 1

второй элемент ИЛИ 15 (.по фронту) осуществляется запись данных с выхода аналого-цифрового преобразователя 2 в адресованную ранее с выхода первого счетчика 7 ячейку памяти первого блока 5 памяти. Кроме того, по- тен1щальный сигнал Конец кодирования окончательно разблокировывает пятый элемент И 34, и тактовые им- ;пульсы начинают поступать на вход второго распределителя импульсов 28. Следует отметить, что второй коммутатор 6 адресуется с третьего выхода второго распределителя 28 импульсов. Поэтому, после поступления разрешающего потенциала с управляющего выход блока 3 анализа приращений сигнала и наличия нулевого потенциала на входе второго коммутатора 6, к выходу оказывается подключенным его вход, к которому подсоединен выход первого счетчика 7, т.е. на выходе второго коммутатора 6 в данный момент оказывается адрес опрашиваемого канала. Импульсом с первого выхода второго распределителя импульсов 28 через пятьй элемент ИЛИ 30 во второй блок 19 памяти заносится адрес опрашиваемого канала. При этом адрес ячейки блока 19 памяти устанавливается с выхода второго счетчика 10. Если это быпо первое занесение в цикле опроса после начальной установки, то адрес ячейки будет нулевым Сигналом со второго выхода второго распределителя 28 импульсов через шестой элемент И 29 по счетному входу второго счетчика 10 его содержимое увеличивается на единицу, во втором блоке 19 памяти адресуется уже следующая ячейка. Сигналом с третьего выхода второго распределителя 28 импульсов изменяется адресация второго коммутатора 6, который теперь переключается на шину данных с выхода аналого-цифрового преобразователя 2. Кроме того через пятый элемент ИЛИ 30 формируется синхросигнал на входе второго блока 19 памяти, что приводит к записи данных из аналого-цифрового преобразователя 2 во второй блок 19 памяти по адресу на единицу больше, чем записанный ранее адрес опрашиваемого канала. Сигнапом с четвертого выхода второго распределителя 28 импульсов через шестой элемент ИЛИ 29 содержимое счетчика 10 увеличивается на единицу, что является подготовкой

872612

адреса следуклцей ячейки блока 19 памяти для возмо;кной в дальнейшем записи адреса канала и результатов ко- г дирования при опросе одного из последующих каналов устройства. Этим же сигналом через седьмой элемент ИЛИ 27 осуществляется сброс третьего триггера 31J что приводит к переключению

0 выхода генератора 18 импульсов с работы на второй распределитель 28 импульсов на работу на первый распределитель 32 импульсов. Кроме того, вновь разблокировывается шестой эле-

5 мент И 35 и вновь меняется режим работы Первого блока 5 памяти. Сигналом с четвертого выхода первого распределителя 32 импульсов происходит увеличение содержимого первого счет0 чика 7, и далее схема переходит к работе по опросу следующего канала системы ввода аналоговых данных.

Опрос каждого из каналов может происходить по укороченному варианту,

5 который бьш описан ранее i-ши согласно выше описанному удлиненному вари- ,анту, когда выполняется кодирование данных.

Следует отметить, что адресация

0 первого блока 5 памяти осуществляется синхронно и синфазно с адресацией каналов устройства. А адресация второго блока 19 памяти осуществляется инкрементно, начиная с нулевого адреса, по мере поступления данных с выхода аналого-цифрового преобразователя 2. Причем на запись каждого результата кодирования используется две ячейки памяти В ячейку с -четным номером заносят адрес опрашивае0

5

0

5

мого канала, по которому проводилось кодирования информации, а в последующую ячейку с нечетным номером записывается результат кодирования данных. При этом, так как кодирование, происходит только по тем каналам, где разница с результатом предшествующего кодирования превьшшет допуск, то во второй блок 19 памяти данных может оказаться занесено гораздо меньше, чем опрошено, каналов в цикле. Может оказаться, что кодирование не осуществлялось ни по одному из опрашиваемых каналов, т.е был пустой цикл опроса, как это было описано ранее. В этом случае второй счетчик 10 сохраняет нулевой выход в конце цикла опроса, что фиксируется компаратором 13.

131А1872614

Следует отметить, что многоканаль-тановленному вторым счетчиком 10, а нре устройство ввода аналоговой ин-так как по окончании цикла огфоса формации по завершению каждого циклаканалов второй счетчик 10 сброшен, опроса взводит второй триггер 17, вы- сто, следовательно, чтение начинается ход которого является выходом готов-с нулевого адреса. По срезу каткдого ности информации устройства. Триггеримпульса чтение через шестой элемент 17 устанавливается в единичное сое-ИЛИ 29 увеличивает на единицу содер- тояние с выхода первого элемента 8жимое второго счетчика 10, т„ео гото- сравнения только в том случае, если 10вится адрес для чтения данных из сле- выход второго счетчика 10 не равендующей ячейки второго блока 19 па- нулю, что реализуется третьим элемен-мяти.

том И 23, поэтому сброс второго счет™ Так как сначала читается адрес ка- чика 10 в нулевое состояние с цельюнала, по которому поступает новая подготовки его к процедуре чтения 15информация, а потом слово данных, то осуществляется также с выхода первого при реализации программного обмена элемента 8 сравнения через первьш эле-легко формируется с помощью регист- мёнт ИЛИ 22 и через элемент 14 задерж-ровых операций объектньм адрес ячейки,ки основной памяти, по которому заПо окончании цикла опроса каналов 20 исываются извлекаемые из второго

устройства в момент срабатывания пер-блока 19 памяти ;анные. вого элемента 8 сравнения осуществля™

ется перепись конечного адреса второго По достижении вторым счетчиком

блока 19 памяти из второго счетчика адреса последней ячейки, в кото10 в буферный регистр 24« Хранение 25РОЙ еще имелась информация, после

конечного адреса занесенных данныхпрочтения этих данных содержимое

в блок 19 памяти необходимо для кор- .счетчика 10 увеличивается на единицу

рёктного проведения процедуры чтения о становится равным содержимому буТаким образом, по завершении про-Ферного регистра 24. Срабатывает вто- цедуры кодирования данных получаем ЗОР° элемент 16 сравнения, и через нулевое значение выхода готовностичетвертый элемент ИЛИ 26 сбрасывает устройства и единичное значение выхо-второй триггер 17, что приводит к да го говности информации устройства,сбросу сигнала готовности информации, который будет снят после прочтенияЭто воспринимается системным контрол- данных из второго блока 19 памяти илилером как сигнал к прекращению пропри новом цикле опроса каналов, такцедуры чтения. Импульсом с выхода как нет аппаратных препятствий осу-второго элемента 16 сравнения через ществлять следующий цикл опроса ка-элемент ИЛИ 22 и элемент 14 задержки налов, не прочитав данных из блока 19вновь осуществляется сброс второго памяти И в том, и в другом случае счетчика 10„ Теперь устройство пол- сброс второго триггера 17 осуществля-ностью возвращено в исходное состоя- ется с выхода второго элемента и готово к новому циклу опроса сравнения через четвертый элементканалов„

ИЛИ 26. Вопрос же о необходимости Следует отметить, что новый запуск

чтения массива должен решаться прог- опроса возможен как по системному

раммно, как результат анализа указан- синхровходу от системного таймера,

ных системных выходов устройства.так и по адресованному входу записи

Iс занесением нового слова-состояния

Чтение массива данных осуществля- сохранением прежнего,

ется по системной шине данных с выхо-i

да второго блока 19 памяти по завер- 50 Таким образом, процедура сжатия

шении цикла опроса каналов в режимеданных, осуществляемая в анапоговой

чтения. Чтение кавдого слова осущест-форме на входе многоканального уствляется посылкой сигнала по адресо-ройства сбора аналоговой информации,

ванному входу чтения, который посту-позволяет сжать данные за счет исклю- пает на первый вход пятого элемента gg чения избыточных отсчетов во времени,

ИЛИ 30. С выхода пятого элементапримерно вдвое сократить время ввоИЛИ 30 формируется синхросигнал дляда информации и увеличить полосу проBiToporo блока 19 памяти При этомпускания части высокочастотных канабудет прочитано слово по адресу, ус-лов устройства.

7

опроса, а выход первого счетчика 7 поступает на адресные входы коммутатора 1 и первого блока .5 памяти, то по .сигналам с первого выхода первог распределителя 32 импульсов происходит коммутация адресованного канала и считывание из одноименной каналу ячейки блока 5 памяти в цифроаналог вый преобразователь 4 слова данных, т.е. первый блок 5 памяти в этот момент с выхода третьего триггера 31 удерживается в режиме чтения В процессе выполнения указанных операций аналоговый сигнал адресованного кан ла поступает на вход аналого-ци(3)ро- вого преобразователя 2 и на первый вход блока 3 анализа приращений сигнала. В то же время на второй вход блока 3 анализа приращений сигнала с выхода цифроаналогового преобразователя 4 поступает аналоговый эквивалент слова данных, прочитанного из ячейки памяти первого блока 5 памяти с одноименным адресом, что и замкнутый канал коммутатора 1. Чере интервал времени, достаточный для завершения переходных процессов в целях аналоговых сигналов, импульсо с второго выхода первого распредели теля 3Z импульсов осуществляется стробирование элемента 40 памяти блока 5 анализа приращений сигнала,, При этом на выходе блока 3 анализа приращений сигнала фиксируется соотношение входного аналогового сигнал на данный момент времени и его значения в предьщущий момент отсчета. Если разница между сигналами находися в пределах установленного допуск то на управляющем входе блока 3 анализа приращений сигнала фиксируется нулевое значение, в противном случае - единичное.

Выход блока 3 анализа приращений сигнала поступает на разрешающие входы коммутатора 6 и первого элемента И 9 и определяет дальнейшую

работу схемы, г

С незначительным интервалом врем ни на третьем выходе первого распределителя 32 импульсов вьфабатывает- ся управляющий импульс, который поступает на второй вход первого элемета И 9 и на S-вход первого триггера 12. Вне зависимости от состояния управляющего выхода блока 3 анализа приращений сигнала первьй триггер 1 будет приводиться в единичное состоя

, 5 0 5 О

0 5

5

0

5

ние и, следовательно, изменяется потенциал на выходе готовности устройства, что свидетельствует о нахожде- ::ии измерительной части устройства в состоянии функционирования изменяется режим работы первого счетчика 7, который переходит в счетный реж1-1м. Второй блок 19 памяти по входу режима работы переводится в режим записи, на входы пятого 34 и шестого 35 элементов Н поступает разрешаюш 1Й потенциал, который подготавливает эти элементы для предстоящих тактов работы устройства, разрешающий потенциал поступает на первый элемент И 9, Через первый элемент И 9 скол импульса с третьего выхода первого распределителя 32 импульсов проходит в зависимости от состояния выхода блока 3 анализа приращений сигнала. Если . на первом входе элемента И 9 нулевой потенциал, то сигнал на его выход не проходит и, следовательно, не влияет на дальнейшую работу устройства В этом случае последующим сигналом с четвертого выхода первого распределителя 32 импульсов через шестой элемент И 35, который подготовлен уже потенциалами с выходов первого 12 и третьего 10 триггеров, заносится единица на счетный вход первого счетчика 7 Это приводит к изменению адреса на адресных входах коьмутатора 1 и первого блока 5 памяти. Поскольку , в дальнейшем первьй распределитель 32 импульсов работает, начиная вновь с первого входа, то описанньм тцикл работы устройства повторяется вновь, но уже с другим адресом канала, который на еди1гицу больше предыдущего, Если в процессе работы устройства при опросе в.сех каналов вход первого элемента И 9 так и остается заблокированным управляющим выходом блока 3 анализа приращений сигнала, то через установленное число таких коротких циклов на выходе первого счетчика 7 устанавливается адрес, равный адресу, записанному во вторую группу битов регистра 20 состояния. Этот факт выявляется первым элементом 8 сравнения, сигналом с выхода которого через первый элемент ИЛИ 22 сбрасывается первьй триггер 12 и осуществляется сброс ряда других элементов, которые в описанном пустом цикле опроса каналов не работали, и поэтому сигнал сброса, вьфаботанный первым

9 1

элементом 8 сравнения, лишь подтверждает их ранее установленное состояние. Триггер 12 вновь переводит первый счетчик 7 в режим параллельной записи, меняет сигнал на выходе готовности устройства, блокирует пятый 34 и шестой 35 элементы И, но не останавливает работу первого распределителя 32 импульсов. Следующий запуск цикла работы устройства может осуществляться по системному синхро- входу от таймера через второй элемен И 21 и третий элемент ИЛИ 25, так как содержание регистра состояния 22 сохраняется и второй элемент И 21 разблокировывается с выхода старшего разряда регистра 20. Повторньш запуск может быть осуществлен и путем записи нового слова-состояния в регистр 20 состояния, .Следует подчеркнуть, что адресный режим работы устройства обеспечивается записью слова-состояния, в котором в качестве адреса первого канала в цикле записывается адрес адресуемого канала, а в качестве ад,реса канала, до которого должен длиться цикл, записывается адрес на единицу больше. В этом случае после опроса одного канала происходит останов устройства и возврат его в начальное состояние Следует также отметить, что асинхронный режим работы системного синхровхода и генератора, импульсов, который определяет работу первого распределителя 32 импульсов, не приводит к сбойной ситуации, так как установка нового адреса на выходе первого счетчика 7 происходит на четвертом также распределителя 32, а установка первого триггера 12 происходит на третьем такте. Поэтому несвоевременные попытки опрокинуть первый триггер 12 на на третьем такте работы первого распределителя 32 импульс9В и начать новый цикл опроса каналов до прихода системного синхроимпульса и осуществления параллельной записи в счетчик 7 начального адреса не увенчиваются успехом,,так как первый триггер 12 удерживается в сброшенном состоянии с выхода первого элемента 8 сравнения потенциально до тех пор, пока на входах первого элемента 8 сравнения не появятся разные кодовые комбинации, т.е, до параллельной записи в первый счетчик 7 начального адреса Как следствие, первый элемент И 9

2610

заблокирован и сигнал на его выходе, приводящий к запуску аналого-цифрового преобразователя 2 и к установке

третьего триггера 31 , не появляетсяе,

Следовательно, несмотря на то, что после завершения цикла работы устройства генератор 18 импульсов и первый распределитель 32 импульсов

продолжают работать, сбойной ситуации не возникает, так как асинхронное поступление системного синхроимпульса синхронизируется, а влияние выходов первого распределителя 32

импульсов на работу элементов устройства блокируется до прихода нового системного синхроимпульса или их поступление безразлично для элементов как, например, поступление в этот

период сигналов на синхровходы коммутатора 1 и блока 3 анализа приращений сигнала.

Для синхронизации системного синхроимпульса и первого распределителя

импульсов 32 длительность системного синхроимпульса должна превышать цикл работы первого распределителя 32 импульсов., Системный синхроимпульс стробируется-сигналом с четвертого

выхода первого распределителя 32 импульсов на втором элементе И 21 Поэтому параллельная запись канального адреса, в цикле опроса происходит перед новым циклом работы первого распределителя 32 импульсов о

Если в процессе опроса каналов устройства на выходе блока 3 анализа приращений сигнала появляется единичный потенциал, то он сигналом с третьего выхода первого распределителя импульсов через разблокированный первый элемент И 9 (или скол сигнала при опросе первого канала в цикле) поступает на вход запуска аналого- цифрового преобразователя 2 и на установочный вход третьего триггера 31, который переходит в единичное состояние. Единичное состояние третьего триггера 31 блокирует четвертый 33 и шестой 35 элементы И, подготавливает

к отпиранию пятый элемент И 34, и меняет режим работы первого блока 5 памяти, который из режима чтения переходит в режим записио Несмотря на работу генератора 18 импульсов, схема устройства переходит в режим ожидания до прихода сигнала конца кодирования с аналого-цифрового преобразователя 2о Этим сигналом через

15

Формула изобретения

10

15

20

55

1872616

выход конца преобразования аналого- цифрового преобразователя соединен с первым входом второго элемента ИЛИ и вторым входом блока синхронизации, выход второго элемента соединен с синхровходом первого блока памяти, первьй выход блока синхронизации соединен с синхровходом первого коммутатора и вторым входом второго элемента ИЛИ, второй выход - с синхровходом блока анализа приращений сигнала, третий выход - с входом чтения- записи первого блока памяти, четвертьй выход - с вторым входом первого элеме нта И и входом установки в 1 первого триггера, пятый выход - с счетным входом второго триггера, щес- той выход - с вторым управляющие входом второго ком гутатора, седьмой вы- ход - с синхровходом второго блока

5

0

5

5

0

5

0

памяти, восьмой выход - с первым входом второго элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с синхровходом первого счетчика, счетньй вход которого подключен к девятому выходу блока синхронизации, выход первого триггера соединен с управляющим входом первого счетчика, третьим входом блока синхронизации, третьим входом первого элемента И, входом чтения-записи второго блока памяти и является выходом готовности устройства, выход первого элемента ШШ соединен с входом сброса первого триггера, выход элемента задержки соединен с входом сброса второго счетчика, выходы которого соединены с адресными входами второго блока памяти, входами компаратора, информационными входами буферного регнст- ра и входами первой группы второго элемента сравнения, входы второй группы которого соединены с выходами буф-зрного регистра, выходы второго коммутатора соединены с информационными входами второго блока памяти, выходы которого являются информационными выходами устройства, входы сброса регистра состояния и буферного регистра, первые входы четвертого и первого элементов ИЛИ и четвертьй вход блока синхронизации являются входом сброса устройства, выход второго элемента сравнения соединен с вторым входом четвертого и первого элементов ИЛИ, выход первого элемента сравнения соединен с третьим вхо

дом первого элемента ИЛИ, синхровхо- дом буферного регистра и первым входом третьего элемента И, выход которого соединен с входом установки в 1 второго триггера, выход которого является выходом готовности информации устройства, выход четвертого элемента ИЛИ соединен с входом сброса второго триггера, выход компаратора соединен с вторым входом третьего элемента И, выходы второй группы ре- тистра состояния соединены с входами ;второй группы элемента сравнения, выход регистра состояния соединен с вторьи входом второго элемента И и . входом запуска генератора импульсов, ;выход которого соединен с пятым входом блока синхронизации, третий вход второго элемента И является синхро- входом устройства, синхровход регистра состояния и второй вход третьего ;элемента ИЛИ являются входом записи ;устройства, шестой вход блока синхронизации является входом чтения устройства, причем блок синхронизации содержит третий триггер, первый и второй распределители импульсов, четвертый, пятьш и шестой элементы Hj пятый, шестой и седьмой элементы ИЛИ, вход установки в 1 третьего триггера является первым входом блока синхронизации, прямой выход кото- :рого соединен с первыми входами четвертого, пятого и шестого элементов И и является третьим выходом блока , синхронизации, вторые входы четвертого и пятого элементов И являются пятым входом блока синхронизации, выход четвертого элемента И соединен с входом первого распределителя импульсов, первьш, второй и третий выходы которого являются соответственно первым, вторым и четвертым выходами блока синхронизации, четвертый выход первого распределителя импульсов соединен с вторым входом шестого элемента И и является восьмым выходом блока синхронизации, выход шестого элемента И является девятым выходом блока синхронизации, третий вход пятого элемента И является вторым

5

0

5 0

0

5

0

5

входом блока синхронизагдаи, четвертый вход элемента И и третий вход шестого элемента И является третьим входом блока синхронизации, выход пятого элемента И соединен с входом второго распределителя импульсов, первый вход которого соединен с первым входом пятого элемента ИЛИ, выход которого является седьмым выходом блока синхронизации, второй выход второго распределителя импульсов соединен с первым входом шестого элемента ИЛИ, выход которого является пятым выходом блока синхронизации, третий выход второго распределителя импульсов соединен с вторым входом пятого элемента ИЛИ и является шестым выходом блока синхронизации, четвертьш выход второго распределителя импульсов соединен с вторым входом шестого элемента ИЛИ и первым входом седьмого элемента ИЛИ, второй вход которого является четвертым входом блока синхронизации, выход седьмого элемента ИЛИ соединен с входом сброса третьего триггера, третьи входы пятого и шестого элементов ИЛИ являются шестым входом блока синхронизации.

Фиг: 2

)

--g-

janucb с АО ось - состояния

±L

Устаноока наяального а арка канала

коммутация канала, записьо ЦАП данные от опроса да.ниоео канала Ь предыдущем 14икж

±

Опрос блока анализа приращении сигнала. установка дзла триееера

/Состояние Выхода анаАиза приращении

Приращение канала устройства

Нет

Конец цикла у

Устано8на системного сигнал Готовность измерительной системы

Анализ состояния aS- ресноео сметчика. мка, памяти

1

Aa/Mspfi i3HUe адресн.сч §лока памяти

jT

дстаноЗка системное сиенала Готодность массиоа ванны)

Да

1

BySem ли новый опроса, кцниАоВ

от

Запись ноЗоео сАо8а -состолния

1

Запуск АЦП I

™Г

Запись pesijAbmama кодира- дания S 1-ыи SAOK памяти

оммутация мультиплексора

JL

Запись до Второй блок па - мята адреса onpouiitScL- емоео канала

L

KoMMymau ufl мульгли/и ексо- ра и модификация адреса 2-80 лока ломя mi/

±

Запись So 2-ой SAOK памяти

I

Модидзикацил адреса 2-е0 SAQKQ памяти

Нет

1

)(ранениёмасси8а онны)

j----

СНднец J

Фт.

С Начало }

Чтение слобо (адреса ) иу dmoposo блока памяти

Автоинкрементная модификация адреса Второго блока памяти meнue слоЗа (данные) из Smopo- го блока памяти.

Ьтоинкрементнал модификация адреса Второго 5лока памяти

Нет /Последний адрес 8 нассиВБ Да информации /

СЬрос сигнала, ТотоВность- массива данных , о1 н1/лр- ние адресного су.-ео блока ламяти

Фив. 5

С оищ }

| 0 |

|

SU402865A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-22—Подача