импульсов, выход счетчика импульсов подключен к информационным входам регистров группы, входы разрещения записи которых соединены с дополнительными входами элементов И всех функциональных узлов блока управления и подключены к выходам компараторов группы, первью входы которых через первый цифроаналоговый преобразователь соединены с выходом счетчика, вторые входы компараторов груп пы являются первой группой информационнь1х входов процессора, выходы регистров группы соединены с информационными входами шинных формирователей, управляющие входы которых подключены к второй группе выходов пифратора блока управления, выходы шинных формирователей соединеьш с

0375

входами выборки постоянного запоминающего устройства, шины задания адреса выборки которого подключены к второй группе выходов шифратора блока управления, выходы постоянного запоминающего устройства соединены с информационными входами блока памяти, информационные выходы которого через первый коммутатор соединены с входами блока умножения, выходы которого соединены с первой группой входив второго цифроаналогового преобразователя, вторая группа входов которого является второй группой входов процессора, выходы второго цифроаналогового преобразователя соединены с входами сумматора, выход которого через второй коммутатор подключен к входам блока памяти аналоговых сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| Устройство для ввода информации | 1983 |

|

SU1124274A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Устройство для вычисления углеродного потенциала | 1984 |

|

SU1257660A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство контроля параметров | 1990 |

|

SU1800447A1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРОЦЕССОР, содержащий блок управления, первая группа выходов которого соединена с управляющими входами первого и второго коммутаторов, блок памяти аналоговых сигналов, первый цифроаналоговый преобразователь, блок памяти, шины задания адреса которого подключены к второй группе выходов блока управления, отличающийся тем, что, с целью повьше- . ния быстродействия, в него дополнительно введены генератор тактовых импульсов, счетчик, второй дифроаналоговый преобразователь,группа компараторов, группа регистров, группа шинных формирователей, постоянное запоминающее устройство, блок умножения, сумматор, а блок управления выполнен в виде R5 -трипера, первого и второго элементов И, формирователя импульсов, счетчика, элемента ИЛИ-НЕ, шифратора и И функциональных узлов, каждый из которых содержит Э -триггер, R5 -триггер, блок задержки и элемент И, выход которого соединен с установочным входом D -триггера. синхронизирующий вход которого соединен с выходом блока задержки, инверсный выход Д -триггера соединен с установочным входом RS -триггера, выход ЧЗ-триггера соединен с первым входом элемента И, первая группа входов шифратора соединена с выходами счетчика, а вторая группа входов подключена к выходам RS -триггеров всех функциональных узлов и соединена с входами элемента ИЛН-НЕ, выход которого подключен к одному входу первого элемента И, другие входы которого соединены с выходами всех D -триггеров функциональных узлов, выход Первого элемента И подключен к входу формирователя импульсов, выход кото(Л рого соединен с входами сброса RSI триггеров функциональнькузлов и входом сброса R5-триггера,установочный вход которого подключен к выходу переполнения счетчика, счетный вход которого соединен с выходом второго элемента И, первый вход IND которого подключен к вьгходу R5 о триггера, второй вход второго элеменОО та И соединен с входами блоков за-vj держки всех функциональных узлов, выход D -триггера каждого функцион льел ного узла соединен с соответствукщими входами элементов И остальных функциональных узлов, первая и вторая группы выходов шифратора являются соответственно первой и второй группами выходов блока управления, причем выход R5 -триггера блока управления соединен с входом разрешения счета счетчика, счетный вход которого соединен с вторым входом второго элемента И блока управления и подключен к выходу генератора тактовых

Изобретение относится к вычислительной технике, в частности к гибридным вычислительным устройствам, и может быть использовано для реализации систем нелинейных уравнений в управляющих системах, например, манипуляционных роботов.

Известно вычислительное устройство, содержащее последовательно соединенные многоканальные аналого-цифровой преобразователь, микро-ЭВМ и цифроаналоговый преобразователь, которое Осуществляет обработку информа.ции с первичных преобразователей в цепи прямой и обратной связи и вычисление расчетных корректирующих воздействий lj .

Наиболее близким по технической сущности к изобретению является управляющий процессор, содержащий пре.образователь кода в напряжение, цифровой вход которого подключен через цифровой запоминающий блок к первому выходу блока управления, а вход опорного напряжения соединен с выходом коммутатора входных сигналов, управляющий вход которого подсоединен к второму выходу блока управления, одна группа входов коммутатора входных сигналов является группой входов процессора, а другая группа входов подключена к группе выходов аналогового запоминающего блока и группе выходов процессоров, коммутатор аналоговых сигналов, 1 групп из m накопительных сумматоров в каждой группе, )Т дополнительных коммутаторов, i информационных входов каждого из которых соединены с выходом одного из накопительных сумматоров,каждой группы, управляющие входы дополнительных

коммутаторов подключены к прямому выходу блока управления, а их выходы подсоединены к соответствукщим входам аналогового запоминающего блока, входы накопительных сумматоров подключекы к соответствующим выходам коммутатора аналоговых сигналов, управляюсций и информационный входы которого соединены соответственно с четвертым выходом блока управления и выходом преобразователя кода в напряжение 2. Недостатком известных устройств является низкое быстродействие.

Цель изобретения - повьшение быстродействия процессора.

Поставленная цель достигается тем, что в многоканальный аналогоцифровой процессор, содержащий блок управления, первая группа выходов которого соединена с управляющими

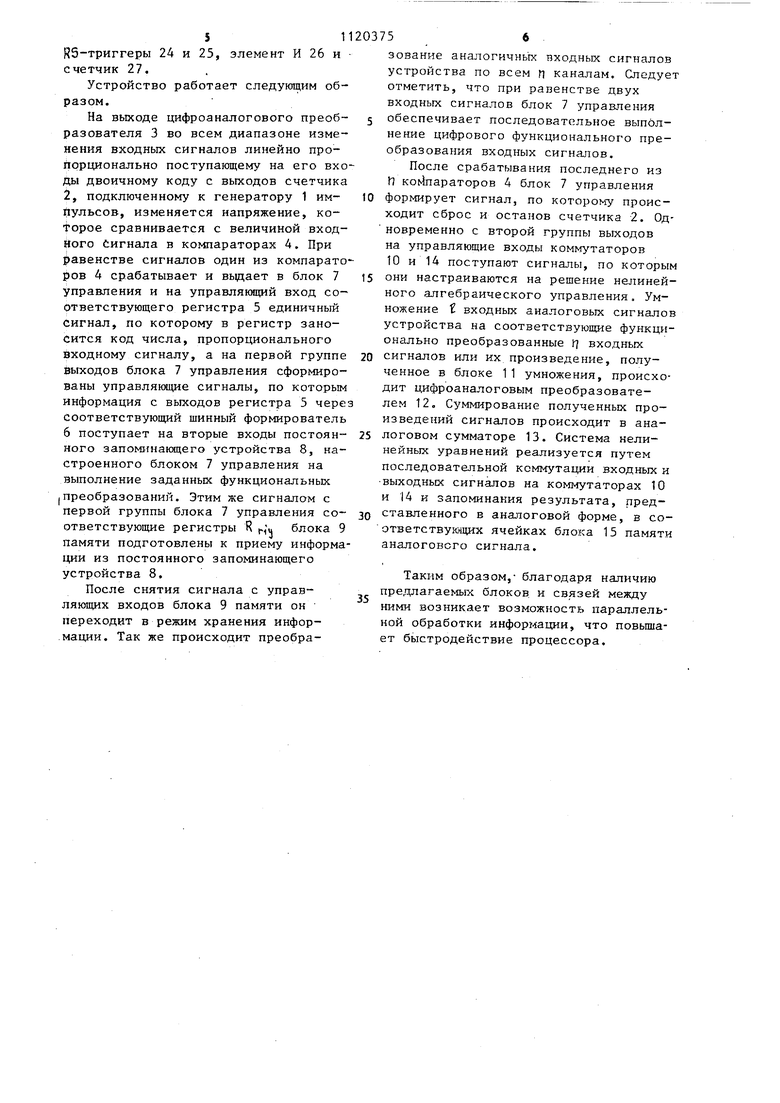

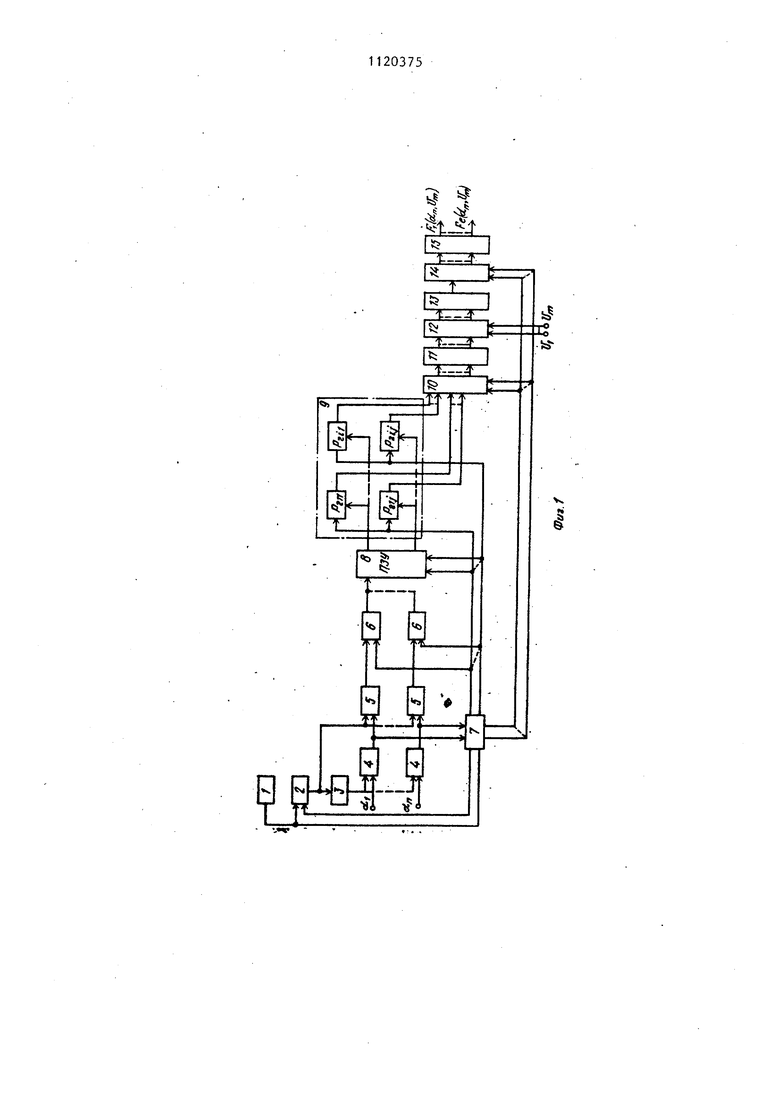

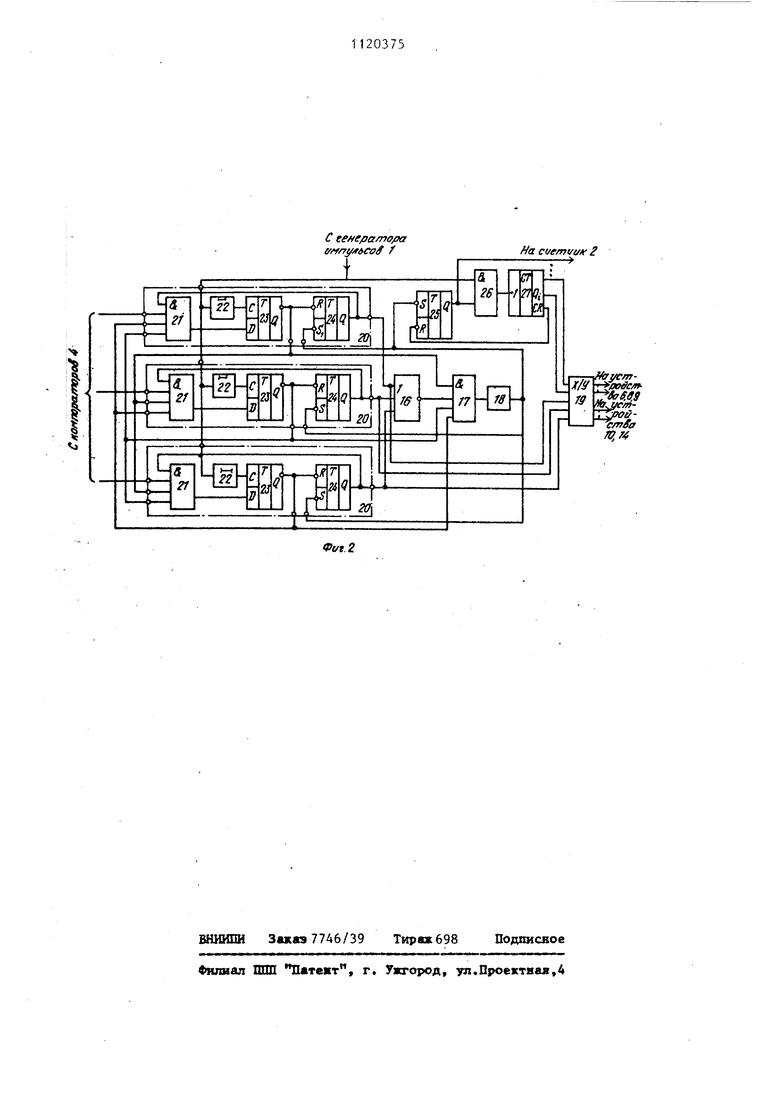

входами первого и второго коммутаторов, блок памяти аналоговых сигналов, первый цифроаналоговый преобразователь, блок памяти, шины задания адреса которого подключены к второй группе выходов блока управления,дополнительно введены генератор такто вых импульсов, счетчик, второй цифр анапоговьм преобразователь, группа .компараторов, группа регистров, гру па шинных формирователей, постоянно запоминающее устройство, блок умножения, сумматор, а блок управления вьтолнен в виде R5 -триггера, перво го и второго элементов И, формирова теля импульсов, счетчика, элемента ИЛИ-НЕ, шифратора и п функционал ных узлов, каждый из которых содерж D-триггер, R5 -триггер, блок задерж ки и элемент И, выход которого соединен с установочным входомD-триггера, синхронизирующий вход которого соединен с выходом блока задержки, инверсный выход D -триггера соединен с установочным входом R5 -три гера, выход R5 -триггера соединен с первым входом элемента И, первая группа входов шифратора соединена с выходами счетчика, а вторая группа входов подключена к выходам RS -триггеров всех функциональных узлов и соединена с входами элемента ИЛИ-НЕ вьга;од которого подключен к одному входу первого элемейта И, другие входы которого соединены с выходами всех D -триггеров функхщональных узлов, выход первого элемента И подключен к входу формирователя импульсов, выход которого соединен с входами сброса R5 -триггеров функциональных узлов и входом сброса RS триггера, установочный вход которого подключен к выходу переполнения счетчика, счетный вход которого соединен с выходом второго элемента И, первый вход которого подключен к выходу RS -триггера, второй вход второго элемента И соединен с входами блоков задержки всех функциональных узлов, выход D -триггера каждого функционального узла соединен с соответствующими входами элементов И остальных функциональных узлов, первая и вторая группы выходов шифратора являются соответственно первой и второй rpjmnaMH выходов блока управления, причем выход RS -триггера блока управления соединен с входом разрешения счета счетчика, счетный вход которого соединен с вторым входом второго элемента И блока управления и подключен к выходу генератора тактовых импульсов, выход счетчика импульсов подключен к информационным входам регистров группы, входы разрешения записи которых соединеньт с дополнительными входам элементов И всех функциональных узлов блока управления и подключены к выходам компараторов группы, первые входы которых через первый цифроаналоговый преобразователь соединены с выходок счетчика, вторые входы компараторов группы являются первой группой информационных входов процессора, выходы регистров группы соединены с информационными входами шинных формирователей, управляющие входы которых подключены к второй группе выходов шифратора блока управления, вькоды шинных формирователей соединены с входами выборки постоянного запоминающего устройства, щины задания адреса выборки которого подключены к второй группе выходов шифратора блока управления, выходы постоянного запоминающего устройства соединены с информационными входами блока памяти, информационные выходы которого через первый коммутатор соединены с входами блока умножения, выходы которого соединены с первой группой входов второго цифроаналогового преобразователя, вторая группа входов которого является второй группой входов процессора, выходы второго цифроаналогового преобразователя codдине ны с входами сумматора, выход которого через второй коммутатор подключен к входам блока памяти аналоговых сигналов. На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 - блок-схема блока управления. Устройство содержит генератор 1 импульсов, счетчик 2, цифроаналоговый преобразователь 3, компараторы 4, регистры 5, шинйые формирователи 6, блок 7 управления, постоянное запоминающее устройство 8, блок 9 памяти, вьшолненный в. виде регистра, коммутатор 10, блок 11 умножения, цифроаналоговый преобразователь 12, сумматор 13, коммутатор 14 и блок 15 памяти аналогового сигнала. Блок 7 управления (фиг.2) содержит элемент ИЛИ-НЕ 16, элемент И 17, формирователь 18 импульсов, шифратор 19, функциональные узлы 20, каждый из которых содержит элемент И 21, блок 22 задержки, С -триггер 23, 51 Р 5-триггеры 24 и 25, элемент И 26 и счетчик 27, Устройство работает следующим образом. На выходе цифроаналогового преобразователя 3 во всем диапазоне изменения входных сигналов линейно пропорционально поступающему на его вхо ды двоичному коду с выходов счетчика 2, подключенному к генератору 1 импульсов, изменяется напряжение, которое сравнивается с величиной входного Ьигнала в компараторах 4. При равенстве сигналов один из компарато ров 4 срабатывает и вьщает в блок 7 управления и на управляющий вход соответствующего регистра 5 единичный сигнал, по которому в регистр заносится код числа, пропорционального входному сигналу, а на первой группе выходов блока 7 управления сформированы управлякщие сигналы, по которым информация с выходов регистра 5 чере соответствующий шинный формирователь 6 поступает на вторые входы постоянного запомннакщего устройства 8, настроенного блоком 7 управления на выполнение заданных функциональных Iпреобразований. Этим же сигналом с первой группы блока 7 управления соответствующие регистры R блока 9 памяти подготовлены к приему информа ции из постоянного запоминающего устройства 8. После снятия сигнала с управляющих входов блока 9 памяти он переходит в режим хранения информации. Так же происходит преобра5зование аналогичньтх входных сигналов устройства по всем п каналам. Следует отметить, что при равенстве двух входных сигналов блок 7 управления обеспечивает последовательное выполнение цифрового функционального преобразования входных сигналов. После срабатывания последнего из П Koi lnapaTopoB 4 блок 7 управления формирует сигнал, по которому происходит сброс и останов счетчика 2. Одновременно с второй группы выходов на управляющие входы коммутаторов 10 и 14 поступают сигналы, по которым они настраиваются на решение нелинейного алгебраического управления. Умножение t входных аналоговых сигналов устройства на соответствующие функционально преобразованные 17 входных сигналов или их, произведение, полученное в блоке 11 умножения, происходит цифроаналоговым преобразователем 12. Суммирование полученных произведений сигналов происходит в аналоговом сумматоре 13. Система нелинейных уравнений реализуется путем последовательной коммутации входных и выходньЕх сигналов на коммутаторах 10 и 14 и запоминания результата, представленного в аналоговой форме, в соответствуклцих ячейках блока 15 памяти аналогового сигнала. Таким образом, благодаря наличию предлагаемых блоков, и связей между ними возникает возможность параллельной обработки информации, что повьшает быстродействие процессора.

С еенератора

ffffrry/fiCO /

Vi

На ct/emve/AT I

ycm poSe/ft f.y.9 ,j/cml u /rrffffЩГ4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бедржицкий Е.П | |||

| и др | |||

| Автоматизированная система управления комплексными прочностными исследованиями | |||

| - Электронная промышленность, 1979, № 11-12, с | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Управляющий процессор | 1977 |

|

SU711593A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-23—Публикация

1983-04-11—Подача