(54) УСТРОЙСТВО ДЯЯ РЕГИСТРАЦИИ ПОТОКА , ОШИБОК ДИСКРЕТНОГО КАНАЛА СВЯЗИ

1

Изобретение.относится к электросвязи и предназначено для исследования дискретных каналов связи.

Известно устройство для регистрации ошибок дискретного канала связи, соде{х- , жащее последовательно соединенньш формирователь команд, анализатор непораженных символов, выход которого подключен к первому, второму и третьему входам управляемого коммутатора, к первому уп- ю равляющему входу которого подключен первый выход блока управления записью и считыванием, а также счетчик ошибок, генератор тактов и блок регистрации ..

Однако известное устройство не обеспечивает поэлементную регистрацгоо потока ошибок в высокоскоростных сисфемах передачи данных.

Цель изобретения - повышение точное- 20 ти путем поэлементной регистрации потока ошибок в высокоскоростных системах передачи данных.

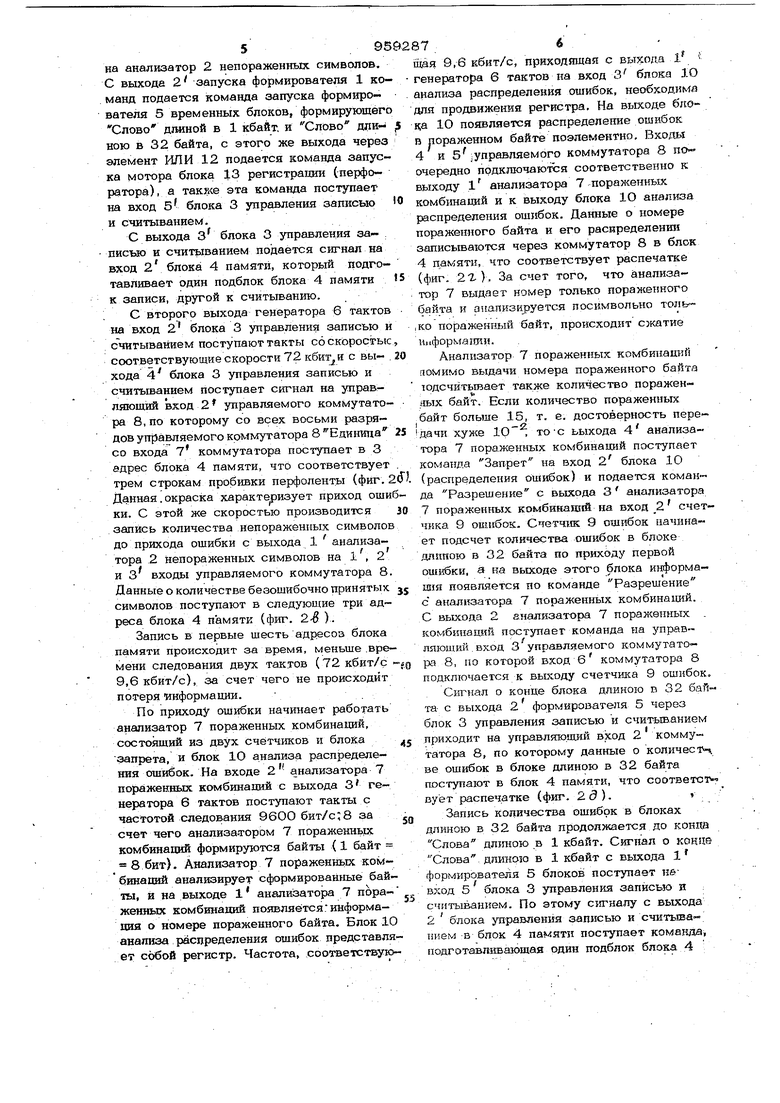

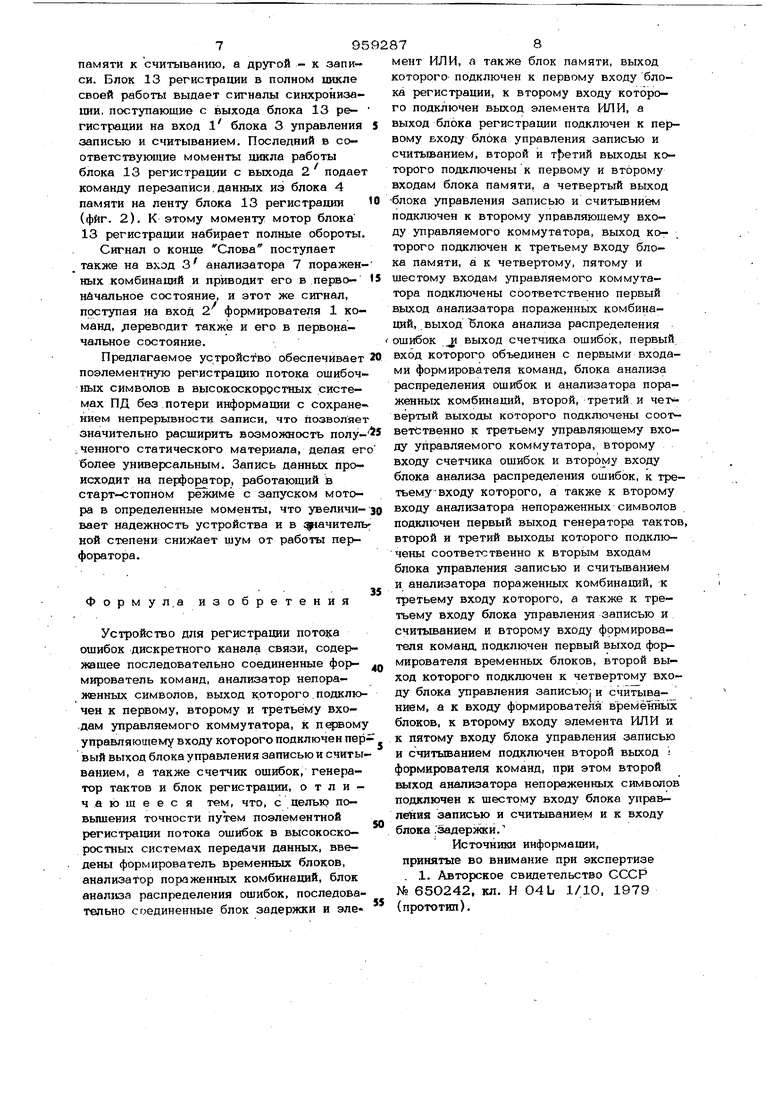

Цель достигается тем, что в устройство для регистрапии потока ошибок дискретного канала связи, содержащее последовательно соединенные формирователькоманд, анализатор непораженных символов, выход которого подключен к первому, второму и третьему входам управляемого коммутатора, к первому управляющему входу которого подключен первый выход блока управления записью: и считьюанием, а также счетчик ошибок, генератор тактов и блок регистрации, введены формирователь временных блоков, анализатор пораженных комбинаций, блок анализа распр1Ыделения ошибок, последовательно соеди15ненные блок задержки и элемент ИЛИ, а также блок памяти, выход которого подключен к первому входу блока регистрации, к второму входу которого подключен выход элемента ИЛИ, а выход блока регистрации подключен к первому входу блока управления записью и считыванием, второй.и третий выходы которого подключены к первому и второму входам блока памяти, а четвертый выход блока управления записью и считьтанием подключен к второму управлаяощему входу управляемого коммутатора, выход которо го подключен к третьему входу блока памяти, а к четвертому, пятому и шестому входам управляемого коммутатора подключены соответственно первый выход анализатора пораженных комбинаций, выход блока анализа распределения ошибок и выход счетчика ошибок, первый вход которого объединен с первыми входами. Формирователя команд, блока анализа распределения ошибок и анализатора пЬраженных комбинаций, второй, третий и четвертый выходы которого подключены соответственно к третьему управляющему входу управляемого коммутатора, вторюм входу счетчика ошибок и второму входу блока анализа распределения ошибок, к третьему входу которого, а также к второму входу анализатора непораженйых символов подключен первый выход генератора тактов, второй и третий выходы к торого подключены соответственно к вторым входам блока управления записью и считьшанием и анализатора пораженных комбинаций, к третьему входу которого, а также к третьему входу блока управления записью и считыванием и втсфому входу формирователя команд. подключен первый вь1ход формирователя временных блоков, второй выход которого подключен к четвертому входу блока управления записью и считыванием, а к.вхОду формиро вателя временных блоков, к второму входу элемента ИЛИ и к пятому входу блока управления записью и считъгаанием подключен второй выход формирователя команд, при этом второй выход анализатора непораженных символов подключен к шестому входу блока управления записью и считыванием и К входу блока задержки. На фиг. 1.представлена структурная схема устройства; на фиг. 2 - форма регистрации потока ошибок на перфоленте. Устройство для регистрации потока ошибок дискретного канала связи содержит формирователь 1 команд, анализатор 2 непораженных символов, блок 3 управления записью и считыванием, блок 4 памяти, формирователь 5 временных бло ков, генератор 6 тактов, анализатор 7 пораженных комбинаций, управляемый коммутатор 8, счетчик ошибок, блок 10анализа распределения ошибок, блок 11задержки, элемент ИЛИ 12, блок 13 регистрации. Устройство работ;ает следующим образом, При отсутствии ошибок в канале связи анализатор 2 непораженных символов, состоящий из трех счетчиков и блока 3 управления записью непораженных символов, подсчитывает количество тактов, идущих со скоростью, соответствующей 9,6 кбит/с. Такты подаются с первого выхода генератора 6 тактов. При полном заполнений: счетчиков анализатора 2 непораженных символов (12Ож120х120) с его выхода 2 подается команда через блок 11 задержки, и элемент ИЛИ 12, запускающий блок 13 регистрации (мотор перфоратора). Задержка, равная 8ОО мс, необходима для полного разгона мотора перфоратора. Команда с выхода 2 анализатора 2 непораженных символов поступает также на вход б блока 3 управления записью и считыванием, с третьего выхода которого подается сигнал подготавливающий блок. 4 памяти к записи. Блок 4 памяти состоит из 1603У (два подблока по 8ОЗУ), двух счетчиков управления адресами и коммутатора управления режимами ОЗУ. Режимов ОЗУ три: хранения, записи, считьюания. Блок 4 па мяти работает таким образом, что на один 8ОЗУ идет запись, с другого ВОЗУ идет считьюание. Одновременно с подачей сигнала в блок 4 памяти, с выхода 1- блока 3 управления записью и считыванием подается сигнал на управляющий вход 3коммутатора 8, который подключает l, 2 И 3 информационные входы управляемого коммутатора к информационному выходу 1 анализатора 2 непораженных символов, и затем дальше через коммутатор 8, состоящий из восьми разрядов, непораженные символы записываются в блок 4 памяти. Информация о безошибочно принятых символах в определенные моменты пере- записывается на перфоленту {фиг, 2а). На перфоленте пробиваются три ряда по пять отверстий: четыре строки несут информашпо, старший (пятый) разряд - маркировочный. В момент появления ошибки сигнал Ошибка поступает на первые входы фор мирователя1 команд, анализатора 7 пораженных комбинаций, блока 10 анализа распределения ошибок и йа счетчик 9 ошибок.. Формирователь 1 команд дает с выхо да l команду запрета подсчета таквов на анализатор 2 непораженных символов. С выхода 2 запуска формирователя 1 ко манд подается команда запуска формирователя 5 временных блоков, формирующег Слово длиной в 1 Кбайт, и Слово длиною в 32 байта, с этого же выхода через элемент ИЛИ 12 подается команда запус ка мотора блока 13 регистрации (перфо р атора), а такзке эта команда поступает на вход Б блока 3 управления записью и считыванием. С выхода 3 блока 3 управления записью и считьюанием подается сигнал на вход 2 блока 4 памяти, который подготавливает один подблок блока 4 памяти к записи, другой к считыванию. С второго выхода генератора 6 тактов на вход 2 блока 3 управления записью считыванием поступают такты соскоросты соответствующие скорости 72 с вы хода 4 блока 3 управления записью и считыванием поступает сигнал на управляющий вход 2 управляемого коммутато ра 8, по которому со всех восьми разрядов управляемого коммутатора 8 Единила со входа 7 коммутатора поступает в 3 адрес блока 4 памяти, что соответствует трем строкам пробивки перфоленты (фиг. Данная. окраска характе ризует приход оши ки. С этой же скоростью производится запись количества непораженных символов до прихода ошибки с выхода анализатора 2 Непораженных символов на l, 2 и з входы управляемого коммутатора 8 Данные о количестве безошибочно принятых символов поступают в следующие три адреса блока 4 памяти (фиг. 2-в ). Запись в первые шесть адресоа блока памяти происходит за время, меньше .времени следования двух тактов (72 кбит/с 9,6 кбит/с), за счет чего не происходит потеря информации. По приходу ошибки начинает работать анализатор 7 пораженных комбинаций, состоящий из двух счётчиков и блока Запрета, и блок 1О анализа распределения ошибок. На входе 2 анализатора 7 пораженных комбинаций с выхода 3 генератора 6 тактов поступают такты с частотой следования 9600 бит/с;8 за счет чего анализа-тором 7 пораженньрс комбинаций формируются байты (1 байт 8 бит). Анализатор 7 пораженньк комбинаций анализирует сформированные байты, и на выходе 1 анализатора 7 пораженных комбинаций появляется .информация о номере пораженного байта. Блок 10 анализа распределения ошибок представля ет собой регистр. Частота, соответствую- щая 9,6 кбит/с, приходящая с выхода J/ генератора 6 тшстов на вход 3 блока Ю анализа распределения ошибок, необходима для продвижения регистра. На выходе б;юн;а 1О появляется распределетше ошибок в пораженном байте поэлементно. Входы 4 и 5 управляемого коммутатора 8 по очередно подключаются соответственно к выходу 1 анализатора 7 пораженных комбинаций и к выходу блока 1О анализа распределения ошибок. Данные о номере пораженного байта и его раснределеиии записываются через коммутатор 8 в блок 4 памяти, что соответствует распечатке (фиг, 21), За счет того, что анализатор 7 выдает номер только поралоэнного байта и анализируется посимвольно тольiKO пораженный байт, происходит сзкатие Ид1форма10ги. Анализатор 7 пораженных комбинаций (юмимо выдачи номера пораженного байта юдсчйтьпзает также количество пораженяых байт. Если количество пораженных байт больше 15, т. е. достоверность передачи хуже IQ , тоС ьыхода 4 анализатора 7 пораженных комбинаций поступает команда Запрет на вход 2 блока 10 (распределения ошибок) и подается коман да Разрешение с выхода 3 анализатора 7 пораженных комбинашй на вход 2 счетчика 9 ошибок. Счетчик 9 ошибок начинает подсчет количества ошибок в блоке дпппою в 32 байта по приходу первой ошибки, а ка выходе этого блока информашш появляется по команде Разрешение с анализатора 7 пораженных комбинахшй. С выхода 2 анализатора 7 пораженных . комбкпааяй поступает команда на управляющий, вход 3управляемого коммутатора 8, по которой вход 6 коммутатора 8 подключается к выходу счетчи1са 9 ошибок, С1$гнал о конце блока длиною в 32 байта- с выхода 2 формирователя 5 через блок 3 управления записью и считьшанием приходит на управляю.шлй вход 2 коммутатора 8, по которому данные о количестч ве ошибок в блоке длиною в 32 байта поступают в блок 4 памяти, что соответст вуёт распечатке (фиг. 25). Запись количества ошибок в блоках длиною в 32 байта продолжается до конпй Слова дл1гаою в 1 кбайт. Сигнал о конце Слова длиною в 1 кбайт с вькода 1 формирователя 5 блоков поступает HS вход 5 блока 3 управления записью н считыванием. По этому сигналу с выхода 2 блока управления записью и считьгоа- нием -в блок 4 памяти поступает комагада, подготавл5юающая один подблок блока 4 памяти к считыванию, а другой - к записи. Блок 13 регистрации в полном цикле своей работы выдает сигналы синхронизации, поступающие с выхода блока 13 ре- гистрации на вход 1 блока 3 управления записью и считыванием. Последний в соответствующие моменты цикла работы блока 13 регистрации с выхода 2 подае команду перезаписи.данных из блока 4 памяти на ленту блока 13 регистрации (фиг. 2). К этому моменту мотор блока 13 регистрации набирает полные обороты Сигнал о конце Слова поступает также на вход З анализатора 7 поражен ных комбинаций и приводит его в перво- нйчальное состояние, и этот же сигнал, поступая на вход 2 формирователя 1 команд, Д1ереводит также и его в первоначальное состояние. Предлагаемое устройство обеспечивает поэлементную регистрацию потока ошибоч ных символов в высокоскоростных системах ПД без потери информации с сохране нием непрерывности записи, что позволяе значительно расширить возможность полуученного статического материала, делая ег более универсальным. Запись данных происходит на перфоратор, работающий в старт-стопном режиме с запуском мотора в определенные моменты, что увеличи- вает надежность устройства и в {ачитель ной степени снижает шум от работы пер- форштора. Форму л.а изобретения Устройство для регистрации потока ошибок дискретного канала связи, содержащее последовательно соединенные формирователь команд, анализатор непораженных символов, выход которого.подключен к первому, второму и третьему вхо.дам управляемого коммутатора, к первому управляющему входу которого подключен пер вый выход блока управления записью и считы ванием, а также счетчик ошибок, генератор тактов и блок регистрации, отличающееся тем, что, с целью повышения точности путем поэлементной регистра1ши потока ошибок в высокоскоростных системах передачи данных, введены формирователь временных блоков, анализатор пораженных комбинаций, блок анализа распределения ошибок, последовательно соединенные блок задержки и эле« мент ИЛИ, а также блок памяти, выход которого подключен к первому входу блока регистрации, к второму входу которого подключен выход элемента ИЛИ, а выход блока регистрации подключен к первому входу блЬка управления записью и считьюанием, второй и т)етий выходы которого подключены к первому и второму входам блока памяти, а четвертый выход блока управления записью и считывнием подключен к второму управляющему входу управляемого коммутатора, выход которого подключен к третьему входу блока памяти, а к четвертому, пятому и шестому входам управляемого коммутатора подключены соответственно первый выход анализатора пораженных комбинаций, выход Блока анализа распределения ошибок JI выход счетчика ошибок, первый вход которого объединен с первыми входами формирователя команд, блока анализа распределения ошибок и анализатора пораженных комбинаций, второй, третий и чет вертый выходы которого подключены соответственно к третьему управляющему входу управляемого коммутатора, второму входу счетчика ошибок и второму входу блока анализа распределения ошибок, к третьему входу которого, а также к второму входу анализатора непораженных символов подключен первый выход генератора тактов, второй и третий выходы которого подключены соответственно к вторым входам блока управления записью и считьшанием и анализатора пораженных комбинаций, к третьему входу которого, а также к третьему входу блока управления записью и считъюанием и второму входу формирователя команд, подключен первый выход формирователя временных блоков, второй выход которого подключен к четвертому входу блока управления записью; и считьшанием, а к входу формирователя временных блоков, к второму входу элемента ИЛИ и к пятому входу блока управления записью и считьшанием подключен второй выход формирователя команд, при этом второй выход анализатора непораженных символов подключен к шестому входу блока управления записью и считыванием и к входу блока .задеряжи. Источники информа1ши, принятые во внимание при экспертизе . 1. .Авторское свидетельство СССР № 650242, кл. Н 04Ь 1/10, 1979 (прототип).

4e,/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Сигнатурный анализатор | 1989 |

|

SU1714602A1 |

| Устройство телеконтроля линейных трактов цифровых систем передачи | 1985 |

|

SU1241494A1 |

| Устройство для реализации подстановок слов | 1989 |

|

SU1635192A1 |

| Устройство для приема трехкратно повторяемых команд управления | 1979 |

|

SU873436A1 |

Авторы

Даты

1982-09-15—Публикация

1981-02-09—Подача